### **MAX42410**

### **General Description**

The MAX42408/MAX42410 are highly-integrated synchronous buck converters with internal high-side and low-side switches. The ICs deliver up to 8A/10A with input voltage from 4.5V to 36V. The voltage quality can be monitored by the PGOOD signal. The MAX42408/MAX42410 can operate in the dropout mode by running at very high duty cycle, which make them ideal for industrial applications.

The MAX42408/MAX42410 offer programmable outputvoltage options. High switching frequency at 1.5MHz and 400kHz options allow for small external components and reduced output ripple. SYNC input programmability enables three modes for optimized performance: forced PWM mode, skip mode with ultra-low quiescent current, and synchronization to an external clock.

The MAX42408/MAX42410 also come with dual-phase capability, which allows up to 20A designs. Two ICs can be configured as a controller and target with dynamic current sharing and 180° out-of-phase operation.

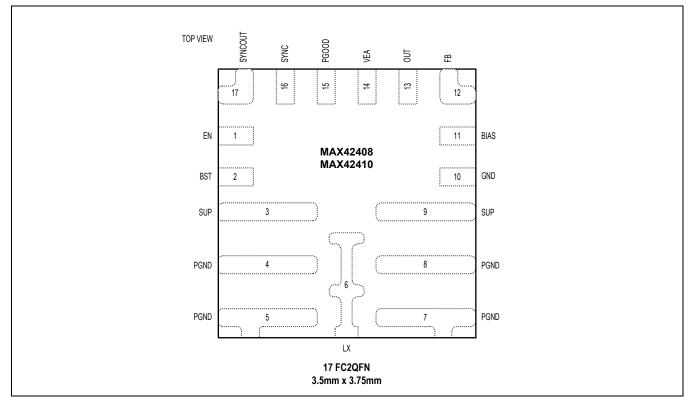

The MAX42408/MAX42410 are available in a small 3.5mm x 3.75mm, 17-pin FC2QFN package. They are pin-to-pin compatible with the MAX42405/MAX42406 (5A to 6A) family of products.

### **Applications**

- Point-of-Load

- Industrial Automation

- Distributed DC Power Systems

### **Benefits and Features**

- High-Power DC/DC Converter in Small Solution Size

- Operating V<sub>IN</sub> range of 4.5V to 36V

- Synchronous DC-DC Converter with Integrated FETs

- 8A/10A Maximum Output Current

- 400kHz and 1.5MHz Fixed Frequency Options

- Fixed Soft-Start Time

- 2.5ms for 400kHz

- 3.5ms for 1.5MHz

- 36ns Minimum On-Time

- · Programmable Output Voltage

- 0.8V to 10V for 400kHz

- 0.8V to 6V for 1.5MHz

- Symmetric and Balanced SUP and PGND Pinout Placement for Better EMI Performance

- Thermally-Enhanced 3.5mm x 3.75mm, 17-Pin FC2QFN Package

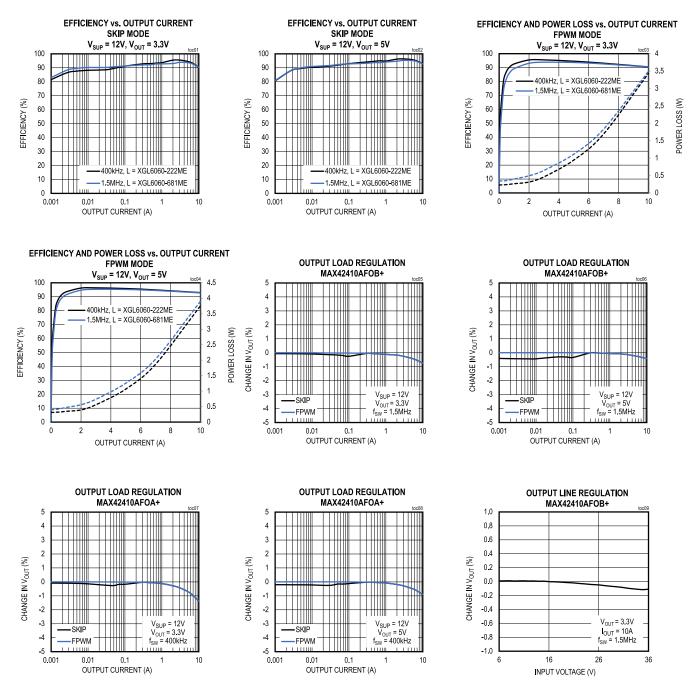

- High Efficiency at All Load Ranges

- 20µA Quiescent Current in Skip Mode

- Up to 95.6% Eff. at 12V<sub>IN</sub>/3.3V<sub>OUT</sub>/400kHz

- Up to 93.9% Eff. at 12V<sub>IN</sub>/3.3V<sub>OUT</sub>/1.5MHz

- Dual-Phase Operation up to 20A Load Capability

- Frequency Synchronization Input/Output

- 180° Out-of-Phase Between Controller and Target

- Dynamic Current Sharing

- Forced PWM and Skip-Mode Operation

- Low Dropout Operation

- Power Good Indicator

- Overtemperature and Short-Circuit Protection

- -40°C to +125°C Temperature Range

- Scalable Power Solution

- Footprint Compatible with MAX42405/MAX42406

Ordering Information appears at end of data sheet.

#### www.datasheetall.com

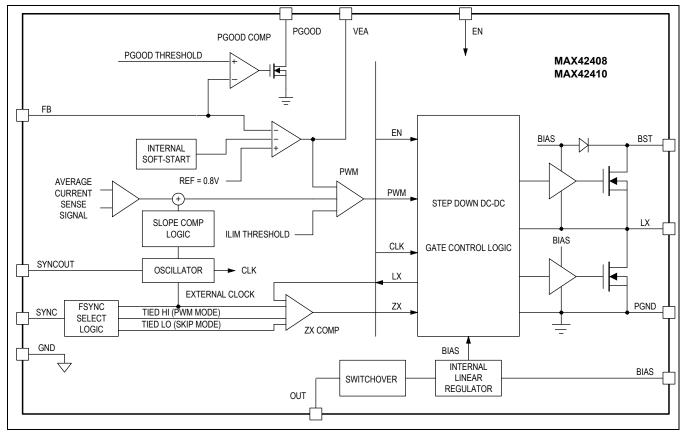

## Simplified Block Diagram

## 36V, 10A Fully Integrated Buck Converter with 10µA Quiescent Current and Dual-Phase Capability

### **Absolute Maximum Ratings**

| SUP, EN to PGND             | 0.3V to +42V        |

|-----------------------------|---------------------|

| BST to LX                   | -0.3V to +2.2V      |

| BST to BIAS                 | -0.3V to 42V        |

| BST to PGND                 | 0.3V to +44V        |

| LX to PGND                  | 0.3V to SUP + 0.3V  |

| SYNC, SYNCOUT, PGOOD to GND | 0.3V to 6V          |

| FB, VEA to GND              | 0.3V to BIAS + 0.3V |

| OUT to GND                  | 0.3V to 16V         |

| PGND to GND                 | -0.3V to 0.3V       |

| BIAS to GND0.3V to +2.2V                                                             | / |

|--------------------------------------------------------------------------------------|---|

| LX Continuous RMS Current10A                                                         | ٩ |

| SUP Continuous RMS Current5A                                                         | ٩ |

| ESD Protection Human Body Model±2k                                                   | / |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C, derate 37mW/°C<br>above +70°C) |   |

| Operating Junction Temperature40°C to +150°C                                         | ) |

| Storage Temperature Range65°C to +150°C                                              | ) |

| Lead Temperature (Soldering 10s)+300°C                                               | ) |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

| Package Code                                                   | F173A3F+1F       |  |  |  |  |

|----------------------------------------------------------------|------------------|--|--|--|--|

| Outline Number                                                 | <u>21-100699</u> |  |  |  |  |

| Land Pattern Number                                            | <u>90-100239</u> |  |  |  |  |

| THERMAL RESISTANCE, JEDEC BOARD                                |                  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                         | 38.6°C/W         |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )          | 7.7°C/W          |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER EVALUATION KIT (EV KIT) BOARD   |                  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                         | 27°C/W           |  |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) 8.5°C/W |                  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>https://www.analog.com/en/design-center/packaging-quality-symbols-footprints/package-index.html</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>https://www.analog.com/en/technical-</u> <u>articles/thermal-characterization-of-ic-packages.html</u>.

## **Electrical Characteristics**

$(V_{SUP} = V_{EN} = 14V, T_J = -40^{\circ}C$  to +150°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$  under normal conditions, unless otherwise noted (*Note 1*, *Note 2*).)

| PARAMETER                                              | SYMBOL                         | COND                                                                  | ITIONS                                                                 | MIN   | TYP     | MAX   | UNITS |

|--------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-------|---------|-------|-------|

| Supply Voltage Range                                   | V <sub>SUP</sub>               |                                                                       |                                                                        | 4.5   |         | 36    | V     |

|                                                        | I <sub>SUP_SHDN</sub>          | V <sub>EN</sub> = 0, T <sub>A</sub> = +25°C                           |                                                                        |       | 4       | 6     |       |

| Supply Current                                         |                                | V <sub>EN</sub> = high, V <sub>OUT</sub> = switching                  | V <sub>EN</sub> = high, V <sub>OUT</sub> = 3.3V, no load,<br>switching |       | 20      |       | μA    |

| SUP Undervoltage                                       |                                | Rising                                                                |                                                                        | 2.9   | 3.0     | 3.2   | Ň     |

| Lockout                                                |                                | Falling                                                               |                                                                        | 2.6   | 2.7     | 2.9   | V     |

| BIAS Voltage                                           |                                | $+2.5 V \leq V_{SUP} \leq +36$                                        | V                                                                      |       | 1.8     |       | V     |

| BIAS Undervoltage                                      | V <sub>BIAS_UVLO</sub>         | Rising                                                                |                                                                        | 1.58  | 1.63    | 1.68  | V     |

| Lockout                                                | V <sub>BIAS_UVLO_</sub><br>HYS | Hysteresis                                                            |                                                                        |       | 50      |       | mV    |

| BUCK CONVERTER                                         |                                |                                                                       |                                                                        | -     |         |       |       |

| Adjustable Output-                                     |                                | f <sub>sw</sub> = 1.5MHz                                              |                                                                        | 0.8   |         | 6     | V     |

| Voltage Range                                          |                                | $f_{sw} = 400 kHz$                                                    |                                                                        | 0.8   |         | 10    |       |

| FB Voltage Accuracy                                    | V <sub>FB_PWM</sub>            | PWM mode, no load                                                     |                                                                        |       | 0.800   | 0.812 | V     |

| FB Leakage Current                                     | I <sub>FB</sub>                | V <sub>FB</sub> = 0.8V, T <sub>A</sub> = +2                           | 5°C                                                                    |       |         | 100   | nA    |

| High-Side Switch On<br>Resistance                      | R <sub>DSON_HS</sub>           | V <sub>BIAS</sub> = 1.8V, I <sub>LX</sub> = 5                         | 5A                                                                     |       | 26      | 53    | mΩ    |

| Low-Side Switch On<br>Resistance                       | R <sub>DSON_LS</sub>           | V <sub>BIAS</sub> = 1.8V, I <sub>LX</sub> = 5A                        |                                                                        |       | 13      | 26    | mΩ    |

| High-Side Switch                                       | I <sub>LIM</sub>               | MAX42408                                                              |                                                                        | 10    | 12      | 14    | А     |

| Current-Limit Threshold                                | 'LIM                           | MAX42410                                                              |                                                                        | 11.9  | 11.9 14 | 16    | A     |

| Low-Side Switch<br>Negative Current-Limit<br>Threshold | I <sub>NEG</sub>               |                                                                       |                                                                        |       | -4      |       | A     |

| LX Leakage Current                                     | I <sub>LX_LKG</sub>            | $V_{SUP} = 36V, V_{LX} = 0V \text{ or } V_{LX} = 36V, T_A$<br>= +25°C |                                                                        | -5    |         | 5     | μA    |

|                                                        | t <sub>SS</sub>                | f <sub>sw</sub> = 1.5MHz                                              |                                                                        |       | 3.5     |       |       |

| Soft-Start Ramp Time                                   |                                | f <sub>sw</sub> = 400kHz                                              |                                                                        |       | 2.5     |       | ms    |

| Minimum On-Time                                        | T <sub>ON</sub>                | <u>Note 3</u>                                                         |                                                                        |       | 36      | 65    | ns    |

| Maximum Duty Cycle                                     |                                | Dropout mode                                                          |                                                                        | 96    |         |       | %     |

| SWITCHING FREQUEN                                      | CY                             |                                                                       |                                                                        |       |         |       |       |

| PWM Switching                                          | form                           | f <sub>SW</sub> = 1.5MHz                                              |                                                                        | 1.375 | 1.500   | 1.625 | MHz   |

| Frequency                                              | fsw                            | f <sub>SW</sub> = 400kHz                                              |                                                                        | 360   | 400     | 440   | kHz   |

| SYNC External Clock                                    | farme                          | f <sub>SW</sub> = 1.5MHz                                              |                                                                        | 1.215 |         | 1.845 | MHz   |

| Frequency $f_{SYNC} = 400 \text{kHz}$                  |                                |                                                                       | 360                                                                    |       | 600     | kHz   |       |

| PGOOD OUTPUT                                           | -                              | ·                                                                     |                                                                        |       |         |       |       |

|                                                        | V <sub>PGOOD_R</sub>           | Percentage of V <sub>OUT</sub> , rising                               |                                                                        | 92    | 94      | 96    | 0/    |

| PGOOD Threshold                                        | V <sub>GOOD_F</sub>            | Percentage of V <sub>OUT</sub>                                        | , falling                                                              | 91    | 93      | 95    | %     |

|                                                        |                                | f <sub>SW</sub> = 1.5MHz                                              |                                                                        |       | 70      |       | μs    |

| PGOOD Debounce                                         | T <sub>DEB</sub>               | PWM mode, falling                                                     | f <sub>SW</sub> = 400kHz                                               |       | 50      |       |       |

|                                                        |                                | PWM mode, rising f <sub>SW</sub> = 1.5MHz                             |                                                                        |       | 140     |       | μs    |

| PARAMETER                        | SYMBOL                 | CONDITIONS                                |                           | MIN | TYP | MAX | UNITS |

|----------------------------------|------------------------|-------------------------------------------|---------------------------|-----|-----|-----|-------|

|                                  |                        |                                           | $f_{SW} = 400 \text{kHz}$ |     | 100 |     |       |

| PGOOD High-Leakage<br>Current    | IPGOOD_LKG             | T <sub>A</sub> = +25°C                    |                           |     |     | 1   | μA    |

| PGOOD Low-Voltage<br>Level       | V <sub>PGOOD_LOW</sub> | Sinking 1mA                               |                           |     |     | 0.4 | V     |

| LOGIC LEVELS                     |                        |                                           |                           |     |     |     |       |

| EN High-Voltage Level            | V <sub>EN_HIGH</sub>   |                                           |                           | 1.2 |     |     | V     |

| EN Low-Voltage Level             | V <sub>EN_LOW</sub>    |                                           |                           |     |     | 0.5 | V     |

| EN Input Current                 | I <sub>EN</sub>        | V <sub>EN</sub> = V <sub>SUP</sub> = 36V, | T <sub>A</sub> = +25°C    |     |     | 1   | μA    |

| SYNC High-Voltage<br>Level       | V <sub>SYNC_HIGH</sub> |                                           |                           | 1.4 |     |     | V     |

| SYNC Low-Voltage<br>Level        | V <sub>SYNC_LOW</sub>  |                                           |                           |     |     | 0.4 | V     |

| SYNC Input Current               | I <sub>IN,SYNC</sub>   | T <sub>A</sub> = +25°C                    |                           |     |     | 1   | μA    |

| SYNCOUT Output-<br>Voltage Level | V <sub>SYNCOUT</sub>   | No load                                   |                           | 2.6 | 3.3 | 3.9 | V     |

| THERMAL PROTECTION               | N                      |                                           |                           |     |     |     |       |

| Thermal Shutdown                 | T <sub>SHDN</sub>      |                                           |                           |     | 175 |     | °C    |

| Thermal Shutdown<br>Hysteresis   | T <sub>SHDN_HYS</sub>  |                                           |                           |     | 20  |     | °C    |

| (V <sub>SUP</sub> = V <sub>EN</sub> = 14V, T <sub>J</sub> = -40°C to +150°C, unless otherwise noted. Typical values are at T <sub>A</sub> = +25°C under normal conditions, unles | s |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| otherwise noted ( <u>Note 1, Note 2</u> ).)                                                                                                                                      |   |

**Note 1:** All units are 100% production tested at +25°C. All temperature limits are guaranteed by design and characterization.

**Note 2:** The device is designed for continuous operation up to  $T_J = +125^{\circ}C$  for 95,000 hours and  $T_J = +150^{\circ}C$  for 5,000 hours.

**Note 3:** Guaranteed by design, not production tested.

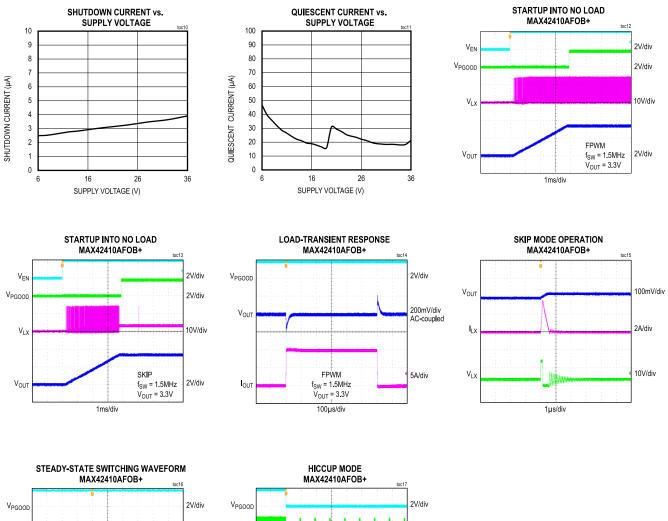

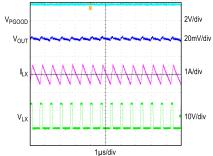

# **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, unless otherwise noted.)$

## 36V, 10A Fully Integrated Buck Converter with 10µA Quiescent Current and Dual-Phase Capability

$(T_A = +25^{\circ}C, unless otherwise noted.)$

# **Pin Configurations**

### MAX42408/MAX42410

## **Pin Descriptions**

| PIN  | NAME  | FUNCTION                                                                                                                                                                                         |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | EN    | High-Voltage Compatible Enable Input. Drive EN high to enable the buck converter.                                                                                                                |

| 2    | BST   | High-Side Gate Driver Supply. Connect a 0.1µF ceramic capacitor between BST and LX.                                                                                                              |

| 3    | SUP   | IC Supply Input and Internal High-Side Switch Supply Input. Bypass SUP to PGND with $0.1\mu$ F and $4.7\mu$ F ceramic capacitors as close as possible. Both SUP pins are internally connected.   |

| 4, 5 | PGND  | Power Ground. Connect all PGND pins together.                                                                                                                                                    |

| 6    | LX    | Buck Inductor Connection. Connect an inductor from LX to the buck output. LX is high impedance when the IC is disabled.                                                                          |

| 7, 8 | PGND  | Power Ground. Connect all PGND pins together.                                                                                                                                                    |

| 9    | SUP   | IC Supply Input and Internal High-Side Switch Supply Input. Bypass SUP to PGND with 0.1µF and 4.7µF ceramic capacitors as close as possible. Both SUP pins are internally connected.             |

| 10   | GND   | Analog Ground. Connect GND and PGND through start connection to the PCB ground plane.                                                                                                            |

| 11   | BIAS  | 1.8V Internal Linear Regulator Output. Connect BIAS to ground with a minimum of 2.2µF ceramic capacitor.                                                                                         |

| 12   | FB    | Feedback Input. Connect FB to a resistor-divider between OUT and GND to adjust the output voltage between 0.8V and 10V.                                                                          |

| 13   | OUT   | Output Voltage Sense Input. The buck converter uses OUT to sense output voltage.                                                                                                                 |

| 14   | VEA   | Internal Voltage Loop Error Amplifier Output. Connect VEA of the controller and target together in dual-<br>phase operation. Leave VEA open for single-phase operation.                          |

| 15   | PGOOD | Open-Drain Power Good Output. The PGOOD is low if the buck output voltage falls below 93% (typ) of regulation voltage. The PGOOD becomes high impedance when the buck output voltage rises above |

|    |         | 94% (typ) of its regulation voltage. The PGOOD asserts low during soft-start. Connect PGOOD to BIAS or a positive voltage lower than 5.5V with a pull-up resistor to indicate buck output status.                         |

|----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 | SYNC    | External Clock Synchronization Input. Connect SYNC low to enable skip-mode operation. Connect SYNC high for forced PWM operation. Connect a valid external clock signal to SYNC to enable external clock synchronization. |

| 17 | SYNCOUT | 180° Out-of-Phase Clock Output. In dual-phase operation, connect SYNCOUT to BIAS to configure the IC as a target, and connect SYNCOUT of the controller to SYNC of the target. Leave SYNC open in single-phase operation. |

### **Detailed Description**

The MAX42408/MAX42410 are small, synchronous buck converters with integrated high-side and low-side switches. The ICs are designed to deliver up to 8A/10A current with input voltages from 4.5V to 36V while using only 20µA quiescent current at no load condition. Voltage quality can be monitored by the PGOOD signal. The ICs can operate in dropout by running at a very high duty cycle, which makes them ideal for industrial applications.

The MAX42408/MAX42410 offer adjustable output voltage programmed by an external resistor-divider. Frequency is internally fixed with 1.5MHz and 400kHz options, which allow for small external components and reduced output ripple. The signal at SYNC programs the ICs in skip enable, forced pulse-width modulation (FPWM), or when synchronizing to the external clock. Average current-mode control with 36ns minimum ON time allows for large input/output step-down ratios without skipping cycles.

The MAX42408/MAX42410 can also be configured in dual-phase to supply up to 20A load. The average current-mode control provides noise immunity and accurate dynamic current sharing during transients.

The FC2QFN package lowers the package parasitic impedance and improves the thermal performance. Symmetrical pinout placement of SUP and PGND provides balanced current loop around the ICs and further improves their EMI performance.

#### Linear Regulator Output (BIAS)

The devices include a 1.8V linear regulator ( $V_{BIAS}$ ) that provide power to the internal circuit blocks. Connect a 2.2µF ceramic capacitor from BIAS to GND. During startup, the bias regulator draws power from the input and switches over to the output after the startup is completed (if  $V_{OUT} > 2.5V$ ).

#### Synchronization Input (SYNC)

The MAX42408/MAX42410 provide an internal oscillator with 400kHz and 1.5MHz options. Drive SYNC high for FPWM operation with 400kHz or 1.5MHz switching frequency. Drive SYNC low to enable skip-mode for better efficiency improvement at light load. The ICs can be synchronized to the external clock with a valid external clock present at SYNC.

#### Enable Input (EN)

An Enable Input (EN) enables the ICs from shutdown mode. Drive EN high to enable the ICs. Drive EN low to disable the ICs into shutdown mode. The quiescent current is reduced to 4µA (typ) during shutdown.

#### Soft-Start

Drive EN high to enable the ICs. The soft-start circuitry gradually ramps up the reference voltage during soft-start time (2.5ms at 400kHz or 3.5ms at 1.5MHz, typ) to reduce the input inrush currents during startup.

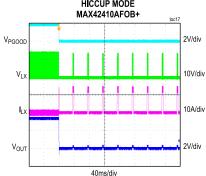

#### **Short-Circuit Protection**

The ICs feature a cycle-by-cycle current limit and hiccup-mode to protect against short-circuit or overload condition. In overload conditions, the high-side FET remains on until the inductor current reaches the current limit threshold,  $I_{LIM}$ . Then the converter turns off the high-side FET and turns on the low-side FET to allow the inductor current to ramp down. Once the inductor current decreases to the valley current limit, the converter turns on the high-side FET again. This cycle repeats until the overload condition is removed.

A short-circuit is detected when the output voltage falls below the preset threshold voltage while the inductor current hits the current limit. The threshold voltage is 25% of output regulation voltage. During hiccup-mode, the ICs turn off the buck converter for 35ms (10x soft-start time,  $f_{SW}$  = 1.5MHz), and then restart it if the overcurrent or short-circuit condition is removed. The hiccup repeats when the short-circuit is continuously present.

#### **Power Good Indicator (PGOOD)**

The ICs feature an open-drain Power Good (PGOOD) output to indicate the output voltage status. The PGOOD goes low to high impedance when the converter output voltage rises above 94% (typ) of its nominal regulation voltage. The PGOOD goes low when the output voltage drops below 93% (typ) of the nominal regulation voltage. Connect PGOOD to the converter output or BIAS voltage through a pull-up resistor The PGOOD asserts low during soft-start.

#### **Thermal Shutdown Protection**

Thermal shutdown protection limits total power dissipation in the ICs. When the junction temperature exceeds +175°C, an internal sensor shuts down the ICs, which allows them to cool. The thermal sensor turns on the ICs again after the junction temperature cools by 20°C.

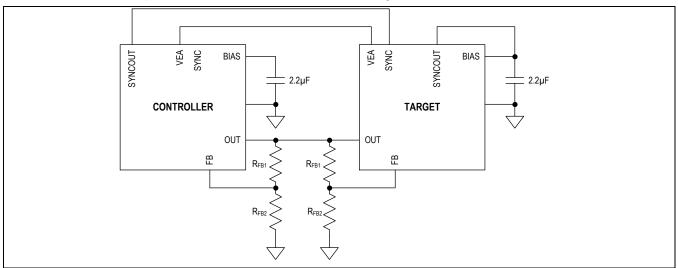

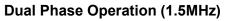

#### **Dual-Phase Operation**

Two MAX42408/MAX42410s can be configured in dual-phase to provide higher output current up to 20A. To operate in dual-phase, one IC is programmed as a target by connecting its SYNCOUT to BIAS, and the other IC is treated as a controller. The SYNCOUT of the controller is connected to the SYNC of the target to have both ICs switch in 180° out-of-phase. Therefore, with present SYNCOUT signal from the controller, FPWM is recommended for dual-phase operation.

The VEA nodes of the controller and target are connected together to ensure balanced current sharing between two phases. Also, by doing this, the controller's voltage control loop is shared with the target. Instead of connecting FB nodes together, use separate resistor-dividers for each phase.

To set the output voltage to value, connect a resistor-divider between the buck output, FB, and GND as shown in *Figure* <u>1</u>. Use an identical but separate resistor-divider for controller and target.

Figure 1. Typical Application Circuit for Dual-Phase Configuration with External Resistor-Divider

#### Low-IQ Operation in Dual-Phase

The MAX42408/MAX42410 come with dual-phase capability, where each IC can be either configured as controller or target. The SYNCOUT pin of the controller outputs 180° out-of-phase clock when SYNC is tied high (FPWM mode). For low- $I_Q$  mode, pull the SYNC pin of the controller low (skip-mode). In this mode, there is no clock present on the SYNCOUT pin of the controller IC enters the skip-mode. The internal circuit of the target IC remains ON during this time and actively looks for the SYNCOUT signal from the controller. As the target IC is ON, the quiescent current is slightly higher, even though both the ICs skip pulses.

To improve the light-load efficiency and further reduce the  $I_Q$ , pull the target EN low. This disables the target and its internal circuits, which further reduces the  $I_Q$ . <u>Table 1</u> summarizes the truth table for low- $I_Q$  operation.

| CONTROLLER             | TARGET    | MODE                                     |

|------------------------|-----------|------------------------------------------|

| EN = High, SYNC = BIAS | EN = High | FPWM (high I <sub>Q</sub> )              |

| EN = High, SYNC = Low  | EN = High | Skip-mode (low I <sub>Q</sub> )          |

| EN = High, SYNC = Low  | EN = Low  | Standby-mode (ultra-low I <sub>Q</sub> ) |

| EN = Low               | EN = High | Not allowed                              |

### Table 1. Configurations for Low-IQ Operation

### **Applications Information**

#### Setting the Output Voltage

To externally program the output voltage between 0.8V and 10V for 400kHz switching frequency, and between 0.8V and 6V for 1.5MHz switching frequency, connect a resistor-divider from the buck converter output to FB, and then to GND. Select  $R_{FB2}$  between FB and GND in <u>Typical Application Circuits</u> less than 20k $\Omega$ . Calculate  $R_{FB1}$  between buck output and FB with the following equation:

$$R_{FB1} = R_{FB2} \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

Where,  $V_{FB}$  = 0.8V, and  $R_{FB2}$  is less than 20 k $\Omega$ .

<u>Table 2</u> provides components selection recommendation for each output range (CFF is recommended based on  $R_{FB1} = 50 k\Omega$ ).

| SWITCHING FREQUENCY<br>(kHz) | V <sub>OUT</sub> (V) | INDUCTOR<br>(µH) | OUTPUT CAPACITOR (µF) | CFF (pF) |

|------------------------------|----------------------|------------------|-----------------------|----------|

| 400                          | 0.8 to 1.8           | 0.68             | 500                   | N/A      |

| 400                          | 1.8 to 3.3           | 1                | 220                   | N/A      |

| 400                          | 3.3 to 5             | 2.2              | 120                   | 82pF     |

| 400                          | 5 to 7               | 2.2              | 88                    | 56pF     |

| 400                          | 7 to 10              | 3.3              | 66                    | 47pF     |

| 1500                         | 0.8 to 1.8           | 0.38             | 88                    | N/A      |

| 1500                         | 1.8 to 3.3           | 0.47             | 88                    | N/A      |

| 1500                         | 3.3 to 5             | 0.68             | 66                    | 47pF     |

| 1500                         | 5 to 6               | 0.68             | 44                    | 15pF     |

### Table 2. Recommended Component Selection

#### Input Capacitor

The input capacitors reduce peak current drawn from the power source, and improve noise and voltage ripple on the SUP nodes caused by the buck converter switching cycles. Use two ceramic input capacitors with  $0.1\mu$ F and  $4.7\mu$ F capacitance in parallel at each side of the IC for proper buck operation.

Place a  $0.1\mu$ F ceramic capacitor with 0402 or 0603 size next to SUP and PGND at each side of the IC to reduce input noise and improve EMI performance. A  $4.7\mu$ F ceramic capacitor after  $0.1\mu$ F capacitor is required on each input side to reduce input voltage ripple. Additional buck capacitor might be required if high impedance exists in the input supply or traces.

The input capacitor RMS current requirement (I<sub>RMS</sub>) is defined by the following equation:

$$I_{\text{RMS}} = I_{\text{LOAD(MAX)}} \times \left( \frac{\sqrt{V_{\text{OUT}} \times (V_{\text{SUP}} - V_{\text{OUT}})}}{V_{\text{SUP}}} \right)$$

IRMS has a maximum value when the input voltage equals twice the output voltage:

$$V_{SUP}$$

= 2  $\times$   $V_{OUT}$

Therefore:

$$I_{\rm RMS} = \frac{I_{\rm LOAD(MAX)}}{2}$$

Choose an input capacitor that exhibits less than +10°C self-heating temperature rise at the RMS input current for optimal long-term reliability. The input-voltage ripple comprises  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the capacitor). Assume the contribution from the ESR and capacitor discharge equal to 50%. Calculate the input capacitance and ESR required for a specified input voltage ripple using the following equations:

36V, 10A Fully Integrated Buck Converter with 10µA Quiescent Current and Dual-Phase Capability

$$ESR_{IN} = \frac{\Delta V_{ESR}}{I_{LOAD(MAX)} + \frac{\Delta I_{L}}{2}}$$

$$C_{IN} = \frac{I_{LOAD(MAX)} \times D(1 - D)}{\Delta V_{Q} \times f_{SW}}$$

Where:

$$D = \frac{V_{OUT}}{V_{SUP}}$$

e maximum output current. Alu is peak-to-peak inductor current. four is switc

$\Delta I_{L} = \frac{(V_{SUP} - V_{OUT}) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$

and  $I_{LOAD(MAX)}$  is the maximum output current,  $\Delta I_L$  is peak-to-peak inductor current,  $f_{SW}$  is switching frequency, and D is the duty cycle.

#### Selecting the Inductor

Inductor selection is a compromise between component size, efficiency, control loop bandwidth, and loop stability. Insufficient inductance increases the inductor current ripple, conduction losses, and output voltage ripple, and causes loop instability in the worst case. A large inductor reduces the inductor current ripple by sacrificing component size and slow response. For recommended inductor values, see <u>Table 2</u>.

#### **Output Capacitor**

The output capacitor is a critical component for switching regulators. It is selected to meet output voltage ripple, load transient response, and loop stability requirements.

The output voltage ripple comprises  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the output capacitor). Use low ESR ceramic capacitors. Assume the contribution to the output ripple voltage from ESR and the capacitor discharge to be equal. Use the following equations to get the output capacitance and ESR for a specified output voltage ripple.

$$ESR = \frac{\Delta V_{ESR}}{\Delta I_{P,P}}$$

$$C_{OUT} = \frac{\Delta I_{P,P}}{8 \times \Delta V_Q \times f_{SW}}$$

$$\Delta I_{P,P} = \frac{(V_{SUP} - V_{OUT}) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$$

$$V_{OUTRIPPLE} = \Delta V_{ESR} + \Delta V_Q$$

Where,  $\Delta I_{P-P}$  is the peak-to-peak inductor current, and  $f_{SW}$  is the switching frequency.

During a load step, the output capacitors supply the load current before the converter loop responses with higher duty cycle, which causes output voltage undershoot. To keep the maximum output voltage deviations below the tolerable limits of the electronics being powered, calculate the output capacitance with the following equation:

$$C_{OUT} = \frac{\Delta I_{LOAD}}{\Delta V \times 2\pi \times f_{C}}$$

Where,  $\Delta I$  is the load step,  $\Delta V$  is the allowed output voltage undershoot, and  $f_c$  is the loop crossover frequency, which can be assumed to be the lesser of  $f_{SW}/10$  or 100kHz. The calculated  $C_{OUT}$  is the capacitance after considering capacitance tolerance, temperature effect, and voltage derating. <u>*Table 2*</u> shows the recommended values of output capacitance based on frequency and output voltage.

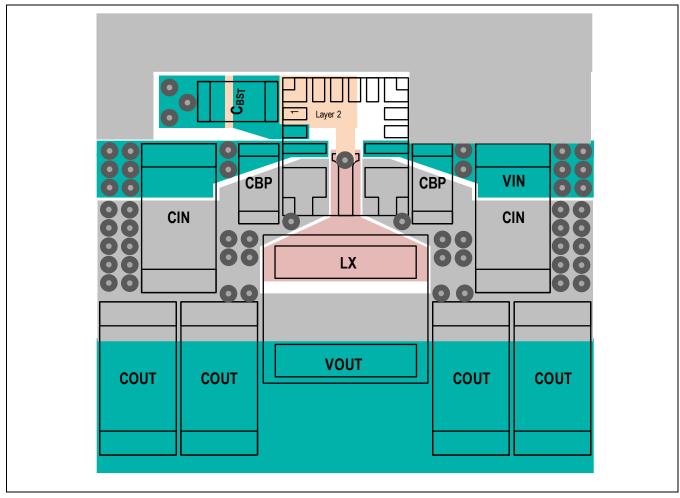

#### **PCB Layout Guidelines**

- 1. Careful PCB layout is critical to achieve low switching losses, low EMI, and clean, stable operation. For an example layout, see *Figure 2*.

- 2. Place the input bypass capacitors CBP and CIN as close as possible to each SUP and PGND on both sides of the IC. CBP should be placed right next to the SUP and PGND node on the same layer to provide best EMI rejection and minimize the input noise on SUP. The symmetrical CIN and CBP arrangements generate the SUP loops with opposite orientation to cancel the magnetic fields and help EMI mitigation.

- 3. Minimize the connection from the buck output capacitor's ground terminal to the input capacitor's ground terminal. Keep buck high-current path, and power traces wide and short. Minimize the traces from LX node to the inductor and then to the output capacitors. This minimizes the buck current loop area and minimizes LX trace resistance and stray capacitance to achieve optimal efficiency.

- Place the bootstrap capacitor CBST close to the IC. Use short and wide traces from BST and LX, and minimize this

routing parasitic impedance. High parasitic impedance from BST to LX impacts the switching speed, further increases

switching losses, and high dV/dt noise. For BST to LX routing, see <u>Figure 2</u>.

- 5. Place the BIAS capacitor as close to the BIAS node as possible. Noise coupling into BIAS can disturb the reference and bias circuitry if this capacitor is installed away from the IC.

- 6. Keep the sensitive analog signals (FB/VEA) away from noisy switching nodes (LX and BST) and high current loops.

- 7. Ground is the return path for the full-load currents flowing into and out of the IC. It is also the common reference voltage for all the analog circuits. Improper ground routing can bring extra resistance and inductance into the current loop, causing different voltage reference and worsening voltage ringing or spikes. Place a solid ground plane layer under the power loop components layer to shield the switching noise from other sensitive traces. Connect the analog ground GND and power grounds PGND together at a single point in a star ground connection.

- 8. The PCB layout also plays an important role in power dissipation and thermal performance. The PGND nodes are the main power connection area between the IC and outside the IC. Place the ground copper area as much as as possible around the PGND area to ensure efficient heat transfer. Place vias as many as possible around the PGND nodes to further transfer the heat down the internal ground plane and other layers to further improve the thermal resistance from the IC package to the ambient.

36V, 10A Fully Integrated Buck Converter with 10µA Quiescent Current and Dual-Phase Capability

Figure 2. PCB Layout Example

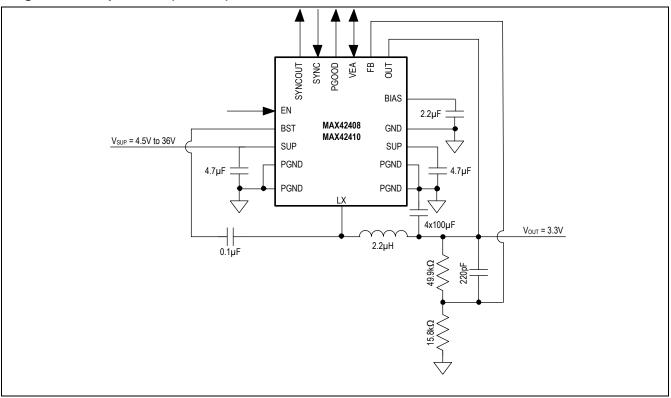

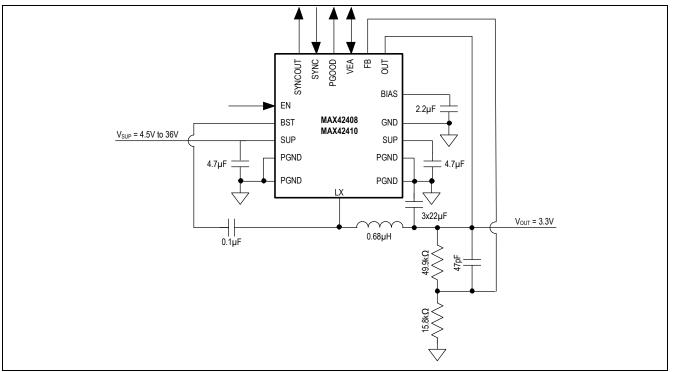

# **Typical Application Circuits**

### Single Phase Operation (1.5MHz)

# **Ordering Information**

| PART NUMBER    | V <sub>OUT</sub> (V)   | MAXIMUM<br>OPERATING<br>CURRENT (A) | FREQUENCY |

|----------------|------------------------|-------------------------------------|-----------|

| MAX42408AFOA+T | Adjustable 0.8V to 10V | 8                                   | 400kHz    |

| MAX42408AFOB+T | Adjustable 0.8V to 6V  | 8                                   | 1.5MHz    |

| MAX42410AFOA+T | Adjustable 0.8V to 10V | 10                                  | 400kHz    |

| MAX42410AFOB+T | Adjustable 0.8V to 6V  | 10                                  | 1.5MHz    |

+ denotes a lead(Pb)-free/RoHS-compliant package.

T denotes tape-and-reel.

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                         | PAGES<br>CHANGED         |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 0                  | 11/23            | Release for market intro                                                                                                                                                            | _                        |

| 1                  | 12/23            | Updated General Description, Benefits and Features, Absolute Maximum Ratings,<br>Electrical Characteristics, Typical Operating Characteristics and Detailed Information<br>sections | 1, 3, 4, 5, 7,<br>10, 11 |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.