# Dual SilentMOS Smart Power Stage in 5 mm × 8 mm LQFN

#### **FEATURES**

- ▶ 70 A Peak Output Current per Channel

- ▶ SilentMOS<sup>™</sup> Smart Power Stage

- ▶ Utilizes Low EMI/EMC Silent Switcher®2 Architecture

- Ultra-low SW-Voltage Overshoot

- ▶ Frequency Up to 2 MHz

- ► V<sub>IN</sub> Up to 16 V

- ▶ Up to 94% Efficiency at 1 MHz with 1.8 V<sub>OUT</sub>

- ▶ Integrated Boost Diodes and Capacitors

- ► Accurate Switch Current Monitoring

- ▶ Power MOSFET Overcurrent Protection

- ▶ Input Overvoltage and Bias Undervoltage Protection

- ▶ Thermal Monitor with Overtemperature Flag

- ▶ 3.3 V/5 V Compatible Tri-State PWM Input

- ▶ 5 mm × 8 mm LQFN Package

## **APPLICATIONS**

- ▶ High Current Servers and Workstations

- ▶ Networking/Telecom Microprocessor Supplies

- Small Form-Factor POL Converter

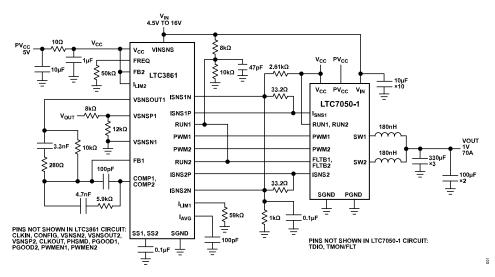

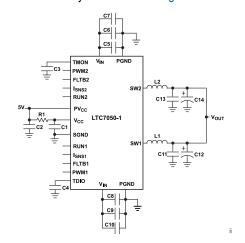

# TYPICAL APPLICATION

## **GENERAL DESCRIPTION**

The LTC®7050-1¹ dual monolithic power stage fully integrates high speed drivers with low resistance half-bridge power switches plus comprehensive monitoring and protection circuitry in an electrically and thermally optimized package. With a suitable high frequency controller, this power stage forms a compact, high current voltage regulator system with state-of-the-art efficiency and transient response.

SilentMOS technology utilizes second generation Silent Switcher 2 architecture reducing both EMI and switch-node voltage overshoot while maximizing efficiency at high switching frequencies.

High speed current sensing provides low latency switch current information, enabling tight current balancing and immediate overcurrent protection.

Thermally-enhanced packaging provides dual 35 A rated output current capability.

Figure 1. 12 V<sub>IN</sub>, 1 V/70 A<sub>OUT</sub> 1 MHz Dual-Phase POL Converter

Rev. A

<sup>&</sup>lt;sup>1</sup> Protected by U.S. patents, including 9525351.

# **TABLE OF CONTENTS**

| Features 1                                          | Voltage Fault Conditions        | 12 |

|-----------------------------------------------------|---------------------------------|----|

| Applications1                                       | Over Current Fault Conditions   | 12 |

| General Description1                                | Active Diode Mode               | 13 |

| Typical Application1                                | Applications Information        | 14 |

| Functional Block Diagram3                           | Power Sequence                  | 14 |

| Specifications4                                     | Fault Management                |    |

| Electrical Characteristics4                         | Current Sense and Current Limit |    |

| Absolute Maximum Ratings6                           | Frequency Selection             | 14 |

| ESD Caution6                                        | Input Capacitors                | 14 |

| Pin Configuration and Function Descriptions 7       | Inductor Selection              |    |

| Typical Performance Characteristics8                | Output Capacitors               | 15 |

| Theory of Operation12                               | Bypassing and Grounding         | 15 |

| Main Control Architecture12                         | PCB Layout                      |    |

| Current Sense12                                     | Typical Application             | 16 |

| Temperature Monitor and Overtemperature             | Outline Dimensions              |    |

| Fault 12                                            | Ordering Guide                  | 17 |

| REVISION HISTORY<br>6/2023—Rev. 0 to Rev. A         |                                 |    |

| Updated Format (Universal)                          |                                 |    |

| Changes to Figure 1                                 |                                 |    |

| Deleted Figure 2 and Figure 3; Renumbered Sequentia |                                 |    |

| Changes to Figure 2                                 |                                 |    |

| Changes to Table 1                                  |                                 |    |

| Changes to Table 2                                  |                                 |    |

| Changes to Figure 3                                 |                                 |    |

| Deleted Figure 26 and Figure 27                     |                                 |    |

| Changes to Power Sequence Section                   |                                 |    |

| Changes to Figure 31                                |                                 | 16 |

|                                                     |                                 |    |

1/2022—Revision 0: Initial Version

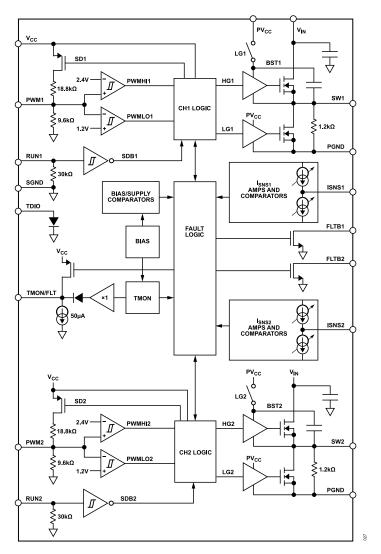

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Functional Block Diagram

# **SPECIFICATIONS**

# **ELECTRICAL CHARACTERISTICS**

$T_J$  = -40°C to +125°C for the minimum and maximum values,  $V_{IN}$  = 12 V,  $PV_{CC}$  =  $V_{CC}$  = 5 V, unless otherwise noted.

Table 1.

| Parameter <sup>1</sup>                                                     | Symbol                    | Test Conditions/Comments                                                        | Min  | Тур       | Max  | Unit |

|----------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------|------|-----------|------|------|

| V <sub>IN</sub> SUPPLY                                                     |                           |                                                                                 |      |           |      |      |

| Power Input Supply Range                                                   | V <sub>IN</sub>           |                                                                                 |      |           | 16   | V    |

| V <sub>IN</sub> Overvoltage Lockout Threshold                              |                           | V <sub>IN</sub> Rising                                                          | 17.7 |           | 18.7 | V    |

| V <sub>IN</sub> Overvoltage Lockout Hysteresis <sup>2</sup>                |                           | 6                                                                               |      | 1         |      | V    |

| V <sub>IN</sub> Overvoltage Lockout Delay <sup>2</sup>                     |                           |                                                                                 |      | 1         |      | μs   |

| V <sub>IN</sub> Shutdown Current <sup>2</sup>                              |                           | V <sub>IN</sub> = 12 V, RUN1 = RUN2 = 0                                         |      | 25        |      | μA   |

| V <sub>CC</sub> SUPPLY                                                     |                           |                                                                                 |      |           |      |      |

| V <sub>CC</sub> Input Supply Range                                         | V <sub>CC</sub>           |                                                                                 | 4.5  | 5         | 5.5  | V    |

| V <sub>CC</sub> Undervoltage Lockout Threshold                             | V <sub>CC(UVLO)</sub>     | V <sub>CC</sub> Rising                                                          | 4.05 | 4.15      | 4.25 | V    |

| V <sub>CC</sub> Undervoltage Lockout Hysteresis <sup>2</sup>               | V <sub>UVLO_HYST</sub>    |                                                                                 |      | 0.2       |      | V    |

| V <sub>CC</sub> Supply Current in Shutdown <sup>2</sup>                    | I <sub>VCC(SD)</sub>      | RUN1 = RUN2 = 0 V                                                               |      | 14        |      | μA   |

| V <sub>CC</sub> Supply Current in Active <sup>2</sup>                      | I <sub>VCC_active</sub>   | RUN1 = RUN2 = 5 V, PWM = Float                                                  |      | 2.5       |      | mA   |

| PV <sub>CC</sub> SUPPLY                                                    | 100_000                   |                                                                                 |      |           |      |      |

| Driver Input Supply Range                                                  | PV <sub>CC</sub>          |                                                                                 | 4.5  | 5         | 5.5  | ٧    |

| PV <sub>CC</sub> Undervoltage Lockout Threshold                            | PV <sub>CC(UVLO)</sub>    | PV <sub>CC</sub> Rising                                                         | 3.9  | 4.0       | 4.1  | V    |

| PV <sub>CC</sub> Undervoltage Lockout Hysteresis <sup>2</sup>              | PV <sub>UVLO_HYST</sub>   |                                                                                 |      | 0.35      |      | V    |

| PV <sub>CC</sub> Supply Current in Shutdown <sup>2</sup>                   | I <sub>PVCC(SD)</sub>     | RUN1 = RUN2 = 0 V                                                               |      | 300       |      | μA   |

| PV <sub>CC</sub> and V <sub>CC</sub> Supply Current in Active <sup>2</sup> | I <sub>PVCC_active</sub>  | RUN1 = RUN2 = 5 V, PWM = Float                                                  |      | 2.5       |      | mA   |

| UNDERVOLTAGE TIME LOCKOUT DELAY, FROM V <sub>CC</sub>                      | t <sub>UVLO</sub>         | PV <sub>CC</sub> , V <sub>CC</sub> Rising                                       |      | 1         |      | μs   |

| AND PV <sub>CC</sub> TO SW LOW <sup>2, 3</sup>                             |                           | RUN = 5 V PWM = 0                                                               |      |           |      |      |

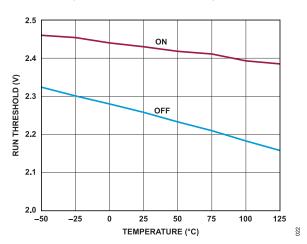

| RUN INPUT                                                                  |                           |                                                                                 |      |           |      |      |

| RUN High Threshold                                                         | V <sub>IH_RUN</sub>       | RUN Rising                                                                      | 2.2  | 2.45      | 2.7  | V    |

| RUN Hysteresis <sup>2</sup>                                                | V <sub>RUN_HYS</sub>      |                                                                                 |      | 0.2       |      | V    |

| EN Pull-Down Resistor <sup>2</sup>                                         | R <sub>PD_RUN</sub>       |                                                                                 |      | 30        |      | kΩ   |

| Propagation Delay for RUN Low to High <sup>2, 3</sup>                      | T <sub>d_RUNH</sub>       | From RUN Low ≥ High to SW = 0, PWM = 0                                          |      | 12        |      | μs   |

| Propagation Delay for RUN High to Low <sup>2, 3</sup>                      | T <sub>d_RUNL</sub>       | From RUN High ≥ Low to SW High Z, PWM = 0                                       |      |           | 0.1  | μs   |

| PWM INPUT                                                                  | _                         |                                                                                 |      |           |      |      |

| PWM High Threshold                                                         | $V_{IH\_PWM}$             | V <sub>IN</sub> = 1 V, PV <sub>CC</sub> = 6 V                                   |      |           | 2.7  | V    |

| PWM Low Threshold                                                          | V <sub>IL PWM</sub>       | V <sub>IN</sub> = 5 V                                                           | 0.8  |           |      | V    |

| PWM Tri-State Range                                                        | V <sub>TR_PWM</sub>       | V <sub>IN</sub> = 1 V and 5 V                                                   | 1.5  |           | 2.1  | V    |

| PWM Pull-Down Resistor <sup>2</sup>                                        | R <sub>PD_PWM</sub>       | To SGND, V <sub>IN</sub> = 5 V                                                  |      | 9.6       |      | kΩ   |

| PWM Pull-Up Resistor <sup>2</sup>                                          | R <sub>PU_PWM</sub>       | To V <sub>CC</sub> , V <sub>IN</sub> = 5 V                                      |      | 18.8      |      | kΩ   |

| Delay Time, PWM High to SW High <sup>2, 3</sup>                            | t <sub>PWMHI-SW</sub>     | No Fault Condition                                                              |      | 10        |      | ns   |

| Delay Time, PWM Low to SW Low <sup>2, 3</sup>                              | t <sub>PWMLO-SW</sub>     | No Fault Condition                                                              |      | 10        |      | ns   |

| Tri-State to Low Propagation Delay <sup>2</sup>                            | t <sub>Tri_Lo_Delay</sub> | PWM Going Low to SW Going Low, V <sub>IN</sub> = 5 V                            |      | 20        |      | ns   |

| Tri-State to High Propagation Delay <sup>2</sup>                           | t <sub>Tri_Hi_Delay</sub> | PWM Going High to SW Going High, V <sub>IN</sub> = 5 V                          |      | 30        |      | ns   |

| Active to Tri-State Delay Time <sup>2</sup>                                | t <sub>Tri_Hold</sub>     | PWM Going to High Z to SW High Z                                                |      | 20        |      | ns   |

| PWM Minimum ON-Time <sup>2</sup>                                           | t <sub>PWM MINON</sub>    | V <sub>IN</sub> = 5 V                                                           |      | 20        |      | ns   |

| PWM Floating Voltage                                                       | V <sub>PWM FLOAT</sub>    |                                                                                 | 1.6  | 1.7       | 1.8  | ٧    |

| I <sub>SNS</sub> OUTPUT                                                    |                           |                                                                                 |      |           |      |      |

| Current Sense Gain (I <sub>MON</sub> /I <sub>OUT</sub> ) <sup>2</sup>      | A <sub>IMON</sub>         | V <sub>ISNS</sub> = 1.5 V                                                       | 8.5  | 10        | 11.5 | µA/A |

| ,                                                                          |                           | I <sub>OUT</sub> = 5 A to 25 A, PWM = 0, V <sub>IN</sub> = 5 V                  |      |           |      | ľ    |

| Overall Accuracy <sup>2</sup>                                              | I <sub>SNS</sub>          | $I_{OUT}$ = 25 A, $V_{ISNS}$ = 1.5 V, PWM = 0, $V_{IN}$ = 5 V, Accuracy at Trim |      | 250 ±12.5 | 5    | μA   |

|                                                                            |                           | $I_{OUT} = -10 \text{ A}, V_{ISNS} = 1.5 \text{ V}, PWM = 0$                    |      | 100       |      | μA   |

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter <sup>1</sup>                                      | Symbol                   | Test Conditions/Comments                                                     | Min | Тур  | Max | Unit  |

|-------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------|-----|------|-----|-------|

| IMON Operational Voltage Range                              | V <sub>IMON</sub>        | V <sub>IN</sub> = 5 V                                                        | 1.2 |      | 2.0 | V     |

| FLTB OUTPUT                                                 |                          |                                                                              |     |      |     |       |

| Fault Bar Open-Drain Pull-Down Resistance <sup>2</sup>      | R <sub>FLTB-PD</sub>     | FLTB Low                                                                     |     |      | 1   | kΩ    |

| TMON/FLT OUTPUT                                             |                          |                                                                              |     |      |     |       |

| Thermal Monitor Gain <sup>2, 3</sup>                        | A <sub>TMON</sub>        | 0°C < T <sub>J</sub> < 150°C                                                 |     | 8    |     | mV/°C |

| Thermal Monitor Voltage <sup>2, 3</sup>                     | V <sub>TMON</sub>        | $T_J = 0$ °C                                                                 |     | 0.6  |     | V     |

|                                                             |                          | $T_J = 25^{\circ}C, V_{IN} = 1 V$                                            | 780 | 800  | 825 | mV    |

|                                                             |                          | T <sub>J</sub> = 125°C                                                       |     | 1.6  |     | ٧     |

| Overtemperature Protection Accuracy <sup>2, 3</sup>         | OTP                      |                                                                              |     | 150  |     | °C    |

| Overtemperature Hysteresis <sup>2, 3</sup>                  | OTP_Hys                  |                                                                              |     | 40   |     | °C    |

| Thermal Monitor Maximum Source Current <sup>2</sup>         | I <sub>SOURCE_TMON</sub> | T <sub>J</sub> = 25°C, T <sub>MON</sub> Forced at 0 V, V <sub>IN</sub> = 1 V |     | 650  |     | μA    |

| Thermal Monitor Maximum Sink Current <sup>2</sup>           | I <sub>SINK_TMON</sub>   | $T_J = 25$ °C, $T_{MON}$ Forced at 1.28 V, $V_{IN} = 1$ V                    |     | 45   |     | μA    |

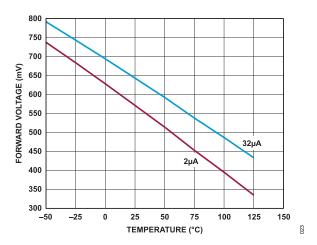

| Tdiode Forward Voltage Drop <sup>2</sup>                    | _                        | $T_J = 25$ °C, $I_F = 0.1$ mA, $V_{IN} = 1$ V                                |     | 678  |     | mV    |

| Tdiode Voltage Drop Temperature Coefficient <sup>2, 3</sup> | $V_{Tdiode}$             | I <sub>F</sub> = 0.1mA                                                       |     | -1.8 |     | mV/°C |

| SW NODE                                                     |                          |                                                                              |     |      |     |       |

| SW Floating Voltage <sup>2</sup>                            | V <sub>SW Float</sub>    | V <sub>IN</sub> = 12 V                                                       |     | 0.7  |     | V     |

| SW Pull-Down Resistance <sup>2</sup>                        | R <sub>SW-PGND</sub>     | V <sub>IN</sub> = 5 V                                                        |     | 1.2  |     | kΩ    |

| OVERCURRENT LIMITS                                          |                          |                                                                              |     |      |     |       |

| Positive Overcurrent Threshold <sup>2</sup>                 | I <sub>OCP</sub>         | PWM = H, V <sub>IN</sub> = 0.2 V                                             | 80  | 90   | 100 | Α     |

| Negative Overcurrent Threshold <sup>2</sup>                 | INCP                     | PWM = L, V <sub>IN</sub> = 1 V                                               |     | -45  |     | Α     |

| Positive Overcurrent Blanking Time <sup>2, 3</sup>          | t <sub>Blank OC</sub>    | PWM = H                                                                      |     | 22   |     | nS    |

| Negative Overcurrent Blanking Time <sup>2, 3</sup>          | t <sub>Blank_NC</sub>    | PWM = L                                                                      |     | 55   |     | nS    |

| Positive Zero Current Threshold <sup>2</sup>                | I_ZCP                    | V <sub>IN</sub> = 0.2 V                                                      |     | 5    |     | Α     |

| Negative Zero Current Threshold <sup>2</sup>                | I <sub>ZCN</sub>         | V <sub>IN</sub> = 1 V                                                        |     | -8   |     | Α     |

<sup>&</sup>lt;sup>1</sup> All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

<sup>&</sup>lt;sup>2</sup> Specifications are at  $T_A = 25$ °C.

<sup>&</sup>lt;sup>3</sup> This parameter is not tested but is guaranteed by design.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                             | Rating                                        |

|-------------------------------------------------------|-----------------------------------------------|

| V <sub>IN</sub> DC Voltage                            | -0.3 V to 19 V                                |

| V <sub>IN</sub> Transient Voltage                     | -0.3 V to 25 V                                |

| SW1, SW2 Voltage                                      | -0.3 V to 25 V DC                             |

| SW1, SW2 Voltage (20 ns)                              | –2 V to 25 V                                  |

| PV <sub>CC</sub> , V <sub>CC</sub> Voltage            | -0.3 V to 6 V                                 |

| PWM1, PWM2                                            | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V})$ |

| I <sub>SN</sub> S1, I <sub>SN</sub> S2                | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V})$ |

| FLTB1, FLTB2                                          | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V})$ |

| TDIO Voltage/Current                                  | -0.3 V/5 mA                                   |

| Absolute Maximum Junction Temperature <sup>1, 2</sup> | 125°C                                         |

| Storage Temperature                                   | -55°C to 150°C                                |

| Maximum Reflow (Package Body) Temperature             | 260°C                                         |

- The LTC7050-1 is specified over the  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  operating junction temperature range. High junction temperatures degrade operating lifetimes. Note the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature ( $T_J$ , in  $^{\circ}\text{C}$ ) is calculated from the ambient temperature ( $T_A$  in  $^{\circ}\text{C}$ ) and power dissipation ( $P_D$ , in watts) according to the formula:  $T_J = T_A + (P_D \times \theta_{JA})$  where  $\theta_{JA}$  (in  $^{\circ}\text{C/W}$ ) is the package thermal impedance.

- The LTC7050-1 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

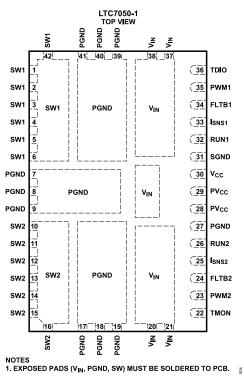

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

Table 3. Pin Function Descriptions

| Pin No. <sup>1</sup>           | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 6, 10 to 16, 42           | SW1, SW2         | Power Stage Switch Node. The output of the power stage, this node is connected to V <sub>IN</sub> through the high side N-channel FET and to PGND through the low side N-channel FET.                                                                                                                                                                                                                    |

| 7 to 9, 17 to 19, 27, 39 to 41 | PGND             | Power Stage Ground. This pin is connected to SW through the low side N-channel FET. Also powers the drivers.                                                                                                                                                                                                                                                                                             |

| 20, 21, 37, 38                 | V <sub>IN</sub>  | Power Stage Supply. This pin is connected to SW through the high side N-channel FET.                                                                                                                                                                                                                                                                                                                     |

| 22                             | TMON/FLT         | Temperature Monitor/Fault Pin. This pin provides a voltage, referred to SGND, of 0.6 V to 1.8 V corresponding to die temperature of 0°C to 150°C for a gain of 8 mV/°C. Above 150°C, the pin is pulled high to indicate an overtemperature (OT) fault. The pin has limited current sinking capability, so multiple like pins can be tied together for highest temperature and single-OT-fault reporting. |

| 23, 35                         | PWM1, PWM2       | PWM Input Pin. With RUN driven high, SW will nominally follow this pin high, low, and high-Z. Nominal 3 V CMOS logic levels; can be driven with 3 V to 5 V CMOS signals. Resistor divider holds voltage at 1.7 V when in high-Z state.                                                                                                                                                                   |

| 24, 34                         | FLTB1, FLTB2     | Fault Bar Pin. This open-drain pin pulls down when the chip/channel encounters a fault condition such as OC or OCN.                                                                                                                                                                                                                                                                                      |

| 25, 33                         | ISNS1, ISNS2     | Current Sense Pin. This pin sources/sinks instantaneous current equal to 1/100,000 the SW node current, positive and negative.                                                                                                                                                                                                                                                                           |

| 28, 29                         | PV <sub>CC</sub> | 5 V Driver Supply. This pin powers the low side gate driver directly and the high side gate driver through an internal bootstrapped supply riding on SW. Bypass this pin with a 10 $\mu$ F ceramic capacitor to PGND in close proximity to chip.                                                                                                                                                         |

| 30                             | V <sub>CC</sub>  | 5 V Supply. Bypass this pin with a 1 μF ceramic capacitor to SGND in close proximity to chip.                                                                                                                                                                                                                                                                                                            |

| 31                             | SGND             | Circuit Ground.                                                                                                                                                                                                                                                                                                                                                                                          |

| 36                             | TDIO             | Temperature Diode Pin. This pin provides a reference diode to SGND for use in measuring die temperature.                                                                                                                                                                                                                                                                                                 |

<sup>&</sup>lt;sup>1</sup> All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

Rev. A | 7 of 17 analog.com

# TYPICAL PERFORMANCE CHARACTERISTICS

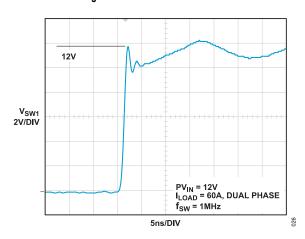

$T_A = 25$ °C,  $V_{IN} = 12$  V,  $PV_{CC} = V_{CC} = 5$  V, unless otherwise noted.

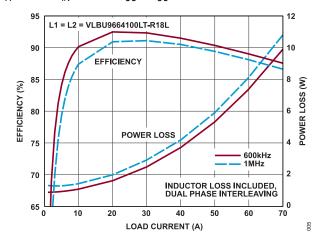

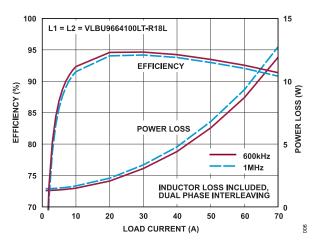

Figure 4. 12 V<sub>IN</sub> to 1 V<sub>OUT</sub> Efficiency

Figure 5. 12 V<sub>IN</sub> to 1.8 V<sub>OUT</sub> Efficiency

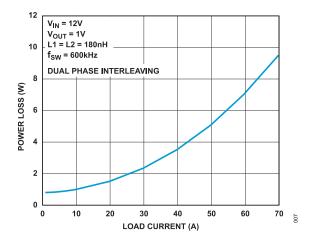

Figure 6. LTC7050-1 Power Dissipation vs. Load

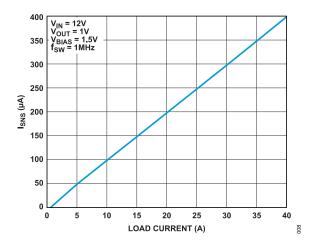

Figure 7. I<sub>SNS</sub> vs. Load

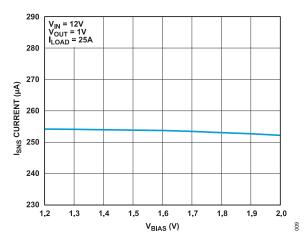

Figure 8. I<sub>SNS</sub> Current vs. V<sub>BIAS</sub>

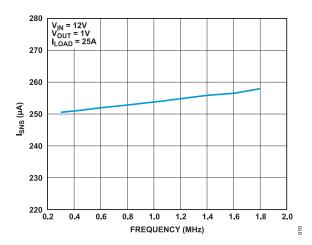

Figure 9.  $I_{\rm SNS}$  vs. Frequency

analog.com Rev. A | 8 of 17

# TYPICAL PERFORMANCE CHARACTERISTICS

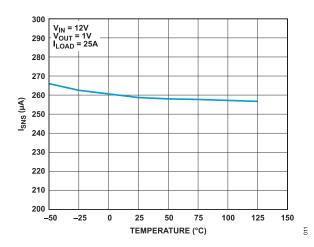

Figure 10. I<sub>SNS</sub> vs. Temperature

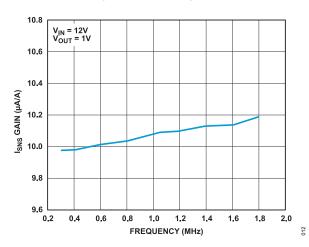

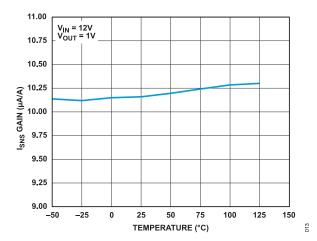

Figure 11. I<sub>SNS</sub> Gain vs. Frequency

Figure 12. I<sub>SNS</sub> Gain vs. Temperature

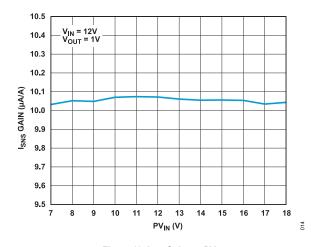

Figure 13. I<sub>SNS</sub> Gain vs. PV<sub>IN</sub>

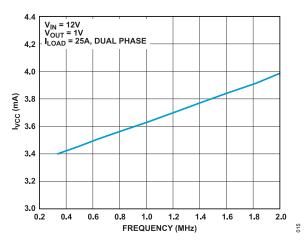

Figure 14. I<sub>VCC</sub> vs. Frequency

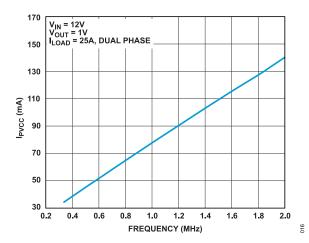

Figure 15. I<sub>PVCC</sub> vs. Frequency

analog.com Rev. A | 9 of 17

# TYPICAL PERFORMANCE CHARACTERISTICS

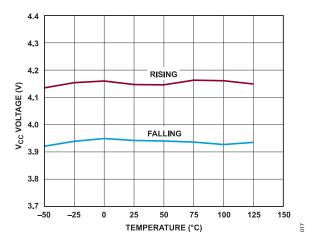

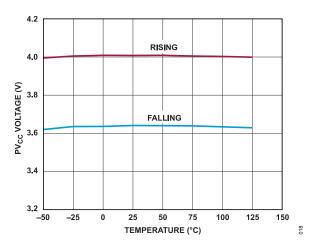

Figure 16. V<sub>CC</sub> UVLO vs. Temperature

Figure 17. PV<sub>CC</sub> UVLO vs. Temperature

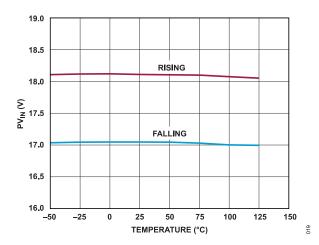

Figure 18.  $PV_{IN}$  OVLO vs. Temperature

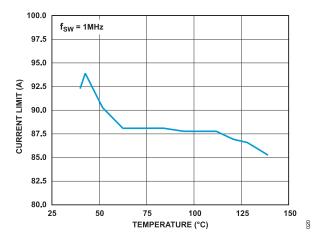

Figure 19. Current Limit vs. Temperature

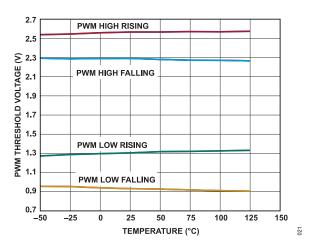

Figure 20. PWM Threshold vs. Temperature

Figure 21. RUN Threshold vs. Temperature

analog.com Rev. A | 10 of 17

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 22. T<sub>DIODE</sub> Forward Voltage vs. Temperature

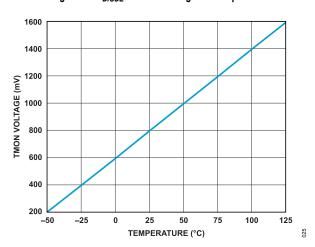

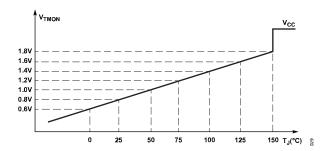

Figure 23. TMON vs. Temperature

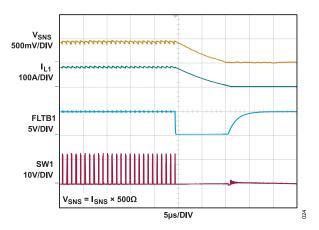

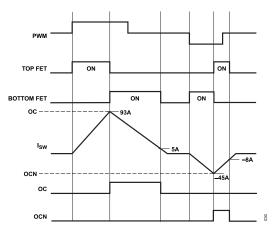

Figure 24. Overcurrent Protection

Figure 25. Switching Rising Edge

analog.com Rev. A | 11 of 17

#### THEORY OF OPERATION

#### MAIN CONTROL ARCHITECTURE

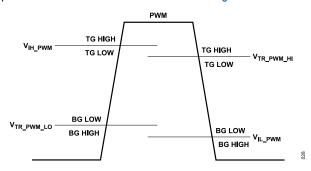

The LTC7050-1 is a dual-channel or dual-phase integrated-driver half-bridge power MOSFET stage for DC/DC step-down applications. It is designed to be used in a synchronous switching architecture with a controller utilizing 3.3 V or 5 V PWM three-state outputs. The relationship between the transition thresholds and the three input states of the LTC7050-1 is illustrated in Figure 26.

Figure 26. Three-State Input Operation

In normal operation, PWMHI turns on the high side FET, and PWMLO turns on the low side FET. SW node follows the PWM pin with a typical 10 ns delay. There is <1 ns dead time before SW rises from PGND to  $V_{\rm IN}$  and a typical 3 ns dead time after SW falls.

The high side FET driver is powered from the internal BST node to SW via an internal integrated switch and capacitor, which allows lower dropout than achievable with a typical diode as well as higher-frequency operation.

## **CURRENT SENSE**

Real-time current sense amplifiers provide a scaled-down version of SW current. During PWMHI or PWMLO, the  $I_{SNS}$  pin sources or sinks, according to SW current direction, a current equal to 1/100,000 the instantaneous SW current.

Associated current comparators flag high side FET positive overcurrent (OC) and low side FET negative overcurrent (OCN) conditions. Zero-current of both FETs are also detected by associated current comparators.

# TEMPERATURE MONITOR AND OVERTEMPERATURE FAULT

Normally, TMON outputs a voltage from 0.6 V to 1.8 V, corresponding to a die temperature range of 0°C to 150°C. The TMON voltage is calculated by:

$$V_{TMON}(V) = 800 \text{ mV} + (T_J(^{\circ}C) - 25^{\circ}C) \times (8 \text{ mV/}^{\circ}C)$$

(1)

Figure 27 illustrates the relationship between  $V_{\mbox{\scriptsize TMON}}$  and die temperature.

Figure 27. V<sub>TMON</sub> vs. Die Temperature

TMON is driven by an amplifier that can source current but has limited sinking capacity. This allows multiple TMON pins to be paralleled, with the highest temperature being reported. Overtemperature is triggered at 150°C (typical), and it causes the TMON pin to be pulled high to  $V_{CC}$ . The overtemperature fault will be cleared once the internal temperature falls 40°C (typical) below the threshold.

The TDIO pin is internally connected to the anode of a P/N junction diode while the cathode is connected to SGND. It provides an alternative measurement of die temperature for the controllers, such as LTC3884-1, to measure the die temperature using direct  $V_{\text{BE}}$  method or  $\Delta V_{\text{BE}}$  method.

#### **VOLTAGE FAULT CONDITIONS**

When  $V_{CC}$  or  $PV_{CC}$  is in UVLO, or  $V_{IN}$  is in OVLO, SW will not respond to PWM and both top FET and bottom FET are off.

When BST-to-SW voltage is in UVLO, SW will not respond to a PWMHI until a PWMLO is provided such that BST-to-SW voltage is recharged sufficiently.

### **OVER CURRENT FAULT CONDITIONS**

When the high side FET is on, instantaneous SW current of >93 A (net current flowing out of SW) will trip the overcurrent (OC) comparator and set the internal OC state. When this happens, regardless of PWM pin state, the high side FET will be turned off, and the low side FET will be turned on until SW current decreases to 5 A, at which point OC state will be reset. Normal PWMHI-to-high-side-FET and PWMLO-to-low-side-FET operation resumes.

When the low side FET is on, instantaneous SW current of <-45 A (net current flowing into SW) will trip the OCN comparator. When this happens, regardless of PWM pin state, the low side FET will be turned off and the high side FET will be turned on until SW current increases to -8 A, at which point OCN state will be reset. Normal PWMHI-to-high-side-FET and PWMLO-to-low-side-FET operation resumes. The trigger and reset of over current condition are illustrated in Figure 28.

In either OC or OCN condition, FLTB is pulled down.

analog.com Rev. A | 12 of 17

## THEORY OF OPERATION

#### **ACTIVE DIODE MODE**

If PWM goes from high to Hi-Z state while large (>5 A) currents are still flowing through the top FET from  $V_{\text{IN}}$  to SW, the top FET will turn off and the bottom FET will turn on to freewheel the current until it has been ramped down. If PWM goes from high to Hi-Z state while large (≥8 A) currents are still flowing through the top FET from SW to  $V_{\text{IN}}$ , the top FET will not turn off until the current has been ramped down.

Similarly, if PWM goes from low to Hi-Z state while large (≥8 A) currents are still flowing through the bottom FET from SW to PGND, the bottom FET will turn off, and the top FET will turn on to freewheel the current until it has been ramped down. If PWM goes from low to Hi-Z state while large (>5 A) currents are still flowing through the bottom FET from PGND to SW, the bottom FET will not turn off until the current has been ramped down.

Figure 28. Over Current Conditions

analog.com Rev. A | 13 of 17

## **APPLICATIONS INFORMATION**

#### **POWER SEQUENCE**

The LTC7050-1 requires the following input signals to operate normally:  $V_{\text{IN}},\,V_{\text{CC}}/\text{PV}_{\text{CC}},\,\,\text{RUN},\,\,\text{and PWM}.\,\,\text{Make sure that }V_{\text{IN}}$  and  $V_{\text{CC}}/\text{PV}_{\text{CC}}$  are present and the RUN pin of the LTC7050-1 is pulled up before enabling the PWM controller. Do not force RUN pin voltages above  $V_{\text{CC}}$  voltage.

#### **FAULT MANAGEMENT**

The fault management and shutdown mode of the LTC7050-1 is summarized in Table 4. Connecting the open-drain output FLTB pin to the controller's RUN pin can prevent the controller from starting up and force the converter to restart once the LTC7050-1 runs into fault conditions, except BST-to-SW undervoltage fault.

Table 4. Fault Management and Shutdown Mode Summary

| ,                     |      |                                            |                            |  |

|-----------------------|------|--------------------------------------------|----------------------------|--|

|                       | FLTB | Respond to PWM                             | TMON                       |  |

| V <sub>IN</sub> OVLO  | Low  | No, Both FETs Off When I <sub>SW</sub> ≈ 0 | Report Temperature         |  |

| V <sub>CC</sub> UVLO  | Low  | No, Both FETs Immediate Off                | Floating                   |  |

| PV <sub>CC</sub> UVLO | Low  | No, FETs Off When I <sub>SW</sub> ≈ 0      | Report Temperature         |  |

| Positive OC           | Low  | No, Top FET Immediate Off                  | Report Temperature         |  |

| Negative OC           | Low  | No, Bottom FET Immediate Off               | Report Temperature         |  |

| Overtemperature       | Low  | Yes                                        | Pull Up to V <sub>CC</sub> |  |

| BST-to-SW UV          | High | Ignore PWMHI                               | Report Temperature         |  |

| RUN Shutdown          | Low  | No, Both FETs Immediate Off                | Floating                   |  |

## **CURRENT SENSE AND CURRENT LIMIT**

$I_{SNS}$  sources and sinks a current which is 1/100,000 of the SW current. According to the controller's maximum current sense signal range, select a proper resistor to convert the  $I_{SNS}$  current into a differential voltage signal reflecting the real-time SW current. The resistor should be biased at a low impedance common mode voltage, which has current sinking and sourcing capability. Make sure that at the maximum positive current and negative current, the  $I_{SNS}$  pin voltage is in the specified range so that the gain  $I_{SNS}/I_{SW}$  remains constant.

A general LTC7050-1 application circuit is shown on the first page of this data sheet. The LTC7050-1 is optimized for the application of high frequency high current voltage regulator. External component selection is largely driven by the load requirement and begins with the selection of the switching frequency  $f_{SW}$  and inductor L. Once the inductor is chosen, the input capacitor,  $C_{IN}$ , the output capacitor,  $C_{OUT}$ , can be selected. The  $I_{SNS}$  resistors are selected to set the current limit.

#### **FREQUENCY SELECTION**

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing FET switching losses, but requires larger inductance and/or capacitance to maintain low output ripple voltage. In the selection of switching frequency, make sure that the high side on-time at maximum input voltage is longer than the LTC7050-1's

minimum on-time,  $t_{ON(MIN)}$ , which is the smallest time duration that the LTC7050-1 is capable of turning on the top FET. It is determined by internal timing delays, power stage timing delays and the gate charge required to turn on the top FET. Low duty cycle applications may approach this minimum on-time limit (see Equation 2).

$$t_{ON(MIN)} < \frac{v_{OUT}}{v_{IN} \times f_{SW}} \tag{2}$$

#### **INPUT CAPACITORS**

The LTC7050-1 should be connected to a  $V_{IN}$  supply through low impedance power planes. Ceramic input capacitors should be placed as close to the package as physically possible, with size and quantity appropriate for temperature rise with ripple current as calculated below.

For a buck converter, the switching duty cycle can be estimated by Equation 3.

$$D = \frac{V_{OUT}}{V_{IN}} \tag{3}$$

Without considering the inductor ripple current, for each output, the RMS current of the input capacitor can be estimated by Equation 4.

$$I_{CIN(RMS)} = \frac{I_{OUT(MAX)}}{\eta} \times \sqrt{D \times (1 - D)}$$

(4)

where  $\eta$  is the estimated efficiency of the power section.

## INDUCTOR SELECTION

Given the desired input and output voltages, the inductor value and operating frequency, f<sub>SW</sub>, directly determine the inductor's peak-to-peak ripple current (Equation 5).

$$I_{RIPPLE} = \frac{V_{OUT}}{V_{IN}} \left( \frac{V_{IN} - V_{OUT}}{f_{SW} \times L} \right) \tag{5}$$

Lower ripple current reduces core losses in the inductor, ESR losses in the output capacitors and output voltage ripple. Thus, highest efficiency operation is obtained at low frequency with a small ripple current. Achieving this, however, requires a large inductor. A reasonable starting point is to choose a ripple current that is about 40% of I<sub>OUT(MAX)</sub>. Note that the largest ripple current occurs at the highest input voltage. To guarantee that ripple current does not exceed a specified maximum, the inductor should be chosen according to Equation 6.

$$L \ge \left(\frac{V_{IN} - V_{OUT}}{f_{SW} \times I_{RIPPLE}}\right) \times \frac{V_{OUT}}{V_{IN}} \tag{6}$$

Once the inductance value is determined, the type of inductor must be selected. Core loss is independent of core size for a fixed inductor value, but it is very dependent on inductance selected. As inductance increases, core losses go down. Unfortunately, increased inductance requires more turns of wire and therefore copper losses will increase. Ferrite designs have very low core loss and are preferred at high switching frequencies, so design goals can concentrate on copper loss and preventing saturation.

analog.com Rev. A | 14 of 17

# **APPLICATIONS INFORMATION**

Ferrite core material saturates hard, which means that inductance collapses abruptly when the peak design current is exceeded. This results in an abrupt increase in inductor ripple current and consequent output voltage ripple. Do not allow the core to saturate!

#### **OUTPUT CAPACITORS**

The LTC7050-1 is designed for high frequency switching and low output voltage ripple noise. The bulk output capacitors defined as  $C_{OUT}$  are chosen with low enough effective series resistance (ESR) to meet the output voltage ripple and transient requirements.  $C_{OUT}$  can be a low ESR tantalum capacitor, a low ESR polymer capacitor, or ceramic capacitors. At 1 MHz, the typical output capacitance range is from 500  $\mu$ F to 1000  $\mu$ F. Additional output filtering may be required by the system designer if further reduction of output ripple or dynamic transient spikes is required.

#### BYPASSING AND GROUNDING

The LTC7050-1 requires proper bypassing on the PV $_{\rm CC}$  and V $_{\rm CC}$  supplies due to its high speed switching (nanoseconds) and large AC currents (amperes). Careless component placement and PCB trace routing may cause excessive ringing and under/overshoot. Follow the following steps to obtain the optimum performance from the LTC7050-1:

- Mount the bypass capacitors as close as possible between the V<sub>CC</sub> and SGND pins, and the PV<sub>CC</sub> and PGND pins. The traces should be shortened as much as possible to reduce lead inductance.

- 2. Use a low inductance, low impedance ground plane to reduce any ground drop and stray capacitance. Any significant ground drop will degrade signal integrity.

- Plan the power/ground routing carefully. Know where the large load switching current is coming from and going to. Maintain separate ground return paths for the input pin and the output power stage.

- 4. Be sure to solder the Exposed Pad on the back side of the LTC7050-1 packages to the board. Failure to make good thermal contact between the exposed back side and the copper board will result in far greater thermal resistances.

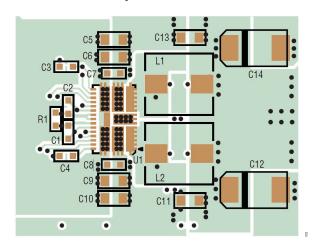

#### **PCB LAYOUT**

Due to the LTC7050-1's high power density and high speed, high frequency operation, proper PCB layout and composition are critical to maximizing performance.

At a minimum, the PCB should be 4-layer with at least top and bottom layers 2 oz. copper. As much as possible, top and bottom layers should be continuous  $V_{\text{IN}}$  and PGND areas. At least one inner layer, preferably the second, should be a continuous PGND plane.

Copper-filled vias should be used under the package exposed pads to connect top and bottom PCB layers.  $\theta_{JCbottom}$  is <1°C/W. Anything less than copper-filled vias will compromise  $\theta_{JA}$  greatly.

The inductor pads should be placed as close as possible to the package, with traces as short and wide as possible. If possible, SW traces should be doubled up with the second layer, taking care not to couple to sensitive traces.

A recommended PCB layout is shown in Figure 30.

Figure 29. Schematic

Figure 30. Example PCB Layout

analog.com Rev. A | 15 of 17

# **APPLICATIONS INFORMATION**

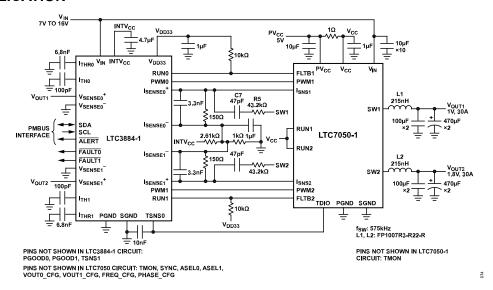

# **TYPICAL APPLICATION**

Figure 31. LTC7050-1 and LTC3884-1 Schematic

## **Related Parts**

#### Table 5.

| Part Number       | Description                                                                                                   | Comments                                                                                                                                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC7050           | Dual SilentMOS Smart Power Stage in 5 mm × 8 mm LQFN                                                          | 70 A Peak Current per Channel, Silent Switcher 2 Architecture, V <sub>IN</sub> Up to 14 V, 5 mm × 8 mm LQFN Package                                                                                                |

| LTC7051           | SilentMOS Smart Power Stage in 5 mm × 8 mm LQFN                                                               | 140 A Peak Current, Silent Switcher 2 Architecture, V <sub>IN</sub> Up to 14 V, 5 mm × 8 mm LQFN Package                                                                                                           |

| LTC7051-1         | SilentMOS Smart Power Stage in 5 mm × 8 mm LQFN                                                               | 140 A Peak Current, Silent Switcher 2 Architecture, V <sub>IN</sub> Up to 16 V, 5 mm × 8 mm LQFN Package                                                                                                           |

| LTC3888/LTC3888-1 | Dual Output 8-Phase Step-Down DC/DC Controller with Digital Power System Management                           | $4.5 \text{ V} \le \text{V}_{\text{IN}} \le 26.5 \text{ V}, 0.3 \text{ V} \le \text{V}_{\text{OUT}} \le 3.45 \text{ V}, 1^2\text{C/PMBus Control, Programmable}$<br>Loop Compesation, 5 mm × 8 mm QFN-52           |

| LTC3884/LTC3884-1 | Dual Output PolyPhase® Step-Down Controller with Sub-Milliohm DCR Sensing and Digital Power System Management | $4.5~V \le V_{IN} \le 38~V,~0.5~V \le V_{OUT} \le 5.5~V,~l^2C/PMBus~Control,~Programmable~Loop~Compesation,~5~mm \times 8~mm~QFN-52$                                                                               |

| LTC7851           | Quad Output Multiphase Step-Down Voltage Mode DC/DC Controller with Accurate Current Sharing                  | Operates with DrMOS, Power Blocks or External Drivers/MOSFETs, $V_{IN}$ Range Depends on External Components, $4.5 \text{ V} \le V_{CC} \le 5.5 \text{ V}$ , $0.6 \text{ V} \le V_{OUT} \le V_{CC} -0.5 \text{ V}$ |

| LTC7852/LTC7252-1 | Dual Output 6-Phase Current Mode Synchronous Buck<br>Controller with Current Monitoring                       | Operates with DrMOS, Power Blocks, 0.5 V ≤ V <sub>OUT</sub> ≤ 2 V, Hiccup Mode Overcurrent Protection, Flexible Phase Configuration                                                                                |

| LTC3861           | Dual, Multiphase Step-Down Voltage Mode DC/DC Controller with Accurate Current Sharing                        | Operates with Power Blocks, DrMOS or External MOSFETs 3 V≤ V <sub>IN</sub> ≤ 24 V                                                                                                                                  |

| LTC3882/LTC3882-1 | Dual Output Multiphase Step-Down DC/DC Voltage Mode Controller with Digital Power System Management           | $3~V \le V_{IN} \le 38~V,~0.5~V \le V_{OUT1,2} \le 5.25~V,~\pm 0.5\%~V_{OUT}$ Accuracy $I^2C/PMBus$ Interface, uses DrMOS or Power Blocks                                                                          |

| LTC3887/LTC3887-1 | Dual Output Multiphase Step-Down DC/DC Controller with Digital Power System Management, 70 mS Start-Up        | $4.5~V \le V_{\text{IN}} \le 24~V,~0.5~V \le V_{\text{OUT0},1}~(\pm 0.5\%) \le 5.5~V,~70~\text{mS}$ Start-Up, I <sup>2</sup> C/PMBus Interface, $-1$ Version uses DrMOS or Power Blocks                            |

analog.com Rev. A | 16 of 17

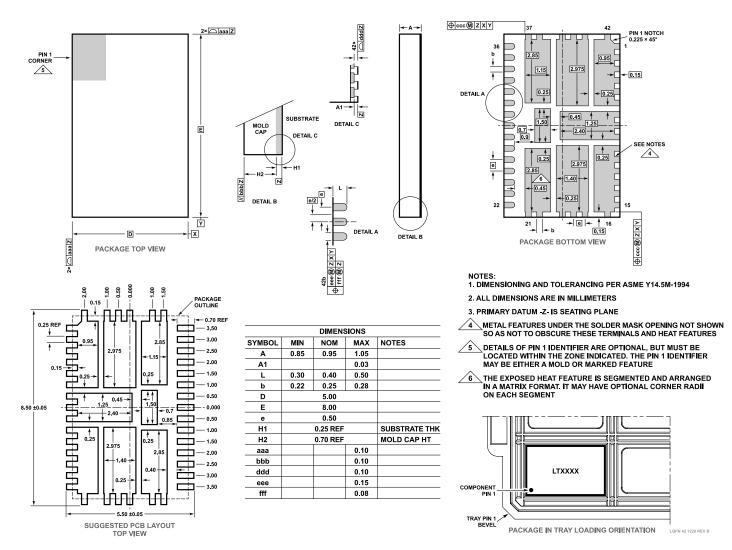

# **OUTLINE DIMENSIONS**

Figure 32. 42-Lead, 5 mm × 8 mm × 0.95 mm, LQFN (05-08-1571)

Dimensions shown in millimeters

Updated: June 08, 2023

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                     | Package Option |

|--------------------|-------------------|-----------------------------------------|----------------|

| LTC7050AV-1#PBF    | -40°C to +125°C   | 42-Lead LQFN (8mm x 5mm x 0.95mm w/ EP) | 05-08-1571     |

<sup>&</sup>lt;sup>1</sup> All models are RoHS compliant.