### Low Phase Noise, Dual Output Buffer/Driver/ Logic Converter

### FEATURES

- Low Phase Noise Buffer/Driver

- Optimized Conversion of Sine Wave Signals to Logic Levels

- Three Logic Output Types Available

- LVPECL

- LVDS

- CMOS

- Additive Jitter 45fs<sub>RMS</sub> (LTC6957-1)

- Frequency Range Up to 300MHz

- 3.15V to 3.45V Supply Operation

- Low Skew 3ps Typical

- Fully Specified from –40°C to 125°C

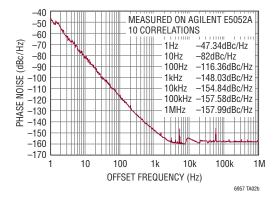

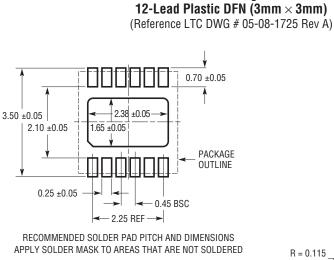

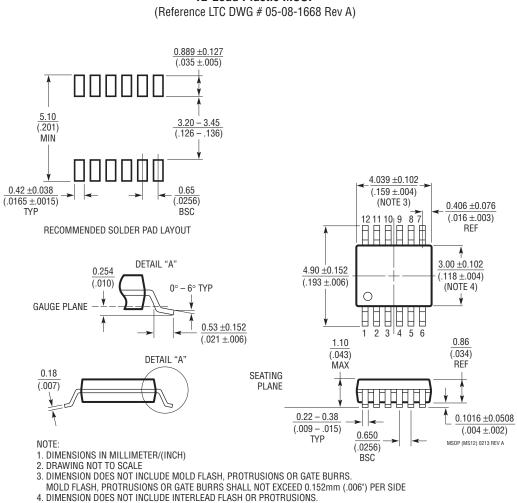

- 12-Lead MSOP and 3mm × 3mm DFN Packages

### **APPLICATIONS**

- System Reference Frequency Distribution

- High Speed ADC, DAC, DDS Clock Driver

- Military and Secure Radio

- Low Noise Timing Trigger

- Broadband Wireless Transceiver

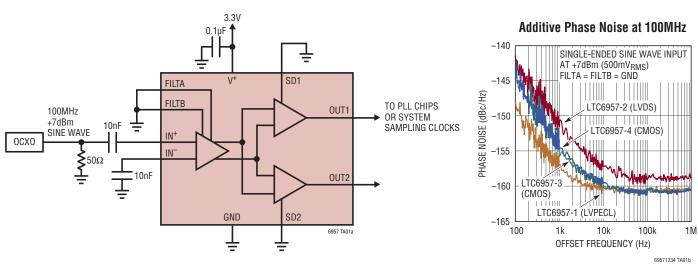

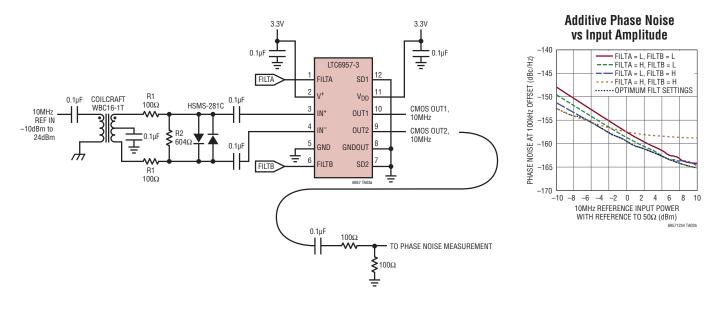

TYPICAL APPLICATION

- High Speed Data Acquisition

- Medical Imaging

- Test and Measurement

# DESCRIPTION

The LTC<sup>®</sup>6957-1/LTC6957-2/LTC6957-3/LTC6957-4 is a family of very low phase noise, dual output AC signal buffer/driver/logic level translators. The input signal can be a sine wave or any logic level ( $\leq 2V_{P-P}$ ). There are four members of the family that differ in their output logic signal type as follows:

LTC6957-1: LVPECL Logic Outputs

LTC6957-2: LVDS Logic Outputs

LTC6957-3: CMOS Logic, In-Phase Outputs

LTC6957-4: CMOS Logic, Complementary Outputs

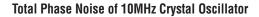

The LTC6957 will buffer and distribute any logic signal with minimal additive noise, however, the part really excels at translating sine wave signals to logic levels. The early amplifier stages have selectable lowpass filtering to minimize the noise while still amplifying the signal to increase its slew rate. This input stage filtering/noise limiting is especially helpful in delivering the lowest possible phase noise signal with slow slewing input signals such as a typical 10MHz sine wave system reference.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents 7969189 and 8319551.

### www.datasheetall.com

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Supply Voltage (V <sup>+</sup> or V <sub>DD</sub> ) to GND                 | 3.6V  |

|----------------------------------------------------------------------------|-------|

| Input Current (IN <sup>+</sup> , IN <sup>-</sup> , FILTA, FILTB, SD1, SD2) |       |

| (Note 2)                                                                   | ±10mA |

| LTC6957-1 Output Current 1mA,                                              | –30mA |

| LTC6957-2 Output Current                                                   | ±10mA |

| LTC6957-3, LTC6957-4 Output Current (Note 3).                              | ±30mA |

|                                                                            |       |

#### Specified Temperature Range

| LTC69571                             | 40°C to 85°C     |

|--------------------------------------|------------------|

| LTC6957H                             | 40°C to 125°C    |

| Junction Temperature                 | 150°C            |

| Storage Temperature Range            | –65°C to 150°C   |

| Lead Temperature (for MSOP Soldering | ng, 10sec) 300°C |

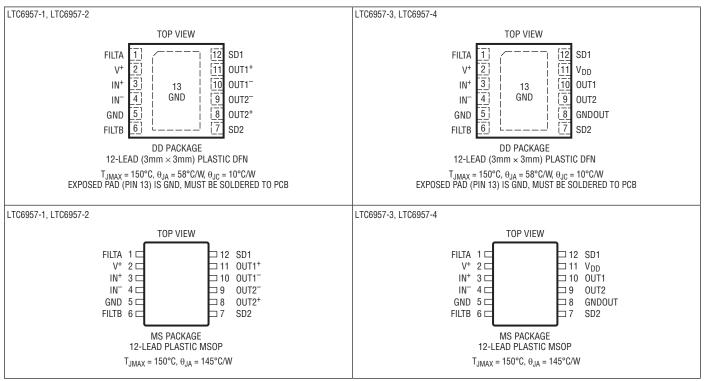

### PIN CONFIGURATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | SPECIFIED TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-----------------------------|

| LTC6957IDD-1#PBF | LTC6957IDD-1#TRPBF | LFQJ          | 12-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C               |

| LTC6957IDD-2#PBF | LTC6957IDD-2#TRPBF | LFQK          | 12-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C               |

| LTC6957IDD-3#PBF | LTC6957IDD-3#TRPBF | LFQM          | 12-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C               |

| LTC6957IDD-4#PBF | LTC6957IDD-4#TRPBF | LFQN          | 12-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C               |

| LTC6957IMS-1#PBF | LTC6957IMS-1#TRPBF | 69571         | 12-Lead Plastic MSOP            | -40°C to 85°C               |

| LTC6957HMS-1#PBF | LTC6957HMS-1#TRPBF | 69571         | 12-Lead Plastic MSOP            | -40°C to 125°C              |

| LTC6957IMS-2#PBF | LTC6957IMS-2#TRPBF | 69572         | 12-Lead Plastic MSOP            | -40°C to 85°C               |

| LTC6957HMS-2#PBF | LTC6957HMS-2#TRPBF | 69572         | 12-Lead Plastic MSOP            | -40°C to 125°C              |

| LTC6957IMS-3#PBF | LTC6957IMS-3#TRPBF | 69573         | 12-Lead Plastic MSOP            | -40°C to 85°C               |

| LTC6957HMS-3#PBF | LTC6957HMS-3#TRPBF | 69573         | 12-Lead Plastic MSOP            | -40°C to 125°C              |

| LTC6957IMS-4#PBF | LTC6957IMS-4#TRPBF | 69574         | 12-Lead Plastic MSOP            | -40°C to 85°C               |

| LTC6957HMS-4#PBF | LTC6957HMS-4#TRPBF | 69574         | 12-Lead Plastic MSOP            | -40°C to 125°C              |

### ORDER INFORMATION http://www.linear.com/product/LTC6957-1#orderinfo

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

### ELECTRICAL CHARACTERISTICS LTC6957-1

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 3.3V, SD1 = SD2 = 0.4V, FILTA = FILTB = 0.4V, R<sub>LOAD</sub> = 50 $\Omega$  connected to 1.3V, unless otherwise specified. All voltages are with respect to ground.

| SYMBOL                   | PARAMETER                                                                                                                                                                              | CONDITIONS                                                                                                                        |             | MIN                                          | ТҮР                          | MAX                    | UNITS                            |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------|------------------------------|------------------------|----------------------------------|

| Inputs (IN               | i <sup>-</sup> , IN+)                                                                                                                                                                  | l                                                                                                                                 |             |                                              |                              |                        |                                  |

| f <sub>IN</sub>          | Input Frequency Range                                                                                                                                                                  |                                                                                                                                   | ٠           |                                              |                              | 300                    | MHz                              |

| V <sub>INSE</sub>        | Input Signal Level Range, Single-Ended                                                                                                                                                 |                                                                                                                                   | ٠           | 0.2                                          | 0.8                          | 2                      | V <sub>P-P</sub>                 |

| VINDIFF                  | Input Signal Level Range, Differential                                                                                                                                                 |                                                                                                                                   | ٠           | 0.2                                          | 0.8                          | 2                      | V <sub>P-P</sub>                 |

| t <sub>MIN</sub>         | Minimum Input Pulse Width                                                                                                                                                              | High or Low                                                                                                                       |             |                                              | 0.5                          |                        | ns                               |

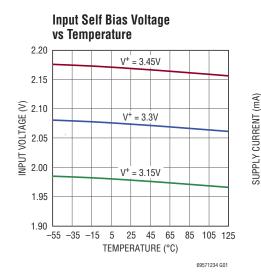

| VINCM                    | Self-Bias Voltage, IN <sup>+</sup> , IN <sup>−</sup>                                                                                                                                   |                                                                                                                                   | ٠           | 1.8                                          | 2.06                         | 2.3                    | V                                |

| R <sub>IN</sub>          | Input Resistance, Differential                                                                                                                                                         |                                                                                                                                   | ٠           | 1.5                                          | 2                            | 2.5                    | kΩ                               |

| CIN                      | Input Capacitance, Differential                                                                                                                                                        |                                                                                                                                   |             |                                              | 0.5                          |                        | pF                               |

| BW <sub>IN</sub>         | Input Section Small Signal Bandwidth (–3dB)                                                                                                                                            | FILTB = L, FILTA = L<br>FILTB = L, FILTA = H<br>FILTB = H, FILTA = L<br>FILTB = H, FILTA = H                                      |             |                                              | 1200<br>500<br>160<br>50     |                        | MHz<br>MHz<br>MHz<br>MHz         |

| Outputs (I               | LVPECL)                                                                                                                                                                                |                                                                                                                                   |             |                                              |                              |                        |                                  |

| V <sub>OH</sub>          | Output High Voltage                                                                                                                                                                    | LTC6957I<br>LTC6957H                                                                                                              | •           |                                              | $V^+ - 0.98$<br>$V^+ - 0.98$ |                        | V<br>V                           |

| V <sub>OL</sub>          | Output Low Voltage                                                                                                                                                                     | LTC6957I<br>LTC6957H                                                                                                              | •           | V <sup>+</sup> – 2.1<br>V <sup>+</sup> – 2.1 |                              | V+ – 1.67<br>V+ – 1.62 | V<br>V                           |

| V <sub>OD</sub>          | Output Differential Voltage                                                                                                                                                            |                                                                                                                                   | ٠           | ±660                                         | ±810                         | ±965                   | mV                               |

| t <sub>r</sub>           | Output Rise Time                                                                                                                                                                       |                                                                                                                                   |             |                                              | 180                          |                        | ps                               |

| t <sub>f</sub>           | Output Fall Time                                                                                                                                                                       |                                                                                                                                   |             |                                              | 160                          |                        | ps                               |

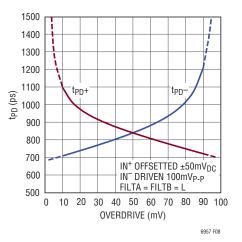

| t <sub>PD</sub>          | Propagation Delay                                                                                                                                                                      | FILTB = L, FILTA = L<br>FILTB = L, FILTA = H<br>FILTB = H, FILTA = L<br>FILTB = H, FILTA = H                                      | •<br>•<br>• | 0.35                                         | 0.5<br>0.6<br>1.1<br>3.2     | 0.7<br>0.8<br>1.3<br>4 | ns<br>ns<br>ns<br>ns             |

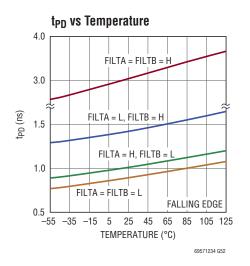

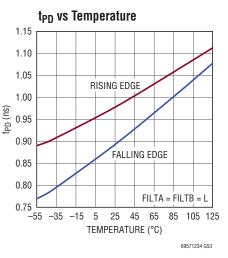

| Δt <sub>PD</sub> /ΔT     | Propagation Delay Variation Over Temperature                                                                                                                                           | $ \begin{array}{l} FILTB = L,  FILTA = L \\ FILTB = L,  FILTA = H \\ FILTB = H,  FILTA = L \\ FILTB = H,  FILTA = H \end{array} $ | •<br>•<br>• |                                              | 0.1<br>0.1<br>0.11<br>0.15   |                        | ps/°C<br>ps/°C<br>ps/°C<br>ps/°C |

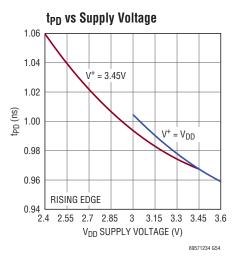

| $\Delta t_{PD}/\Delta V$ | Propagation Delay Variation vs Supply Voltage                                                                                                                                          | FILTB = L, FILTA = L                                                                                                              | ٠           |                                              | 4                            | 50                     | ps/V                             |

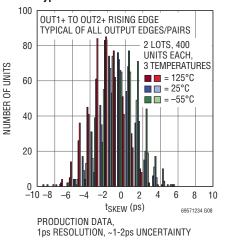

| t <sub>SKEW</sub>        | Output Skew, Differential, CH1 to CH2                                                                                                                                                  |                                                                                                                                   | ٠           |                                              | 3                            | 30                     | ps                               |

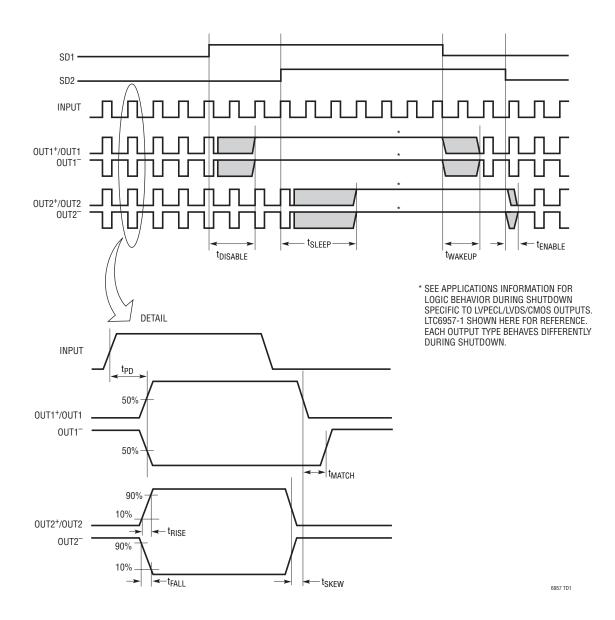

| t <sub>MATCH</sub>       | Output Matching (OUTx+ to OUTx-)                                                                                                                                                       | See Timing Diagram                                                                                                                | ٠           |                                              | 2.5                          | 30                     | ps                               |

| Power                    |                                                                                                                                                                                        |                                                                                                                                   |             |                                              |                              |                        |                                  |

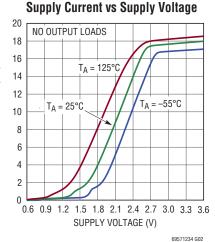

| V+                       | V <sup>+</sup> Operating Supply Voltage Range                                                                                                                                          | $R_{LOAD} = 50\Omega$ to (V <sup>+</sup> - 2V)                                                                                    | ٠           | 3.15                                         | 3.3                          | 3.45                   | V                                |

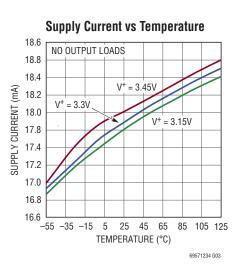

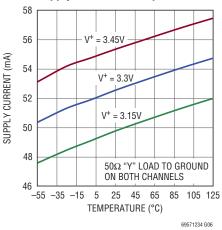

| Is                       | Supply Current<br>Both Outputs Enabled (SD1 = SD2 = L)<br>One Output Enabled (SD1 = L, SD2 = H or SD1 = H, SD2 = L)<br>Both Outputs Disabled (SD1 = SD2 = H)<br>Including Output Loads | No Output Loads<br>No Output Loads<br>No Output Loads<br>$R_{LOAD} = 50\Omega$ to (V <sup>+</sup> – 2V), ×4                       | •           |                                              | 18<br>15<br>0.7<br>58        | 22<br>19<br>1.2<br>72  | mA<br>mA<br>mA<br>mA             |

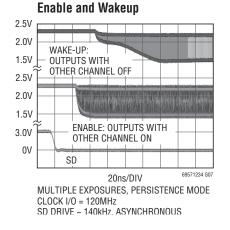

| t <sub>ENABLE</sub>      | Output Enable Time, Other SDx = L                                                                                                                                                      |                                                                                                                                   |             |                                              | 40                           |                        | μs                               |

| t <sub>WAKEUP</sub>      | Output Enable Time, Other SDx = H                                                                                                                                                      |                                                                                                                                   |             |                                              | 120                          |                        | μs                               |

| t <sub>DISABLE</sub>     | Output Disable Time, Other SDx = L                                                                                                                                                     |                                                                                                                                   |             |                                              | 20                           |                        | μs                               |

| t <sub>SLEEP</sub>       | Output Disable Time, Other SDx = H                                                                                                                                                     |                                                                                                                                   |             |                                              | 20                           |                        | μs                               |

**ELECTRICAL CHARACTERISTICS** LTC6957-1 The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 3.3V, SD1 = SD2 = 0.4V, FILTA = FILTB = 0.4V, R<sub>LOAD</sub> = 50 $\Omega$  connected to 1.3V, unless otherwise specified. All voltages are with respect to ground.

| SYMBOL              | PARAMETER                                                                                                                                                                                                                                             | CONDITIONS |   | MIN                  | ТҮР                                                              | MAX | UNITS                                                                                              |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|----------------------|------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------|

|                     |                                                                                                                                                                                                                                                       | CONDITIONS |   | IVIIIN               |                                                                  | шлл | UNITS                                                                                              |

| Digital Lo          | gic Inputs                                                                                                                                                                                                                                            |            |   |                      |                                                                  |     |                                                                                                    |

| VIH                 | High Level SD or FILT Input Voltage                                                                                                                                                                                                                   |            | • | V <sup>+</sup> - 0.4 |                                                                  |     | V                                                                                                  |

| V <sub>IL</sub>     | Low Level SD or FILT Input Voltage                                                                                                                                                                                                                    |            |   |                      |                                                                  | 0.4 | V                                                                                                  |

| I <sub>IN_DIG</sub> | Input Current SD or FILT Pins                                                                                                                                                                                                                         |            |   |                      | 0.1                                                              | ±10 | μA                                                                                                 |

| Additive F          | Phase Noise and Jitter                                                                                                                                                                                                                                |            |   |                      |                                                                  |     | <u> </u>                                                                                           |

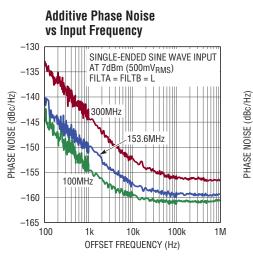

|                     | f <sub>IN</sub> = 300MHz Sine Wave, 7dBm (FILTA = L, FILTB = L)<br>at 10Hz Offset<br>at 10Hz Offset<br>at 1kHz Offset<br>at 10kHz Offset<br>at 100kHz Offset<br>>1MHz Offset<br>Jitter (10Hz to 150MHz)<br>Jitter (12kHz to 20MHz)                    |            |   |                      | -130<br>-140<br>-150<br>-157<br>-157.5<br>-157.5<br>123<br>45    |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub> |

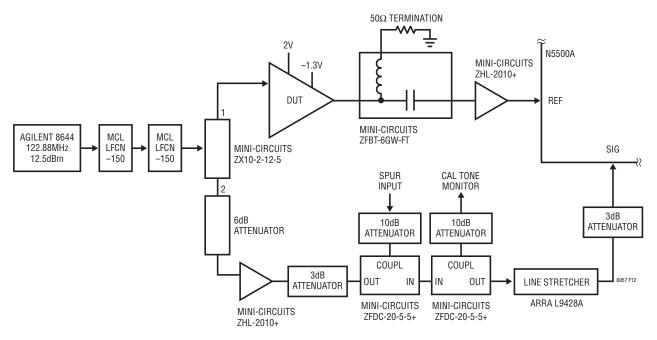

|                     | f <sub>IN</sub> = 122.88MHz Sine Wave, 0dBm (FILTA = H, FILTB = L)<br>at 10Hz Offset<br>at 10Hz Offset<br>at 1kHz Offset<br>at 10kHz Offset<br>at 100kHz Offset<br>>1MHz Offset<br>Jitter (10Hz to 61.44MHz)<br>Jitter (12kHz to 20MHz)               |            |   |                      | -137<br>-146<br>-154.6<br>-157<br>-157.2<br>-157.2<br>200<br>114 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMs</sub>                      |

|                     | $f_{IN} = 100 \text{MHz Sine Wave, } 10 \text{dBm (FILTA = L, FILTB = L)}$<br>at 10 Hz Offset<br>at 10 Hz Offset<br>at 10 Hz Offset<br>at 10 Hz Offset<br>at 10 0 Hz Offset<br>> 1 MHz Offset<br>Jitter (10 Hz to 50 MHz)<br>Jitter (12 Hz to 20 MHz) |            |   |                      | -138<br>-148.1<br>-156.8<br>-160.6<br>-161<br>-161<br>142<br>90  |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub>           |

### ELECTRICAL CHARACTERISTICS LTC6957-2

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 3.3V, SD1 = SD2 = 0.4V, FILTA = FILTB = 0.4V, R<sub>LOAD</sub> = 110 $\Omega$  differential, unless otherwise specified. All voltages are with respect to ground.

| SYMBOL                          | PARAMETER                                                                                                                                                    | CONDITIONS                                                                                                              |   | MIN   | ТҮР                        | MAX                       | UNITS                            |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|-------|----------------------------|---------------------------|----------------------------------|

| Inputs (IN                      | i <sup>-</sup> , IN <sup>+</sup> )                                                                                                                           |                                                                                                                         |   |       |                            |                           |                                  |

| f <sub>IN</sub>                 | Input Frequency Range                                                                                                                                        |                                                                                                                         |   |       |                            | 300                       | MHz                              |

| V <sub>INSE</sub>               | Input Signal Level Range, Single-Ended                                                                                                                       |                                                                                                                         |   | 0.2   | 0.8                        | 2                         | V <sub>P-P</sub>                 |

| VINDIFF                         | Input Signal Level Range, Differential                                                                                                                       |                                                                                                                         |   | 0.2   | 0.8                        | 2                         | V <sub>P-P</sub>                 |

| t <sub>MIN</sub>                | Minimum Input Pulse Width                                                                                                                                    | High or Low                                                                                                             |   |       | 0.5                        |                           | ns                               |

| VINCM                           | Self-Bias Voltage, IN <sup>+</sup> , IN <sup>-</sup>                                                                                                         |                                                                                                                         | • | 1.8   | 2                          | 2.3                       | V                                |

| R <sub>IN</sub>                 | Input Resistance, Differential                                                                                                                               |                                                                                                                         | • | 1.5   | 2                          | 2.5                       | kΩ                               |

| CIN                             | Input Capacitance, Differential                                                                                                                              |                                                                                                                         |   |       | 0.5                        |                           | pF                               |

| BW <sub>IN</sub>                | Input Section Small Signal Bandwidth                                                                                                                         | $      FILTB = L, FILTA = L \\       FILTB = L, FILTA = H \\       FILTB = H, FILTA = L \\       FILTB = H, FILTA = H $ |   |       | 1200<br>500<br>160<br>50   |                           | MHz<br>MHz<br>MHz<br>MHz         |

| Outputs (                       | LVDS)                                                                                                                                                        |                                                                                                                         |   |       |                            |                           |                                  |

| V <sub>OD</sub>                 | Output Differential Voltage                                                                                                                                  |                                                                                                                         |   | 250   | 360                        | 450                       | mV                               |

| $\Delta V_{OD}$                 | Delta V <sub>OD</sub>                                                                                                                                        |                                                                                                                         |   |       | 0.2                        | 50                        | mV                               |

| V <sub>OS</sub>                 | Output Offset Voltage                                                                                                                                        |                                                                                                                         | • | 1.125 | 1.25                       | 1.375                     | V                                |

| $\Delta V_{OS}$                 | Delta V <sub>OS</sub>                                                                                                                                        |                                                                                                                         |   |       | 1.5                        | 50                        | mV                               |

| I <sub>SC</sub>                 | Short-Circuit Current                                                                                                                                        |                                                                                                                         |   |       | 3.9                        | 6                         | mA                               |

| tr                              | Output Rise Time                                                                                                                                             |                                                                                                                         |   |       | 170                        |                           | ps                               |

| t <sub>f</sub>                  | Output Fall Time                                                                                                                                             |                                                                                                                         |   |       | 170                        |                           | ps                               |

| t <sub>PD</sub>                 | Propagation Delay                                                                                                                                            | $      FILTB = L, FILTA = L \\       FILTB = L, FILTA = H \\       FILTB = H, FILTA = L \\       FILTB = H, FILTA = H $ | • | 0.65  | 0.84<br>0.9<br>1.35<br>3.5 | 1.15<br>1.3<br>1.8<br>4.4 | ns<br>ns<br>ns<br>ns             |

| $\Delta t_{PD}/\Delta T$        | Propagation Delay Variation Over Temperature                                                                                                                 | $      FILTB = L, FILTA = L \\       FILTB = L, FILTA = H \\       FILTB = H, FILTA = L \\       FILTB = H, FILTA = H $ | • |       | 0.5<br>0.6<br>0.7<br>1.8   |                           | ps/°C<br>ps/°C<br>ps/°C<br>ps/°C |

| $\Delta t_{\text{PD}}/\Delta V$ | Propagation Delay Variation vs Supply Voltage                                                                                                                | FILTB = L, FILTA = L                                                                                                    | • |       | 5                          | 60                        | ps/V                             |

| t <sub>SKEW</sub>               | Output Skew, Differential, CH1 to CH2                                                                                                                        |                                                                                                                         |   |       | 3                          | 50                        | ps                               |

| Power                           |                                                                                                                                                              |                                                                                                                         |   |       |                            |                           |                                  |

| V <sup>+</sup>                  | V <sup>+</sup> Operating Supply Voltage Range                                                                                                                |                                                                                                                         |   | 3.15  | 3.3                        | 3.45                      | V                                |

| I <sub>S</sub>                  | Supply Current<br>Both Outputs Enabled (SD1 = SD2 = L)<br>One Output Enabled (SD1 = L, SD2 = H or SD1 = H, SD2 = L)<br>Both Outputs Disabled (SD1 = SD2 = H) |                                                                                                                         | • |       | 38<br>26<br>0.7            | 45<br>30<br>1.2           | mA<br>mA<br>mA                   |

| t <sub>ENABLE</sub>             | Output Enable Time, Other SDx = L                                                                                                                            |                                                                                                                         |   |       | 300                        |                           | ns                               |

| t <sub>WAKEUP</sub>             | Output Enable Time, Other SDx = H                                                                                                                            |                                                                                                                         |   |       | 400                        |                           | ns                               |

| t <sub>DISABLE</sub>            | Output Disable Time, Other SDx = L                                                                                                                           |                                                                                                                         |   |       | 40                         |                           | ns                               |

| t <sub>SLEEP</sub>              | Output Disable Time, Other SDx = H                                                                                                                           |                                                                                                                         |   |       | 50                         |                           | ns                               |

**ELECTRICAL CHARACTERISTICS** LTC6957-2 The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = 3.3V, SD1 = SD2 = 0.4V, FILTA = FILTB = 0.4V, R<sub>LOAD</sub> = 110 $\Omega$  differential, unless otherwise specified. All voltages are with respect to ground.

| SYMBOL              | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CONDITIONS |   | MIN                  | ТҮР                                                              | MAX | UNITS                                                                                              |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|----------------------|------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------|

| Digital L           | ogic Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |   |                      |                                                                  |     |                                                                                                    |

| V <sub>IH</sub>     | High Level SD or FILT Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |   | V <sup>+</sup> - 0.4 |                                                                  |     | V                                                                                                  |

| V <sub>IL</sub>     | Low Level SD or FILT Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | • |                      |                                                                  | 0.4 | V                                                                                                  |

| I <sub>IN_DIG</sub> | Input Current SD or FILT Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            | • |                      | 0.1                                                              | ±10 | μA                                                                                                 |

| Additive            | Phase Noise and Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |   |                      |                                                                  |     |                                                                                                    |

|                     | f <sub>IN</sub> = 300MHz Sine Wave, 7dBm (FILTA = L, FILTB = L)<br>10Hz Offset<br>10Hz Offset<br>1kHz Offset<br>10kHz Offset<br>100kHz Offset<br>>1MHz Offset<br>Jitter (10Hz to 150MHz)<br>Jitter (12kHz to 20MHz)                                                                                                                                                                                                                                                                                                                                                                                          |            |   |                      | -124<br>-134<br>-143.5<br>-151.3<br>-154<br>-154<br>183<br>67    |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub> |

|                     | $f_{IN} = 122.88 \text{MHz Sine Wave, 0dBm (FILTA = H, FILTB = L)}$ $10\text{Hz Offset}$ $100\text{Hz Offset}$ $10\text{Hz Offset}$ $10\text{kHz Offset}$ $100\text{kHz Offset}$ $100\text{kHz Offset}$ $310\text{kHz Offset}$ $3100\text{kHz Offset}$ $31000\text{kHz Offset}$ $31000000000000000000000000000000000000$ |            |   |                      | -132.5<br>-142.5<br>-150.7<br>-156<br>-157<br>-157<br>203<br>116 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub>           |

|                     | $f_{IN} = 100 \text{MHz Sine Wave, } 10 \text{dBm (FILTA = L, FILTB = L)} \\ 10 \text{Hz Offset} \\ 100 \text{Hz Offset} \\ 10 \text{Hz Offset} \\ 10 \text{kHz Offset} \\ 100 \text{kHz Offset} \\ 100 \text{kHz Offset} \\ >10 \text{HZ Offset} \\ \text{Jitter (10 \text{Hz to 50 MHz})} \\ \text{Jitter (12 \text{kHz to 20 MHz})} \end{cases}$                                                                                                                                                                                                                                                          |            |   |                      | -132<br>-142<br>-151<br>-157.5<br>-159.5<br>-159.5<br>169<br>107 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub>           |

**ELECTRICAL CHARACTERISTICS** LTC6957-3/LTC6957-4 The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = V<sub>DD</sub> = 3.3V, SD1 = SD2 = 0.4V, FILTA = FILTB = 0.4V, R<sub>LOAD</sub> = 480 $\Omega$  to V<sub>DD</sub>/2, unless otherwise specified. All voltages are with respect to ground.

| SYMBOL                   | PARAMETER                                                                                                                                                           | CONDITIONS                                                                                   |   | MIN                                            | ТҮР                      | MAX                      | UNITS                            |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---|------------------------------------------------|--------------------------|--------------------------|----------------------------------|

| Inputs (IN               | √−, IN+)                                                                                                                                                            |                                                                                              |   |                                                |                          |                          | <u> </u>                         |

| f <sub>IN</sub>          | Input Frequency Range                                                                                                                                               |                                                                                              | ٠ |                                                |                          | 300                      | MHz                              |

| V <sub>INSE</sub>        | Input Signal Level Range, Single-Ended                                                                                                                              |                                                                                              | ٠ | 0.2                                            | 0.8                      | 2                        | V <sub>P-P</sub>                 |

| VINDIFF                  | Input Signal Level Range, Differential                                                                                                                              |                                                                                              | ٠ | 0.2                                            | 0.8                      | 2                        | V <sub>P-P</sub>                 |

| t <sub>MIN</sub>         | Minimum Input Pulse Width                                                                                                                                           | High or Low                                                                                  |   |                                                | 0.6                      |                          | ns                               |

| VINCM                    | Self-Bias Voltage, IN <sup>+</sup> , IN <sup>-</sup>                                                                                                                |                                                                                              | ٠ | 1.8                                            | 2                        | 2.3                      | V                                |

| R <sub>IN</sub>          | Input Resistance, Differential                                                                                                                                      |                                                                                              | ٠ | 1.5                                            | 2                        | 2.5                      | kΩ                               |

| CIN                      | Input Capacitance, Differential                                                                                                                                     |                                                                                              |   |                                                | 0.5                      |                          | pF                               |

| BW <sub>IN</sub>         | Input Section Small Signal Bandwidth                                                                                                                                | FILTB = L, FILTA = L<br>FILTB = L, FILTA = H<br>FILTB = H, FILTA = L<br>FILTB = H, FILTA = H |   |                                                | 1200<br>500<br>160<br>50 |                          | MHz<br>MHz<br>MHz<br>MHz         |

| Outputs (                | CMOS)                                                                                                                                                               |                                                                                              |   |                                                |                          |                          |                                  |

| V <sub>OH</sub>          | Output High Voltage                                                                                                                                                 | No Load<br>–3mA Load                                                                         | • | V <sub>DD</sub> - 0.1<br>V <sub>DD</sub> - 0.2 |                          |                          | V<br>V                           |

| V <sub>OL</sub>          | Output Low Voltage                                                                                                                                                  | No Load<br>3mA Load                                                                          | • |                                                |                          | 0.1<br>0.2               | V<br>V                           |

| t <sub>r</sub>           | Output Rise Time                                                                                                                                                    |                                                                                              |   |                                                | 320                      |                          | ps                               |

| t <sub>f</sub>           | Output Fall Time                                                                                                                                                    |                                                                                              |   |                                                | 300                      |                          | ps                               |

| t <sub>PD</sub>          | Propagation Delay                                                                                                                                                   | FILTB = L, FILTA = L<br>FILTB = L, FILTA = H<br>FILTB = H, FILTA = L<br>FILTB = H, FILTA = H | • | 0.8                                            | 0.95<br>1<br>1.5<br>3.6  | 1.6<br>1.8<br>2.4<br>4.8 | ns<br>ns<br>ns<br>ns             |

| $\Delta t_{PD}/\Delta T$ | Propagation Delay Variation Over Temperature                                                                                                                        | FILTB = L, FILTA = L<br>FILTB = L, FILTA = H<br>FILTB = H, FILTA = L<br>FILTB = H, FILTA = H | • |                                                | 1.7<br>1.7<br>2<br>3     |                          | ps/°C<br>ps/°C<br>ps/°C<br>ps/°C |

| $\Delta t_{PD}/\Delta V$ | Propagation Delay Variation vs Supply Voltage                                                                                                                       | $FILTB = FILTA = L, V^+ = V_{DD}$                                                            | ٠ |                                                | 100                      | 200                      | ps/V                             |

| t <sub>SKEW</sub>        | Output Skew, CH1 to CH2<br>LTC6957-3<br>LTC6957-4                                                                                                                   |                                                                                              | • |                                                | 5<br>120                 | 35<br>250                | ps<br>ps                         |

| Power                    | <u>^</u>                                                                                                                                                            |                                                                                              |   |                                                |                          |                          |                                  |

| V+                       | V <sup>+</sup> Operating Supply Voltage Range                                                                                                                       |                                                                                              | ٠ | 3.15                                           | 3.3                      | 3.45                     | V                                |

| V <sub>DD</sub>          | V <sub>DD</sub> Operating Supply Voltage Range                                                                                                                      | $V_{DD}$ Must Be $\leq V^+$                                                                  | ٠ | 2.4                                            | 3.3                      | 3.45                     | V                                |

| IS                       | Supply Current, Pin 2<br>Both Outputs Enabled (SD1 = SD2 = L)<br>One Output Enabled (SD1 = L, SD2 = H or SD1 = H, SD2 = L)<br>Both Outputs Disabled (SD1 = SD2 = H) |                                                                                              | • |                                                | 24<br>24<br>0.7          | 27.5<br>27.5<br>1.2      | mA<br>mA<br>mA                   |

| I <sub>DD</sub>          | Supply Current, Pin 11, No Load                                                                                                                                     | Static<br>Dynamic, per Output                                                                | • |                                                | 0.001<br>0.056           | 0.01<br>0.07             | mA<br>mA/MHz                     |

| t <sub>enable</sub>      | Output Enable Time, Other SDx = L                                                                                                                                   |                                                                                              |   |                                                | 200                      |                          | ns                               |

| t <sub>WAKEUP</sub>      | Output Enable Time, Other SDx = H                                                                                                                                   |                                                                                              |   |                                                | 300                      |                          | ns                               |

| t <sub>disable</sub>     | Output Disable Time, Other SDx = L                                                                                                                                  |                                                                                              |   |                                                | 20                       |                          | ns                               |

| t <sub>SLEEP</sub>       | Output Disable Time, Other SDx = H                                                                                                                                  |                                                                                              |   |                                                | 20                       |                          | ns                               |

### ELECTRICAL CHARACTERISTICS LTC6957-3/LTC6957-4

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sup>+</sup> = V<sub>DD</sub> = 3.3V, SD1 = SD2 = 0.4V, FILTA = FILTB = 0.4V, R<sub>LOAD</sub> = 480 $\Omega$  to V<sub>DD</sub>/2, unless otherwise specified. All voltages are with respect to ground.

| SYMBOL              | PARAMETER                                                                                                                                                                                                                                                                                                                                          | CONDITIONS |   | MIN                  | ТҮР                                                                | MAX | UNITS                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---|----------------------|--------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------|

| Digital L           | ogic Inputs                                                                                                                                                                                                                                                                                                                                        |            |   |                      |                                                                    | -   |                                                                                                    |

| V <sub>IH</sub>     | High Level SD or Filt Input Voltage                                                                                                                                                                                                                                                                                                                |            | ٠ | V <sup>+</sup> - 0.4 |                                                                    |     | V                                                                                                  |

| V <sub>IL</sub>     | Low Level SD or Filt Input Voltage                                                                                                                                                                                                                                                                                                                 |            | ٠ |                      |                                                                    | 0.4 | V                                                                                                  |

| I <sub>IN DIG</sub> | Input Current SD or Filt Pins                                                                                                                                                                                                                                                                                                                      |            | ٠ |                      | 0.1                                                                | ±10 | μA                                                                                                 |

| Additive            | Phase Noise and Jitter                                                                                                                                                                                                                                                                                                                             |            |   |                      |                                                                    |     |                                                                                                    |

|                     | f <sub>IN</sub> = 300MHz Sine Wave, 7dBm (FILTA = L, FILTB = L)<br>10Hz Offset<br>10Hz Offset<br>1kHz Offset<br>10kHz Offset<br>100kHz Offset<br>>1MHz Offset<br>Jitter (10Hz to 150MHz)<br>Jitter (12kHz to 20MHz)                                                                                                                                |            |   |                      | -123<br>-133<br>-143<br>-152<br>-156<br>-156<br>146<br>53          |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub> |

|                     | $f_{IN} = 122.88 \text{MHz Sine Wave, 0dBm (FILTA = H, FILTB = L)} \\ 10 \text{Hz Offset} \\ 100 \text{Hz Offset} \\ 1k \text{Hz Offset} \\ 10k \text{Hz Offset} \\ 100k \text{Hz Offset} \\ >100k \text{Hz Offset} \\ >10 \text{Hz Offset} \\ Jitter (10 \text{Hz to } 61.44 \text{MHz}) \\ Jitter (12k \text{Hz to } 20 \text{MHz}) \end{cases}$ |            |   |                      | -132<br>-142<br>-150.6<br>-156.5<br>-157.4<br>-157.4<br>192<br>109 |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub> |

|                     | $f_{IN} = 100 \text{MHz Sine Wave, 10dBm (FILTA = L, FILTB = L)} \\ 10 \text{Hz Offset} \\ 100 \text{Hz Offset} \\ 1 \text{kHz Offset} \\ 10 \text{kHz Offset} \\ 100 \text{kHz Offset} \\ > 10 \text{kHz Offset} \\ > 10 \text{Hz Offset} \\ \text{Jitter (10 \text{Hz to 50 \text{MHz})} \\ Jitter (12 \text{kHz to 20 \text{MHz})} \end{cases}$ |            |   |                      | -135<br>-145<br>-153<br>-159.8<br>-161<br>-161<br>142<br>90        |     | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>fs <sub>RMS</sub><br>fs <sub>RMS</sub> |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Input pins IN<sup>+</sup>, IN<sup>-</sup>, FILTA, FILTB, SD1 and SD2 are protected by steering diodes to either supply. If the inputs go beyond either supply rail, the input current should be limited to less than 10mA. If pushing current into FILTB, the Pin 6 voltage must be limited to 4V. On the logic pins (FILTA, FILTB, SD1 and SD2) the Absolute Maximum input current applies

only at the maximum operating supply voltage of 3.45V; 10mA of input current with the absolute maximum supply voltage of 3.6V may create permanent damage from voltage stress.

**Note 3:** With 3.6V Absolute Maximum supply voltage, the LTC6957-3/ LTC6957-4 CMOS outputs can sink 30mA while low, and source 30mA while high without damage. However, if overdriven or subject to an inductive load kick outside the supply rails, 30mA can create damaging voltage stress and is not guaranteed unless V<sub>DD</sub> is limited to 3.15V.

2.4

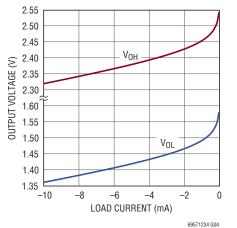

**Output Voltage vs Load Current**

V<sup>+</sup> = 3.3V  $50\Omega$  LOADS TO 1.3V V<sub>OH</sub>

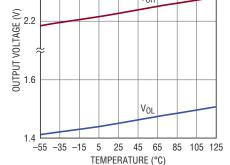

**Output Voltage vs Temperature**

69571234 G05

#### **Supply Current vs Temperature**

**Typical Distribution of Skew**

<sup>6957</sup>fb

69571234 G36

SUPPLY VOLTAGE (V)

TEMPERATURE (°C)

69571234 G35

TEMPERATURE (°C)

69571234 G34

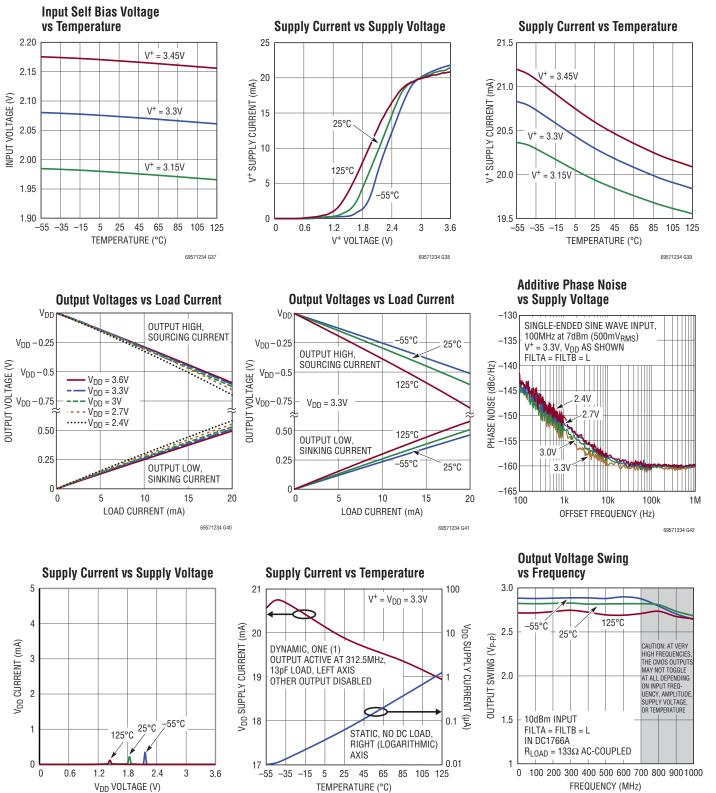

### TYPICAL PERFORMANCE CHARACTERISTICS LTC6957-3/LTC6957-4

69571234 G43

69571234 G44

### TYPICAL PERFORMANCE CHARACTERISTICS LTC6957-3/LTC6957-4

-130

-135

-140

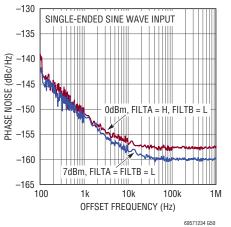

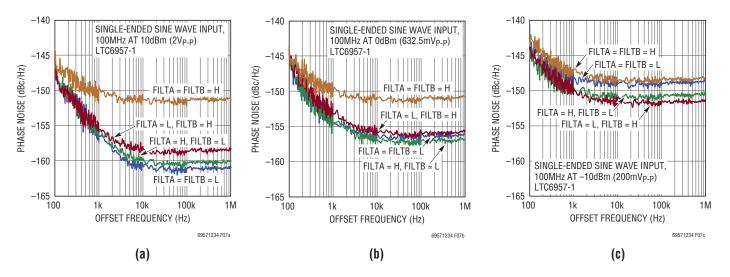

**Additive Phase Noise**

SINGLE-ENDED 100MHz SINE WAVE INPUT

SEE APPLICATIONS INFORMATION

vs Amplitude

–10dBm, FILTA = L, FILTB = H -145 0dBm, FILTA = H, FILTB = L -150-155 -160 10dBm. FILTA = FILTB = L -165 100 10k 100k 1k OFFSET FREQUENCY (Hz) 69571234 G46

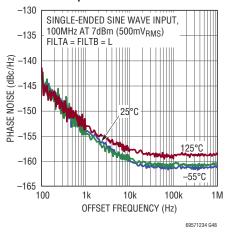

#### Additive Phase Noise vs Temperature

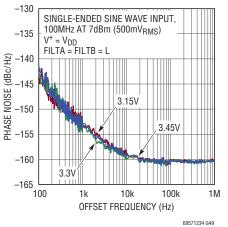

**Additive Phase Noise** vs Supply Voltage

Additive Phase Noise at 122.88MHz

1M

69571234 G47

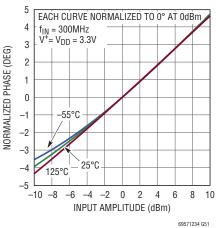

#### AM to PM Conversion

### PIN FUNCTIONS

**FILTA, FILTB (Pin 1, Pin 6):** Input Bandwidth Limiting Control. These CMOS logic inputs control the bandwidth of the early amplifier stages. For slow slewing signals substantially lower phase noise is achieved by using this feature. See the Applications Information section for more details.

V<sup>+</sup> (Pin 2): Supply Voltage (3.15V to 3.45V). This supply must be kept free from noise and ripple. It should be bypassed directly to GND (Pin 5) with a  $0.1\mu$ F capacitor.

**IN<sup>+</sup>, IN<sup>-</sup> (Pin 3, Pin 4):** Input Signal Pins. These inputs are differential, but can also interface with single-ended signals. The input can be a sine wave signal or a CML, LVPECL, TTL or CMOS logic signal. See the Applications Information section for more details.

**GND (Pin 5):** Ground. Connect to a low inductance ground plane for best performance. The connection to the bypass capacitor for V<sup>+</sup> (Pin 2) should be through a direct, low inductance path.

**SD1, SD2 (Pin 12, Pin 7):** Output Enable Control. These CMOS logic inputs control the enabling and disabling of their respective OUT1 and OUT2 outputs. When both outputs are disabled, the LTC6957 is placed in a low power shutdown state.

### LTC6957-1 Only

**OUT1<sup>-</sup>**, **OUT1<sup>+</sup>** (**Pin10**, **Pin11**): LVPECL Outputs. Differential logic outputs typically terminated by  $50\Omega$  connected to a supply 2V below the V<sup>+</sup> supply. Refer to the Applications Information section for more details.

**OUT2<sup>-</sup>, OUT2<sup>+</sup> (Pin 9, Pin 8):** LVPECL Outputs. Differential logic outputs typically terminated by  $50\Omega$  connected to a supply 2V below the V<sup>+</sup> supply. Refer to the Applications Information section for more details.

### LTC6957-2 Only

**OUT1<sup>-</sup>, OUT1<sup>+</sup> (Pin 10, Pin 11):** LVDS Outputs, Mostly TIA/EIA-644-A Compliant. Refer to the Applications Information section for more details.

**OUT2<sup>-</sup>, OUT2<sup>+</sup> (Pin 9, Pin 8):** LVDS Outputs, Mostly TIA/EIA-644-A Compliant. Refer to the Applications Information section for more details.

### LTC6957-3/LTC6957-4 Only

**OUT1, OUT2 (Pin 10, Pin 9):** CMOS Outputs. Refer to the Applications Information section for more details.

$V_{DD}$  (Pin 11): Output Supply Voltage (2.4V to 3.45V). For best performance connect this to the same supply as V<sup>+</sup> (Pin 2). If the output needs to be a lower logic rail, this supply can be separately connected, but this voltage must be less than or equal to that on Pin 2 for proper operation. This supply must also be kept free from noise and ripple. It should be bypassed directly to the GNDOUT pin (Pin 8) with a 0.1µF capacitor.

**GNDOUT (Pin 8):** Output Logic Ground. Tie to a low inductance ground plane for best performance. The connection to the bypass capacitor for  $V_{DD}$  (Pin 11) should be through a direct, low inductance path.

### LTC6957-xDD Only

**Exposed Pad (Pin 13):** Always tie the underlying DFN exposed pad to GND (Pin 5). To achieve the rated  $\theta_{JA}$  of the DD package, there should be good thermal contact to the PCB.

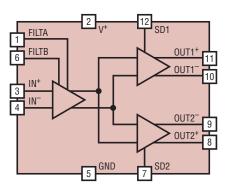

### **BLOCK DIAGRAMS**

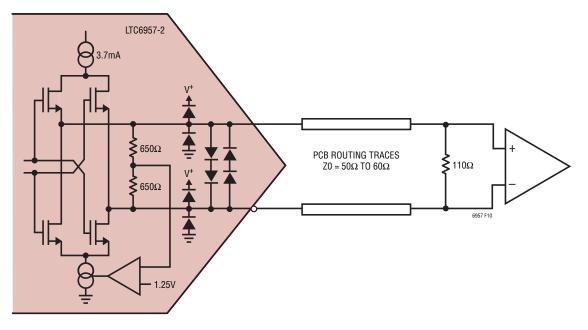

LTC6957-1 and LTC6957-2

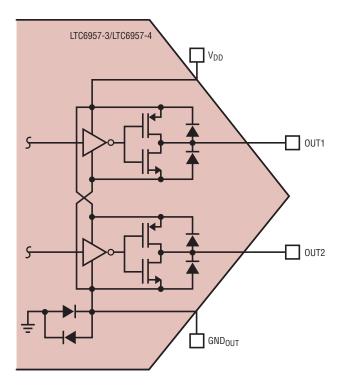

LTC6957-3 and LTC6957-4

## TIMING DIAGRAM

#### **General Considerations**

The LTC6957-1/LTC6957-2/LTC6957-3/LTC6957-4 are low noise, dual output clock buffers that are designed for demanding, low phase noise applications. Properly applied, they can preserve phase noise performance in situations where alternative solutions would degrade the phase noise significantly. They are also useful as logic converters.

However, no buffer device is capable of removing or reducing phase noise present on an input signal. As with most low phase noise circuits, improper application of the LTC6957-1/LTC6957-2/LTC6957-3/LTC6957-4 can result in an increase in the phase noise through a variety of mechanisms. The information below will, hopefully, allow a designer to avoid such an outcome.

The LTC6957 is designed to be used with high performance clock signals destined for driving the encode inputs of ADCs or mixer inputs. Such clocks should not be treated as digital signals. The beauty of digital logic is that there is noise margin both in the voltage and the timing, before any deleterious effects are noticed. In contrast, high performance clock signals have no margin for error in the timing before the system performance is degraded. Users are encouraged to keep this distinction in mind while designing the entire clocking signal chain before, during, and after the LTC6957.

#### **Input Interfacing**

The input stage is the same for all versions of the LTC6957 and is designed for low noise and ease of interfacing to sine-wave and small amplitude signals. Other logic types can interface directly, or with little effort since they present a smaller challenge for noise preservation.

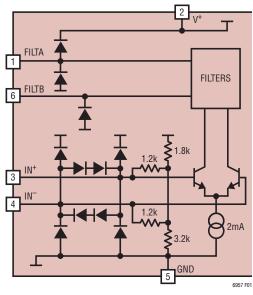

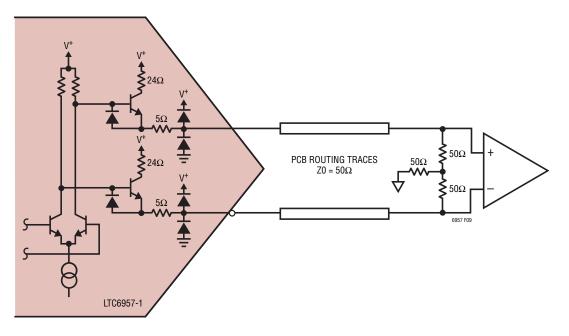

Figure 1 shows a simplified schematic of the LTC6957 input stage. The diodes are all for protection, both during ESD events and to protect the low noise NPN devices from being damaged by input overdrive.

The resistors are to bias the input stage at an optimal DC level, but they are too large to leave floating without increasing the noise. Therefore, for low noise use, always connect both inputs to a low AC impedance. A capacitor to ground/return is imperative on the unused input in single-ended applications.

Figure 1

6957fb

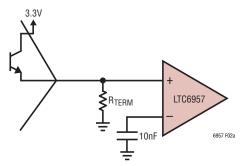

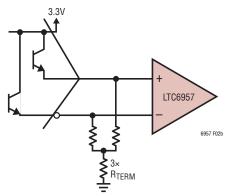

Figure 2a shows how to interface single-ended LVPECL logic to the LTC6957, while Figure 2b shows how to drive the LTC6957 with differential LVPECL signals. The capacitors shown are 10nF and can be inexpensive ceramics, preferably in small SMT cases. For use above 100MHz, lower value capacitors may be desired to avoid series resonance, which could increase the noise in Figure 2a even though the capacitor is just on the DC input. This comment applies to all capacitors hooked to the inputs throughout this data sheet.

In Figure 2a, the R<sub>TERM</sub> implementation is up to the user and is to terminate the transmission line. If it is connected to a V<sub>TT</sub> that is passively generated and heavily bypassed to ground, the 10nF to ground shown on the inverting LTC6957 input is the appropriate connection to use. However, if the termination goes to an actively generated V<sub>TT</sub> voltage, lower noise may be achieved by connecting the capacitor on the inverting input to that V<sub>TT</sub> rather than ground.

Figure 2a. Single-Ended LVPECL Input

Figure 2b. Differential LVPECL Input

In Figure 2b, both inputs to the LTC6957 are driven, increasing the differential input signal size and minimizing noise from any common mode source such as  $V_{TT},$  both of which improve the achievable phase noise.

A variety of termination techniques can be used, and as long as the two sides use the same termination, the configuration used won't matter much. In Figure 2b, the  $R_{TERM}$ s are shown in a "Y" configuration that creates a passive  $V_{TT}$  at the common point. Most 3.3V LVPECL devices have differential outputs and can be terminated with three 50 $\Omega$  resistors as shown.

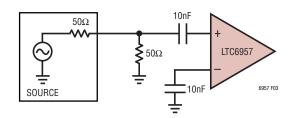

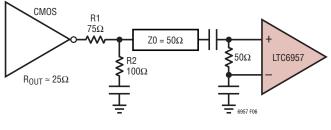

Figure 3 shows a  $50\Omega$  RF signal source interface to the LTC6957. For a pure tone (sine wave) input, Figure 3 can handle up to 10dBm maximum. A broadband  $50\Omega$  match as shown should suffice for most applications, though for small amplitude input signals a narrow band reactive matching network may offer incremental improvements in performance.

Figure 3. Single-Ended 50  $\Omega$  Input Source

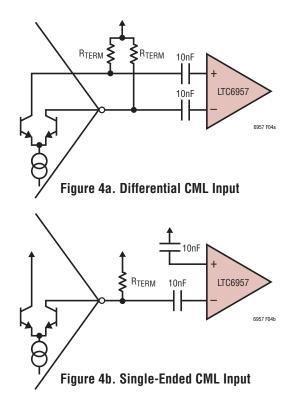

Figure 4 shows the interface between current mode logic (CML) signals and the LTC6957 inputs. The specifics of terminating will be dependent on the particular CML driver used; Figure 4 shows terminations only at the load end of the line, but the same LTC6957 interface is appropriate for applications with the source end of the line also terminated. In Figure 4a, a differential signal interface to the LTC6957 is shown, which must be AC-coupled due to the DC input levels required at the LTC6957.

Figure 4b shows a single-ended CML signal driving the LTC6957. This is not commonly used because of noise and immunity weaknesses compared to the differential CML case. Because the signal is created by a current pulled through the termination resistor, the signal is inherently referenced to the supply voltage to which R<sub>TERM</sub> is tied. For that reason, the other LTC6957 should be AC-referenced to that supply voltage as shown.

The polarity change shown here is for graphic clarity only, and can be reversed by swapping the LTC6957 input terminals.

Figure 4

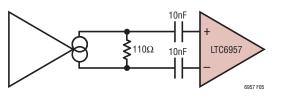

Figure 5 shows the LTC6957 being driven by an LVDS (EIA-644-A) signal pair. This is simply a matter of differentially terminating the pair and AC-coupling as shown into the LTC6957 whose DC common mode voltage is incompatible with the LVDS standard.

Figure 5. LVDS Input

The choice of  $110\Omega$  versus  $100\Omega$  termination is arbitrary (the EIA-644-A standard allows  $90\Omega$  to  $132\Omega$ ) and should be made to match the differential impedance of the trace pair. The termination and AC-coupling elements should be located as close as possible to the LTC6957.

If DC-coupling is desired, for example to control the LTC6957 output phasing during times the LVDS input clocks will be halted, a pair of 3k resistors can parallel the two capacitors in Figure 5. An EIA/TIA-644-A compliant driver can drive this load, which is less load stress than specification 4.1.1. The differential voltage into the LTC6957 when clocked (>100kHz) will be full LVDS levels. When the clocks stop, the DC differential voltage created by the resistors and the 1.2k internal resistors (Figure 1) will be 100mV, still sufficient to assure the desired LTC6957 output polarity. Choosing the smallest capacitors needed for phase noise performance will minimize the settling transients when the clocks restart.

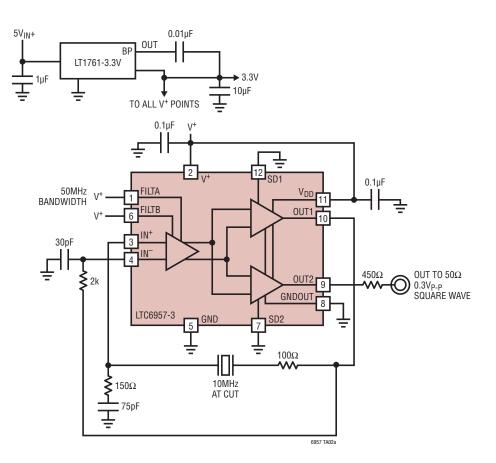

### Interfacing with CMOS Logic