# FEATURES

- Allows Safe Board Insertion into Live Backplane

- Wide Operating Voltage Range: 6.5V to 80V

- Drives Two Gates for High Power Applications

- Configurable Parallel, Staged Start or Single MOSFET Modes

- Adjustable Precision Current Limit: 6mV to 20mV

- Current Foldback Limits MOSFET Power

- SOA Timer Optimizes MOSFET Capability

- Monitors V<sub>GS</sub> and V<sub>DS</sub> for MOSFET Health

- 12V Gate Drive for Lower MOSFET R<sub>DS(ON)</sub>

- Parallelable Controllers for Very High Current Levels

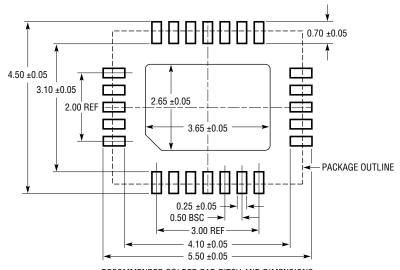

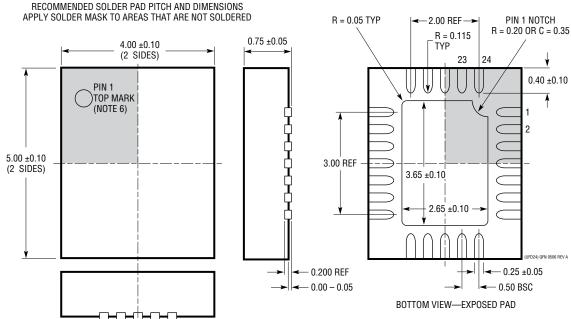

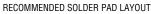

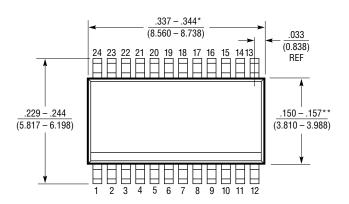

- Available in 24-Lead Narrow SSOP and 24-Pin 4mm × 5mm QFN Packages

### **APPLICATIONS**

- Live Board Insertion in 12V, 24V and 48V Systems

- Industrial High Side Switch/Circuit Breaker

- Computers, Servers

- Vehicle Electrical Systems

# High Voltage High Current Hot Swap Controller

### DESCRIPTION

The LTC®4238 is a high voltage high current Hot Swap controller that allows a board to be safely inserted and removed from a live backplane. Dual 12V gate drive is well suited for high power applications to either share safe operating area across parallel MOSFETs or support a 2-stage start-up that first charges the load capacitance followed by enabling a low on-resistance path to the load.

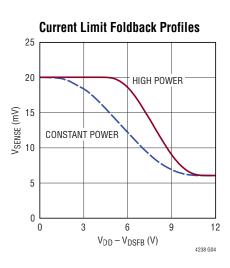

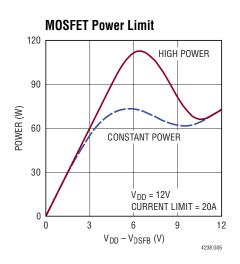

The device features active current limiting (ACL) with two foldback options as  $V_{DS}$  increases. The constant power profile limits the power dissipation to be no higher than a fixed value, while the high power profile allows the part to ride through large input steps during operation.

The LTC4238 notifies when output power is good. In addition, it has protection features that respond to input undervoltage, overvoltage; and generate a fault when there is an overcurrent or FET bad condition.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 9634480, 9634481, 9671465B2, 10003190B2. More patents pending.

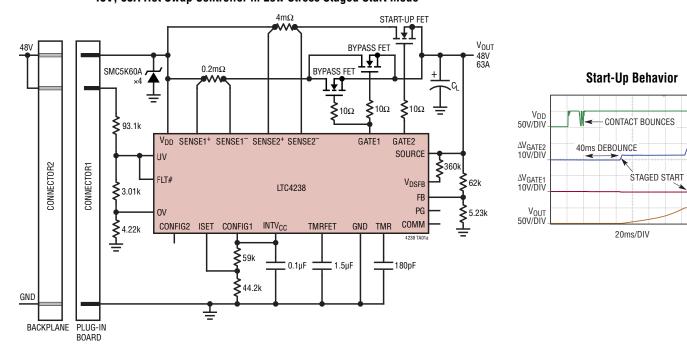

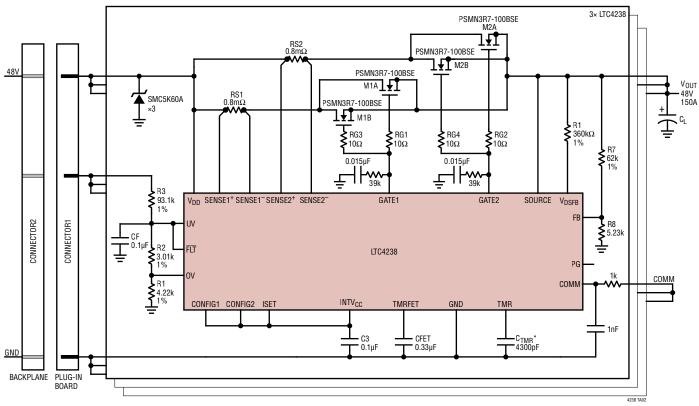

### TYPICAL APPLICATION

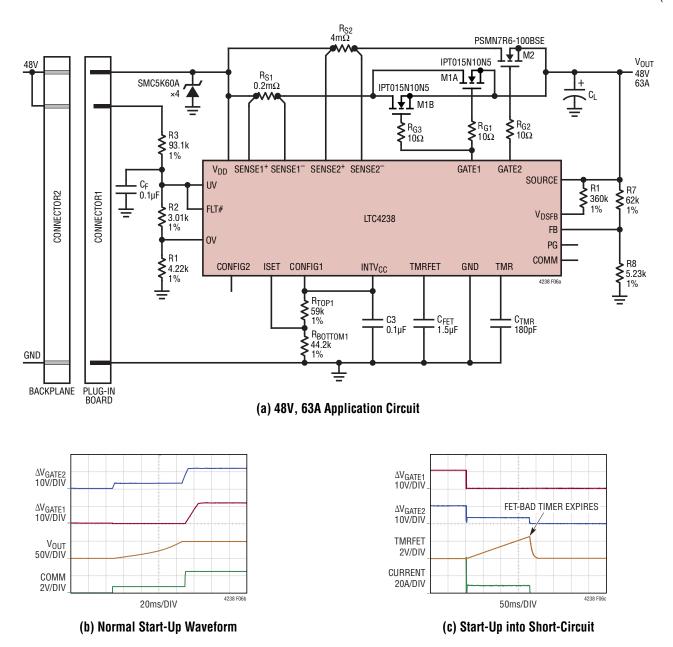

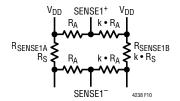

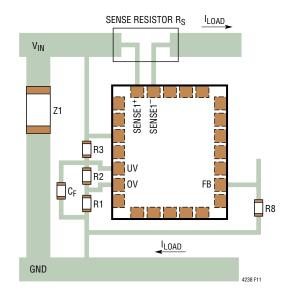

48V, 63A Hot Swap Controller in Low Stress Staged Start Mode

# **ABSOLUTE MAXIMUM RATINGS** (Notes 1 and 2)

| Supply Voltages                                                   |

|-------------------------------------------------------------------|

| V <sub>DD</sub> –0.3V to 100V                                     |

| INTV <sub>CC</sub> 0.3V to 5.5V                                   |

| Input Voltages                                                    |

| GATE – SOURCE (Note 3) –0.3V to 10V                               |

| SENSE1+, SENSE1-, SENSE2+,                                        |

| SENSE2 $^{-}$ V <sub>DD</sub> $- 4.5$ V to V <sub>DD</sub> + 0.3V |

| SOURCE, FB, OV, UV,0.3V to 100V                                   |

| $V_{DSFB}$ 0.3V to $V_{DD}$ +0.3V                                 |

| TMR, TMRFET, ISET, CONFIG1,                                       |

| CONFIG20.3V to INTV <sub>CC</sub> + 0.3V                          |

|                                                                   |

| Output Voltages                      |                |

|--------------------------------------|----------------|

| GATE, PG, FLT#                       | 0.3V to 100V   |

| COMM                                 | 0.3V to 5.5V   |

| Output Currents                      |                |

| INTV <sub>CC</sub>                   | 10mA           |

| Operating Junction Temperature Range |                |

| LTC4238C                             | 0°C to 70°C    |

| LTC4238I                             | 40°C to 85°C   |

| LTC4238H                             | -40°C to 125°C |

| Storage Temperature Range            |                |

| GN Package                           | -65°C to 150°C |

| UFD Package                          | -65°C to 125°C |

| Lead Temperature (Soldering, 10 sec) | 300°C          |

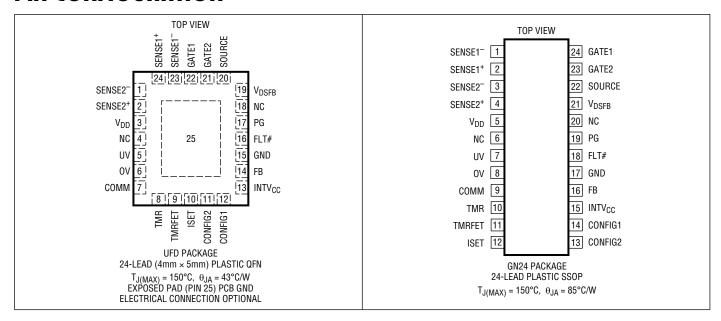

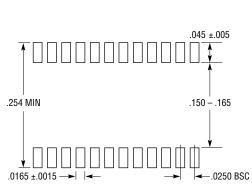

### PIN CONFIGURATION

# ORDER INFORMATION

| TUBE            | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-----------------|-------------------|---------------|---------------------------------|-------------------|

| LTC4238CUFD#PBF | LTC4238CUFD#TRPBF | 4238          | 24-Lead (4mm × 5mm) Plastic QFN | 0°C to 70°C       |

| LTC4238IUFD#PBF | LTC4238IUFD#TRPBF | 4238          | 24-Lead (4mm × 5mm) Plastic QFN | -40°C to 85°C     |

| LTC4238HUFD#PBF | LTC4238HUFD#TRPBF | 4238          | 24-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC4238CGN#PBF  | LTC4238CGN#TRPBF  | LTC4238GN     | 24-Lead Plastic SSOP            | 0°C to 70°C       |

| LTC4238IGN#PBF  | LTC4238IGN#TRPBF  | LTC4238GN     | 24-Lead Plastic SSOP            | -40°C to 85°C     |

| LTC4238HGN#PBF  | LTC4238HGN#TRPBF  | LTC4238GN     | 24-Lead Plastic SSOP            | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD} = 48V$ unless otherwise noted.

| SYMBOL                              | PARAMETER                                                               | CONDITIONS                                                          |   | MIN         | TYP      | MAX         | UNITS    |

|-------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|---|-------------|----------|-------------|----------|

| Power Supply                        |                                                                         |                                                                     |   |             |          |             |          |

| $\overline{V_{DD}}$                 | Input Supply Range                                                      |                                                                     | • | 6.5         |          | 80          | V        |

| $I_{DD}$                            | Input Supply Current                                                    |                                                                     | • |             | 3        | 5           | mA       |

| $\overline{V_{DD(UVLO)}}$           | Input Supply Undervoltage Lockout                                       | V <sub>DD</sub> Rising                                              | • | 5.8         | 6        | 6.2         | V        |

| V <sub>DD(HYST)</sub>               | Input Supply Undervoltage Lockout Hysteresis                            |                                                                     | • |             | 500      |             | mV       |

| INTV <sub>CC</sub>                  | Internal 5V Supply Voltage                                              | I <sub>LOAD</sub> = 0mA to 10mA                                     | • | 4.5         | 5.0      | 5.5         | V        |

| INTV <sub>CC(UVLO)</sub>            | INTV <sub>CC</sub> Undervoltage Lockout Threshold                       | INTV <sub>CC</sub> Rising                                           | • | 3.75        | 4        | 4.25        | V        |

| INTV <sub>CC(HYST)</sub>            | INTV <sub>CC</sub> Undervoltage Lockout Hysteresis                      |                                                                     | • |             | 110      |             | mV       |

| Current Limit                       |                                                                         |                                                                     |   |             |          |             | •        |

| $\Delta V_{SNS(TH)}$                | Current Limit Sense Voltage Threshold (SENSE+ – SENSE-)                 | ISET= 0V<br>ISET = INTV <sub>CC</sub>                               | • | 5.8<br>19.5 | 6<br>20  | 6.2<br>20.5 | mV<br>mV |

|                                     | 10% Current Limit Foldback, Start-Up Only                               | ISET = 0V<br>ISET = INTV <sub>CC</sub>                              | • | 0.18<br>1.6 | 0.6<br>2 | 0.9<br>2.4  | mV<br>mV |

|                                     | 30% Current Limit Foldback, Normal                                      | $V_{DD} - V_{DSFB} = 12V$<br>ISET = 0V<br>ISET = INTV <sub>CC</sub> | • | 1.5<br>5.6  | 1.8<br>6 | 2.1<br>6.4  | mV<br>mV |

|                                     | Current Limit Threshold DAC INL                                         |                                                                     | • |             | 0        | ±60         | μV       |

| $\Delta V_{SNS1} - \Delta V_{SNS2}$ | Current Limit Channel Voltage Mismatch                                  | $V_{SENSE1}+, V_{SENSE2}+=48V$                                      | • |             | 0        | ±300        | μV       |

| α <sub>ILIM</sub> (FAST)            | Ratio of Fast Current Limit to Nominal $\Delta V_{SNS(TH)}$             |                                                                     | • | 2           | 3        | 4           |          |

| I <sub>SENSE1</sub> +               | SENSE1+ Input Current                                                   | $V_{SENSE1}$ + = 48V, $V_{SNS1} \le 20$ mV                          | • | 0           |          | 150         | μA       |

| I <sub>SENSE1</sub> -               | SENSE1 <sup>-</sup> Input Current,                                      | HSSS Mode with CH2 Off                                              | • | 3           | 5        | 7           | μA       |

| _                                   | $V_{SENSE1}$ = $V_{SENSE2}$ = 48V                                       | Parallel, LSSS Mode, HSSS Mode with CH2 On                          | • |             | 0        | ±1          | μА       |

| I <sub>SENSE2</sub> +               | SENSE2+ Input Current                                                   | V <sub>SENSE2</sub> + = 48V                                         | • | 0           |          | 70          | μA       |

| I <sub>SENSE2</sub> -               | SENSE2 <sup>-</sup> Input Current                                       | V <sub>SENSE2</sub> + = V <sub>SENSE2</sub> - = 48V                 | • |             | 0        | ±1          | μA       |

| Gate Drive                          |                                                                         |                                                                     |   |             |          |             |          |

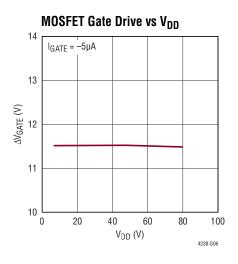

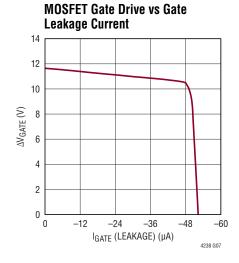

| $\Delta V_{GATE}$                   | External N-Channel Gate Drive (V <sub>GATE</sub> –V <sub>SOURCE</sub> ) | $V_{DD} = 6.5V \text{ to } 80V, I_{GATE} = -5\mu\text{A (Note 3)}$  | • | 10          | 12       | 14          | V        |

| $\Delta V_{GATE(TH)}$               | Gate Threshold for FET-Bad and Power Good                               |                                                                     | • | 6           | 8        | 10          | V        |

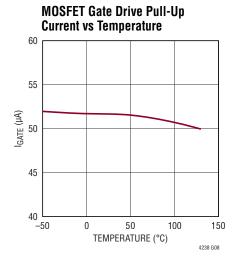

| I <sub>GATE(UP)</sub>               | GATE1, GATE2 Pull-Up Current                                            | Gate On, GATE = 0V                                                  | • | -35         | -50      | -70         | μA       |

| I <sub>GATE(DN)</sub>               | GATE1, GATE2 Fast Pull-Down Current                                     | $\Delta V_{SNS} = 100 \text{mV}, \ \Delta V_{GATE} = 6 \text{V}$    |   |             | 0.8      |             | A        |

|                                     | Gate Off Pull-Down Current to SOURCE                                    | $\Delta V_{GATE} = 6V$                                              | • | 6           | 10       | 16          | mA       |

|                                     | Gate Off Pull-Down Current to Ground                                    | $\Delta V_{GATE} = 6V$                                              | • | 0.5         | 1.5      | 2.5         | mA       |

| t <sub>PHL(SENSE)</sub>             | ΔV <sub>SNS</sub> High to GATE Low Propagation Delay                    | $\Delta V_{SNS} = 0$ mV to 100mV Step, C = 10nF                     | • |             | 0.5      | 1           | μs       |

| t <sub>PHL(GATE)</sub>              | UV, OV Turn Off Propagation Delay                                       | GATE < 6V, Gate Open                                                | • | 0.3         | 1        | 3           | μs       |

| t <sub>PHL(STRESS)</sub>            | Propagation Delay to Turn Off Low Stress<br>MOSFET in HSSS Mode         | Gate Open                                                           | • |             | 6        | 13          | μs       |

| Comparator Inpu                     | ıts                                                                     |                                                                     |   |             |          |             |          |

| $V_{TH}$                            | UV, OV, FB Threshold Voltage                                            | Rising                                                              | • | 2.5         | 2.56     | 2.62        | V        |

| $\Delta V_{UV(HYST)}$               | UV Hysteresis                                                           |                                                                     | • | 280         | 360      | 440         | mV       |

| $\Delta V_{OV(HYST)}$               | OV Hysteresis                                                           |                                                                     | • | 25          | 46       | 85          | mV       |

| $\Delta V_{FB(HYST)}$               | FB Power Good Hysteresis                                                |                                                                     | • | 60          | 80       | 100         | mV       |

| $V_{TH}$                            | UV Reset Threshold Voltage                                              | Falling                                                             | • | 0.95        | 1.00     | 1.05        | V        |

| $\Delta V_{UVR(HYST)}$              | UV Reset Threshold Hysteresis                                           |                                                                     | • | 50          | 100      | 150         | mV       |

| INPUT                               | UV, OV, FB Input Current                                                | V = 2.56V                                                           | • |             | 0        | ±1          | μA       |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{DD} = 48 \,^{\circ}\text{U}$ unless otherwise noted.

| SYMBOL                   | PARAMETER                                                     | CONDITIONS                                                              |   | MIN                         | TYP                         | MAX                          | UNITS |

|--------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|---|-----------------------------|-----------------------------|------------------------------|-------|

| V <sub>FETBAD(TH)</sub>  | V <sub>DD</sub> – SOURCE FET-Bad Threshold                    |                                                                         | • | 80                          | 100                         | 120                          | mV    |

| V <sub>STRESS(TH)</sub>  | V <sub>DD</sub> – SOURCE Low Stress Threshold                 |                                                                         | • | 1.6                         | 2                           | 2.4                          | V     |

| I <sub>SOURCE</sub>      | SOURCE Input Current                                          | V <sub>SOURCE</sub> = 48V                                               | • | 10                          | 40                          | 300                          | μА    |

| t <sub>DL(UV)</sub>      | Debounce Turn-On Propagation Delay                            | UV Turn-On                                                              | • | 30                          | 40                          | 50                           | ms    |

| t <sub>DL(OV)</sub>      | Turn-On Propagation Delay                                     | OV Turn-On                                                              | • |                             | 25                          | 50                           | μs    |

| t <sub>DL(PG)</sub>      | Power Good Delay                                              |                                                                         | • |                             | 1                           | 3                            | μs    |

| V <sub>CONFIG1/2</sub>   | Input High Threshold                                          |                                                                         | • | INTV <sub>CC</sub><br>- 0.8 | INTV <sub>CC</sub><br>- 0.5 | INTV <sub>CC</sub><br>- 0.2  | V     |

|                          | Input Low Threshold                                           |                                                                         | • | 0.2                         | 0.5                         | 0.8                          | V     |

| CONFIG                   | CONFIG Sink or Source Current                                 | CONFIG = 0 to INTV <sub>CC</sub>                                        | • |                             |                             | ±20                          | μA    |

| V <sub>ISET(TH)</sub>    | ISET Threshold Error                                          | (Note 4)                                                                | • |                             |                             | ±150                         | mV    |

| I <sub>ISET</sub>        | ISET Input Current                                            | V = 0, 5V                                                               | • |                             | 0                           | ±1                           | μA    |

| Other Pin and F          | Functions                                                     |                                                                         |   |                             |                             |                              |       |

| $V_{0L}$                 | PG, FLT# Output Low Voltage                                   | I = 2mA                                                                 | • |                             | 0.3                         | 0.4                          | V     |

| I <sub>OH</sub>          | PG, FLT# Leakage Current                                      | V = 80V                                                                 | • |                             | 0                           | ±1                           | μA    |

| R <sub>VDSFB</sub>       | Resistance Between V <sub>DD</sub> and V <sub>DSFB</sub> Pins | Gate On                                                                 | • | 90                          | 120                         | 150                          | kΩ    |

| I <sub>VDSFB</sub>       | V <sub>DSFB</sub> Input Current                               | Gate Off                                                                | • |                             | 0                           | ±1                           | μA    |

| Гсомм                    | COMM Source Current                                           | V = 2.5V, Gate On and in Current Limit                                  | • | -3.5                        | <b>-</b> 5                  | -6.5                         | μA    |

|                          | COMM Sink Current                                             | V = 2.5V, Gate Off                                                      | • | 3                           |                             |                              | mA    |

| V <sub>COMM(SERVO)</sub> | COMM Servo Voltage                                            | LSSS Start-Up                                                           | • | 0.35                        | 0.8                         | 0.9                          | V     |

|                          |                                                               | Gate Fully On, Not in Current Limit                                     | • | 2.3                         | 2.5                         | 2.7                          | V     |

| V <sub>COMM(TH)</sub>    | COMM High Threshold                                           | In Current Limit                                                        | • | INTV <sub>CC</sub><br>– 2   | INTV <sub>CC</sub><br>- 1.5 | INTV <sub>CC</sub><br>- 0.85 | V     |

|                          | COMM Low Threshold                                            | Gates On, Not in LSSS                                                   | • | 0.9                         | 1.4                         | 1.9                          | V     |

|                          | COMM LSSS Threshold                                           | Gate On, in LSSS                                                        | • | 0.1                         | 0.2                         | 0.3                          | V     |

| $V_{TMR(H)}$             | TMR, TMRFET High Threshold                                    | Rising (Note 5)                                                         | • | 2.50                        | 2.56                        | 2.62                         | V     |

| $V_{TMR(L)}$             | TMR, TMRFET Low Threshold                                     | Falling (Note 5)                                                        | • | 0.16                        | 0.2                         | 0.24                         | V     |

| I <sub>TMR(UP)</sub>     | TMR (ILIM), TMRFET Pull Up Current                            | V <sub>TIMER</sub> = 0V                                                 | • | -16.5                       | -20                         | -22                          | μA    |

|                          | TMR (SOA) Pull Up Current                                     | $\Delta V_{SNS} = 0V$ and $V_{DD} - V_{VDSFB} = 0V$                     | • |                             |                             | ±1                           | μA    |

|                          |                                                               | $\Delta V_{SNS}$ = 10mV and $V_{DD} - V_{VDSFB}$ = 6V                   | • | -90                         | -100                        | -110                         | μA    |

|                          |                                                               | $\Delta V_{SNS} = 20 \text{mV}$ and $V_{DD} - V_{VDSFB} = 50 \text{mV}$ | • | -2.5                        | -1.4                        | 1                            | μA    |

| I <sub>TMR(DN)</sub>     | TMR(ILIM) Pull Down Current                                   | V <sub>TMR</sub> = 2.56V                                                | • | 3                           | 5                           | 7                            | μА    |

| I <sub>TMRFET(DN)</sub>  | TMRFET Pull Down Current                                      | V <sub>TMRFET</sub> = 2.56V                                             | • | 0.2                         | 0.5                         | 0.8                          | mA    |

| D <sub>OC</sub>          | Overcurrent Auto-Retry Duty Cycle                             |                                                                         | • | 0.04                        | 0.08                        | 0.12                         | %     |

| D <sub>FETBAD</sub>      | FETBAD Auto-Retry Duty Cycle                                  |                                                                         | • | 0.8                         | 1.6                         | 2.4                          | %     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive. All voltages are referenced to GND unless otherwise specified.

**Note 3:** Internal clamps limit the GATE pin to a minimum of 10V above or 0.3V below SOURCE. Driving this pin to voltages beyond the clamp may damage the device.

Note 4: See Table 1 for more details.

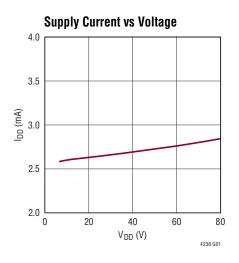

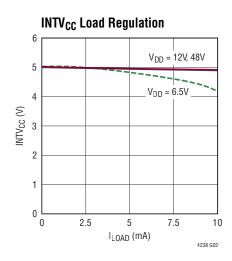

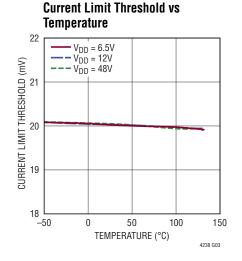

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, $V_{DD} = 48$ V unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, $V_{DD} = 48$ V unless otherwise noted.

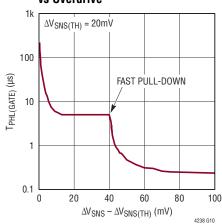

Current Limit Propagation Delay vs Overdrive

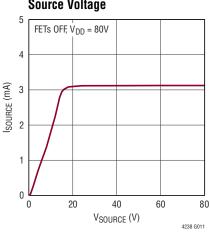

Source Pin Current vs Source Voltage

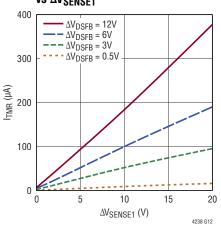

SOA Timer Pull-Up Current vs  $\Delta V_{SENSE1}$

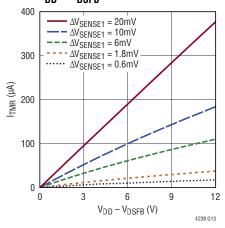

SOA Timer Pull-Up Current vs  $V_{DD} - V_{DSFB}$

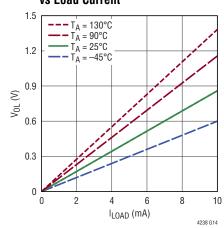

PG and FLT# Output Low Voltage vs Load Current

### PIN FUNCTIONS

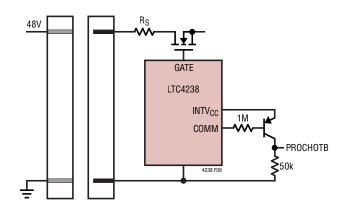

**COMM:** Communication Input/Output. Coordinates turn on, turn off, and overcurrent faults between parts. Directly connect the COMM pins of a group of parts to operate them together. COMM may also be used as an ON status or current limit status indicator. May be pulled to ground with an open drain output to turn off the part. Leave open if unused.

**CONFIG1, CONFIG2:** Three State Configuration Inputs. Decoded to select one of nine possible configurations. These include single FET, High Stress Staged Start (HSSS), Parallel or Low Stress Staged Start (LSSS) modes, current limit profile and timer type for TMR pin (see Table 3).

**FB:** Power Good Comparator Input. Connect this pin to an external resistive divider from SOURCE to GND. If the FB voltage falls below 2.48V, the PG pin will pull low to indicate the power is bad.

**FLT#:** Over Current or FET Bad Fault Output. An open drain output that pulls low when the FET bad timer or current limit/SOA timer expires. Tie FLT# and UV together through a resistor to INTV<sub>CC</sub> to enable auto-retry (see Applications Information for details).

**GATE1**, **GATE2**: Gate Drives for External N-Channel MOSFETs. Internal  $50\mu\text{A}$  current sources charge the gates of the MOSFETs. No compensation capacitors are required on the GATE pins, but a resistor-capacitor (RC) network from these pins to ground may be used to set the turn-on output voltage slew rate. During turn-off there is a 10mA pull-down current to SOURCE and a 1mA pull-down current to GND. During a short-circuit or undervoltage lock-out ( $V_{DD}$  or  $INTV_{CC}$ ), a 0.8A pull-down between GATE1/GATE2 and SOURCE is activated. If only one MOSFET is used, leave the GATE2 pin open and connect SENSE2+ and SENSE2- to  $V_{DD}$ .

**GND:** Device Ground.

**INTV**<sub>CC</sub>: Internal Supply Decoupling Output. Connect a capacitor no smaller than  $0.1\mu F$  from this pin to ground. Up to 10mA may be drawn from this pin to power application circuitry. This pin is current limited and will drop to GND to reduce heating in an overcurrent condition. Overloading this pin can disrupt internal operation. This

pin can be driven by an external supply that can only source, but not sink current.

**ISET:** Current Limit Adjustment Input. The ISET voltage is compared with seven threshold voltages generated by a resistive voltage divider from  $INTV_{CC}$ . The result sets the current limit voltage to be one of eight discrete values from 6mV to 20mV in 2mV increments. When ISET is connected to ground, the current limit threshold is set to 6mV. When ISET is connected to  $INTV_{CC}$ , current limit threshold is set to 20mV (see Table 1).

**NC:** No Connection. Not Internally connected.

**OV:** Overvoltage Comparator Input. Connect OV to an external resistive voltage divider from  $V_{DD}$  to GND. An overvoltage fault is detected if this pin rises above the 2.56V threshold. When the OV pin voltage falls back below the 2.51V falling threshold, the GATE pins will turn on again immediately. Tie to GND if unused.

**PG:** Power Good Output. An open drain output that pulls low when the FB pin drops below 2.48V indicating the power is bad. If the FB pin rises above 2.56V,  $V_{DD}-V_{SOURCE}$  is lower than 2V, and the GATEs are fully enhanced, the open-drain pull-down releases the PG to go high.

**SENSE1+**, **SENSE2+**: Positive Kelvin Current Sense Input. Connect these pins to the  $V_{DD}$  side of the current sense resistor(s).

**SENSE1**<sup>-</sup>, **SENSE2**<sup>-</sup>: Negative Kelvin Current Sense Input. Connect this pin to the MOSFET side of the current sense resistor(s). The current limit circuit controls the GATE pin to limit the sense voltage between the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins to the value selected by the ISET pin or less; depending on the voltage at the  $V_{DSFB}$  pin. Tie SENSE2<sup>-</sup> to  $V_{DD}$  when unused.

**SOURCE:** N-Channel MOSFET Source Connection. Connect this pin to the source of the external N-channel MOSFET switch. This pin provides a return for the gate pull-down circuit and is used as an input to the 100mV and  $2V\ V_{DS}$  comparators which are used for FET-BAD faults and staged start timing, respectively.

### PIN FUNCTIONS

**TMR:** Current Limit Timer or SOA Timer Output. The mode of operation is set by the state of CONFIG pins. In current limit timer mode, connect a capacitor between this pin and ground to set a 128ms/ $\mu$ F duration for current limit before the switch is turned off. If the UV pin is toggled low while the MOSFET switch is off, the switch will turn on again following a cool-down time of 150s/ $\mu$ F, resulting in a 0.08% duty cycle. In SOA timer mode, connect a RC network between this pin and ground. The current charging the RC network is proportional to the power dissipation in the powerpath, which is equal to  $\Delta V_{SENSE1}$  multiplied by the voltage difference between the  $V_{DD}$  and SOURCE pins as measured at the  $V_{DSFR}$  pin.

**TMRFET:** FET-Bad Timer Input. Connect a capacitor between this pin and ground to set a 128ms/μF duration for a FET-bad condition before the switch is turned off due to a FET-bad fault. If the UV pin is toggled low while the MOSFET switch is off, the switch will turn on again following a cool down time of 8s/μF, resulting in a 1.6% duty cycle. Tie to GND if unused.

**UV:** Undervoltage Comparator Input. Connect this pin to an external resistive divider from  $V_{DD}$  to GND. If the UV pin falls below 2.2V, an undervoltage is detected and the switch turns off. Pulling this pin below 1V resets the overcurrent and FET-bad faults and allows the switch to turn back on (see Applications Information for details). If overcurrent auto-retry is desired, then tie this pin to the FLT# pin. Tie to INTV $_{CC}$  if unused.

$V_{DD}$ : Supply Voltage Input. This pin has an undervoltage lockout threshold of 6V.  $V_{DD}$  is an input for the FET-bad comparator with a 100mV threshold. It is also an input for the stress comparator with a 2V threshold.

**V**<sub>DSFB</sub>: V<sub>DS</sub> Foldback Sense Input. This pin is used to monitor the drain to source voltage of the external MOSFETs, which is used by the SOA timer to monitor MOSFET power, as well as set the foldback current limit. 12V systems may connect V<sub>DSFB</sub> directly to the SOURCE pin. 48V systems will require an additional R<sub>VDSFB</sub> resistor of 10kΩ/V for input voltage over 12V to set the proper gain of the SOA timer and foldback circuits.

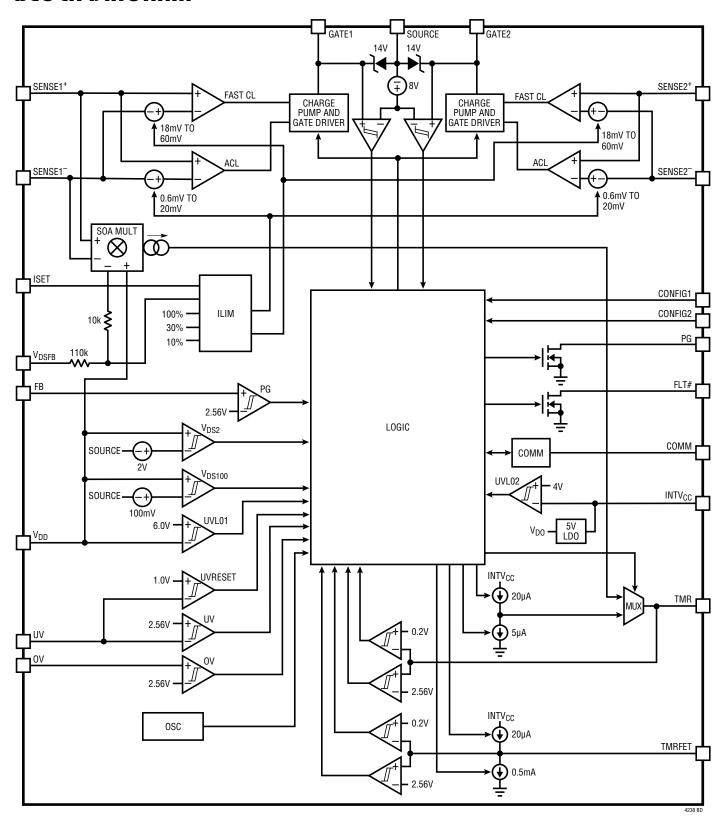

# **BLOCK DIAGRAM**

### **OPERATION**

The LTC4238 is designed to turn a board's supply voltage on and off in a controlled manner, allowing the board to be safely inserted or removed from a live backplane. The device features four distinct operation modes: single driver mode, parallel mode, high stress staged start mode (HSSS), and low stress staged start mode (LSSS). Each of these modes addresses specific application requirements for Safe Operating Area (SOA),  $R_{DS(ON)}$ , and cost.

The Block Diagram shows the monitoring blocks of the LTC4238. First, two undervoltage lockout circuits, UVLO1 and UVLO2, validate the input supply and the internally generated 5V supply, INTVCC. UVLO2 also generates the power-up initialization to the logic. The undervoltage (UV), and overvoltage (OV) comparators determine if the external conditions are valid prior to turning on the GATEs.

In normal operation, the LTC4238 turns on the external N-channel MOSFETs after a startup debounce delay, passing power to the load. A precise current limit value can be set from 6mV to 20mV in 2mV steps using the ISET voltage. During startup, the voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> may be controlled to be no higher than 10% of the current limit threshold or to the current limit threshold with foldback. The startup current may be set to even lower values with an external gate RC network.

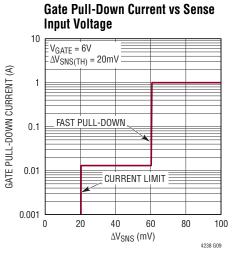

An overcurrent fault at the output may result in excessive MOSFET power dissipation during Active Current Limiting (ACL). To limit this power in each channel, the ACL amplifiers regulate the voltage between SENSE1+, SENSE1- and SENSE2+, SENSE2- pins by reducing the GATE-to-SOURCE voltages in an active control loop when the sense voltages exceed the current limit value. When the MOSFET's drain to source voltage is high, power dissipation is further reduced by folding back the current

limit to 30% of nominal based on foldback. In the event of a catastrophic output short, fast current limit comparators immediately pull the GATE pins down with 0.8A when the sensed current is three times the nominal current limit.

The LTC4238 provides two ways of limiting the time the system is exposed to overstress conditions: a MOSFET SOA timer or a current limit timer. The timer selection is made via the CONFIG pins. If the MOSFET SOA timer is chosen, the TMR pin is pulled up by a current that is proportional to the power dissipation in the MOSFET driven by GATE1. With an RC network representing the thermal behavior of this MOSFET, the TMR voltage is proportional to the MOSFET temperature rise. When the TMR voltage reaches its threshold of 2.56V (representing  $T_{J(MAX)}$  of the MOSFET), the overcurrent fault is triggered. Both GATEs turn off to protect the MOSFETs based on their SOA. If the current limit timer is chosen, the TMR pin is configured to drive a single capacitor and ramps up with 20µA when active current limiting is engaged. If the TMR pin reaches its 2.56V threshold, the LTC4238 turns off both GATEs and FLT# pin pulls low to indicate a fault. Then the TMR pin ramps down using a 5µA current source until the voltage drops below 0.2V. After that, the TMR pin will ramp up and down 256 times with 20µA/5µA to allow the pass transistor to cool down. If overcurrent auto-retry is enabled by tying the FLT# pin to the UV pin, the LTC4238 will turn on again at the end of 256 timer cycles.

The output voltage is monitored using the FB pin and the Power Good (PG) comparator to determine if the power is ready for the load. The power good condition is signaled by the PG pin using an open-drain pull-down transistor.

A typical LTC4238 application is a high availability system in which a positive voltage supply is distributed to power individual hot-swapped cards.

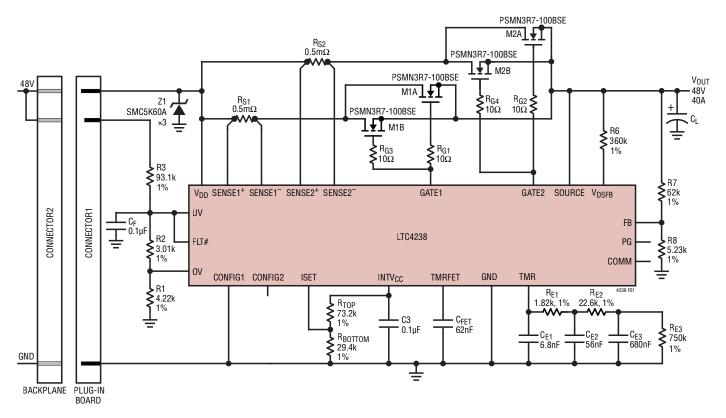

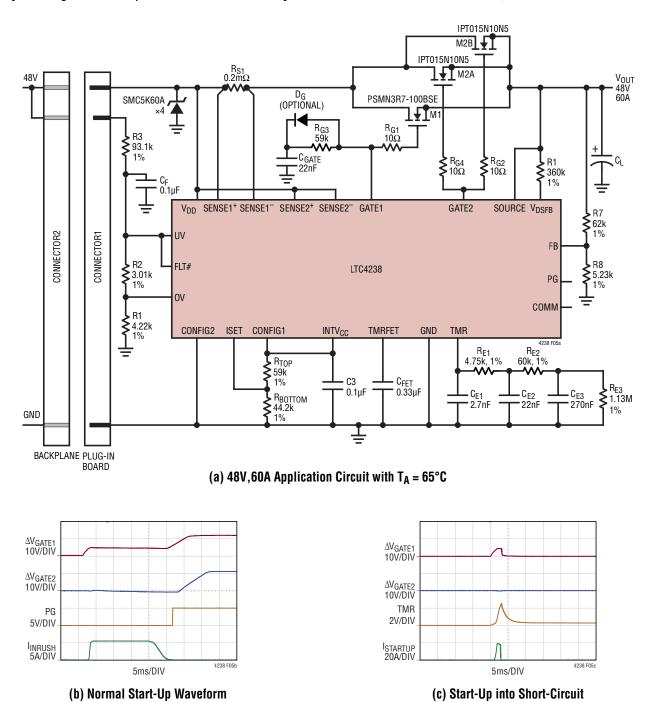

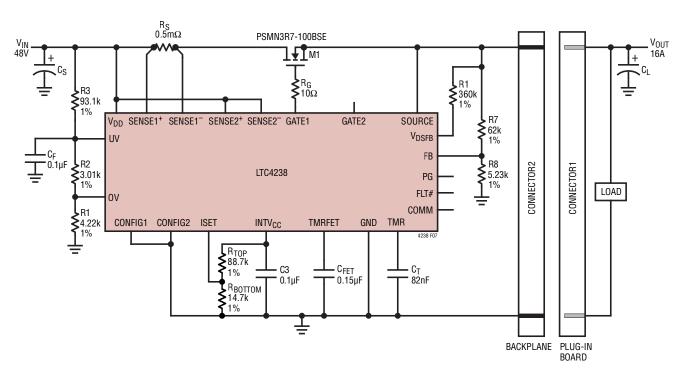

In the following sections, the parallel mode is first chosen to demonstrate common functions and basic hotswap applications. The unique features and applications of each operation mode are then described separately. A basic 48V, 40A LTC4238 application circuit is shown in Figure 1. The power supply on a board is controlled by using two pairs of N-channel pass transistors, M1A-B and M2A-B, placed in the power path. Resistors  $R_{\rm S1}$  and  $R_{\rm S2}$  sense current through M1A-B and M2A-B. Resistors R1, R2 and R3 define undervoltage and overvoltage levels.  $R_{\rm G1-4}$  prevent high frequency self-oscillations in the MOSFETs. R7 and R8 set the power good threshold, and R6 scales current limit foldback to the intended operating voltage.

The following sections cover turn-on, turn-off and various faults that the LTC4238 detects and acts upon. External

component selection is discussed in detail in the Design Examples section.

#### **Turn-On Sequence**

Several conditions must be met before the external MOSFETs turn on. First the external supply,  $V_{DD}$ , must exceed its 6.0V undervoltage lockout level. Next, the internally generated supply, INTV<sub>CC</sub>, must cross its 4V undervoltage threshold. This generates a power-on-reset pulse.

After a power-on-reset pulse, the UV and OV pins verify that input power is within the acceptable range. The state of the UV comparator must be stable for at least 40ms to qualify for turn-on. The MOSFETs are then turned on by charging up the GATE pins with  $50\mu A$  current sources. When the GATE voltage reaches the MOSFET threshold voltage, the MOSFET begins to turn on and the SOURCE voltage then follows the GATE voltages as it increases.

While the MOSFETs are turning on, the power dissipation in current limit for each MOSFET is limited to the

Figure 1. 48V, 40A Hot Swap Controller with SOA Timer in Parallel Mode

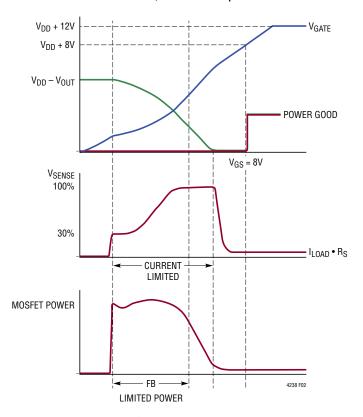

foldback profile as shown in Figure 2. As the SOURCE voltage rises, the  $V_{DSFB}$  and FB pins follow as set by R6, R7 and R8. Once the MOSFET drain to source voltage is lower than its 2V threshold, both GATE pins are higher than their 8V thresholds, and the FB pin has exceeded its

Figure 2. Power-Up Waveforms

2.56V threshold, then the PG pin releases high to indicate power is good and the load may be activated.

In normal operation, the minimum GATE-to-SOURCE ( $\Delta V_{GATE}$ ) drive voltage is 10V. The  $\Delta V_{GATE}$  voltage is clamped below 14V to protect the gates of 20V N-channel MOSFETs. A curve of  $\Delta V_{GATE}$  drive versus  $V_{DD}$  is shown in the typical performance characteristics.

#### **Turn-Off Sequence**

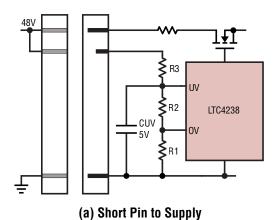

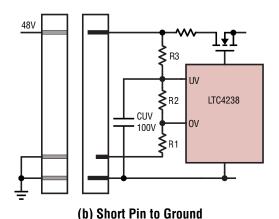

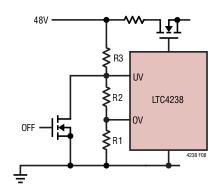

A normal turn-off sequence is initiated by card removal when the backplane connector short pin opens, causing the UV or OV comparator output to change state. Additionally, several fault conditions can turn off the GATEs. These include an input overvoltage, input undervoltage, overcurrent or FET-bad fault.

The MOSFETs are turned off with 10mA from GATE to SOURCE and with 1mA currents pulling the GATE pins to ground. With the MOSFET turned off, the SOURCE and FB voltages drop as the load capacitance discharges. When the FB voltage crosses below its threshold, PG pulls low to indicate that the output power is no longer good. If the  $V_{DD}$  pin falls below 5.5V or INTV<sub>CC</sub> drops below the undervoltage lockout falling threshold of 3.89V, a fast shut down of the MOSFET is initiated. The GATE pins are then pulled down with 0.8A currents to the SOURCE pin.

#### **Overcurrent Protection**

The LTC4238 features two levels of protection from shortcircuit and overcurrent conditions. Load current is monitored by the SENSE+ and SENSE- pins across the current sense resistors. There are two distinct thresholds for the current sense voltages, an active current limit threshold and a fast current limit comparator threshold. The fast current limit comparator threshold is always three times the nominal current limit threshold. If the sense voltage of a channel reaches the current limit threshold, the corresponding GATE is pulled down until the associated active current limit loop is engaged. In the event of a catastrophic short-circuit or a sudden input step, where the sense voltage of a channel reaches the fast current limit comparator threshold, the corresponding GATE is immediately pulled to SOURCE to limit peak current through the MOSFET. When the sense voltage drops to the current limit threshold, the active current limit loop is engaged.

#### **Current Limit Foldback**

The LTC4238 features an adjustable current limit with foldback that protects the MOSFETs from excessive power dissipation. During active current limiting, the available current is reduced as a function of the voltage across MOSFET sensed by  $V_{DD}$  and  $V_{DSFB}$  pins. The higher the voltage across MOSFET, the lower the current limit threshold will be. The lowest foldback value after start-up is 30% of the nominal voltage.

The nominal voltage of the LTC4238 current limit threshold is set between 6mV and 20mV in 2mV steps via the ISET pin (Table 1). This can be used to achieve a given current limit with the limited selection of standard sense

resistor values available around  $1m\Omega$ . Threshold values as low as 6mV reduce power dissipation in sense resistors for high current applications.

Two current limit foldback profiles are available to meet different application needs, constant power and high power. Refer to Table 3 for foldback configurations. The constant power profile is shaped such that the power in the MOSFET is constant while current limiting, regardless of V<sub>DS</sub>. This simplifies the SOA design of the application and makes the safe dissipation time a constant for various voltage and current conditions. This works well with the current limit timer on the TMR pin. However, the constant power foldback profile starts to fold back at small V<sub>DS</sub>. which could occur during an input step. For that reason the high power profile is also available. It doesn't start to fold back until the  $V_{DS}$  is around 50% of the nominal input voltage. This prevents the current limit from folding back after an input step and collapsing the output because it is less than the load current. Since the power dissipation in the MOSFET is not constant for the high power profile, the worst-case power dissipation usually occurs when half of the nominal supply voltage is across the MOSFET. Graphs in the Typical Performance Characteristics show the current limit and power versus voltage across the MOSFETs.

Additionally, to ease start-up, the LTC4238 features a configurable option for a start-up current at 10% of the full current limit. The LTC4238 stays at 10% until the conditions for power good are met, at which point it will switch to the normal foldback profile and current limit. In many cases this will eliminate the need for an RC network on the GATEs of the MOSFETs to limit the inrush current.

Configurations using the 10% current limit for start-up all use the SOA timer. This timer provides the flexibility to allow a long current limit timeout at low power levels during start-up, and a short current limit timeout during a fault after start-up.

#### **Constant Current Start-Up Using GATE RC Networks**

An optional series RC network from GATE to GND (Rg and C<sub>G</sub> in Figure 5) provides an inrush current less than the current limit by limiting the slew rate of the GATE pin. The current limit timer will not run since the current limit is not engaged during start-up. Thus, a small timer capacitor may be used which allows the use of MOSFETs with smaller SOA. Power good will signal when the FB pin crosses its 2.56V threshold and the  $\Delta V_{GATF}$  voltages cross their 8V thresholds. When both those conditions are met and the impedance back to the supply through the MOSFET is low, the output voltage is suitable for the load to be turned on. PG voltage goes high to indicate power is good. R<sub>G</sub> should be chosen such that I<sub>GATF</sub> • R<sub>G</sub> is less than the threshold voltage of the MOSFET to avoid an initial inrush current spike. But increasing R<sub>G</sub> improves the stability of the current limit servo loop (see Applications Information on current limit stability). If the voltage of the 50μA I<sub>GATE</sub> current across R<sub>G</sub> is higher than MOSFET's threshold, a diode may be added in parallel with the large  $R_G$  to limit its voltage while charging up  $C_G$  (see Figure 5). For the staged-start architectures, an RC network may be used on a trickle MOSFET or stress MOSFET. In the parallel architecture, identical RC networks may be used on both MOSFETs. Bypass MOSFETs don't need the current

Table 1. ISET Pin Voltage\* vs Current Limit Thresholds and Suggested 1% Resistor Values

|                           |                       | I <sub>SET</sub> Thresholds | Compared with |                             |                          |                                     |

|---------------------------|-----------------------|-----------------------------|---------------|-----------------------------|--------------------------|-------------------------------------|

| $\Delta V_{SNS(TH)}$ (mV) | V <sub>ISET</sub> (V) | Lower (V)                   | Upper (V)     | $R_TOP\left(k\Omega\right)$ | R <sub>BOTTOM</sub> (kΩ) | $R_{BOTTOM}/(R_{TOP} + R_{BOTTOM})$ |

| 6                         | 0                     |                             | 0.357         | Open                        | Short                    | 0.000                               |

| 8                         | 0.714                 | 0.357                       | 1.071         | 88.7                        | 14.7                     | 0.143                               |

| 10                        | 1.429                 | 1.071                       | 1.786         | 73.2                        | 29.4                     | 0.286                               |

| 12                        | 2.143                 | 1.786                       | 2.5           | 59.0                        | 44.2                     | 0.429                               |

| 14                        | 2.857                 | 2.5                         | 3.214         | 44.2                        | 59.0                     | 0.571                               |

| 16                        | 3.571                 | 3.214                       | 3.929         | 29.4                        | 73.2                     | 0.714                               |

| 18                        | 4.286                 | 3.929                       | 4.643         | 14.7                        | 88.7                     | 0.857                               |

| 20                        | 5                     | 4.643                       |               | Short                       | Open                     | 1.000                               |

<sup>\*</sup>INTV<sub>CC</sub> = 5V is used for this table.

limiting function of an RC network, but an RC network may be used in low stress staged start to improve the undershoot recovery time of the bypass MOSFET(s).

#### **Current Limit Stability**

For many applications the LTC4238 current limit loop is stable without additional components. However, there are certain conditions where additional components may be needed to improve stability. The dominant pole of the current limit circuit is set by the capacitance at the gate of the external MOSFET, and larger gate capacitance makes the current limit loop more stable. Usually a total of 10nF GATE-to-SOURCE capacitance is sufficient for stability and is provided by inherent MOSFET CGS. The stability of the loop is degraded by reducing the size of the resistor on a gate RC network if one is used, which may necessitate additional GATE-to-SOURCE capacitance. The worst case for current limit stability occurs when the output is shorted to ground after a normal start-up. Board level short-circuit testing is highly recommended as board layout can also affect transient performance.

#### Parasitic MOSFET Oscillations

Not all circuit oscillations can be ascribed to the current limit loop. Some higher frequency oscillations can arise from the MOSFETs themselves. (See Rarely Asked Questions 151, High-Side Current Sensing). There are two possible parasitic oscillation mechanisms. The first type of oscillation occurs at high frequencies, typically above 1MHz. This high frequency oscillation is easily damped with gate resistors RG1 – RG4 as shown in Figure 1. In some applications, one may find that these resistors help in short-circuit transient recovery as well. However, too large of a resistor will slow down the turn-off time. The recommended RG1 – RG4 range is between  $5\Omega$  and  $500\Omega$ .  $10\Omega$  provides stability without affecting turn-off time. These resistors must be located next to the MOSFET gate pin with no other connections between them.

A second type of parasitic oscillation occurs at frequencies between 200kHz and 800kHz when the MOSFET source is loaded with less than 10µF, and the drain is fed with an inductive impedance such as contributed by

wiring inductance. To prevent this second type of oscillation, load the source with more than  $10\mu\text{F}$  and bypass the input supply with a series  $10\Omega$ ,  $100\mu\text{F}$  snubber to ground.

#### **Overcurrent Fault with a Basic Current Limit Timer**

During active current limit, the power dissipation in the MOSFET is large. If this power dissipation persists, the MOSFET can reach temperatures that cause damage. A basic current limit timer has a single capacitor connected between TMR pin and GND and sets a maximum time for the MOSFET to operate in a current limit mode. When this timer expires, an over current fault is generated and the MOSFET is turned off to protect it from overheating.

Current limiting begins when the current sense voltage between the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins reaches the current limit threshold level (which depends on foldback and the voltage of the ISET pin). The corresponding GATE pin is then pulled down and regulated to limit the current sense voltage to the current limit value. In parallel mode, if either GATE is in current limit during start-up then the current limit timer starts to run. The external timer capacitor at the TMR pin will be charged with a 20µA pull-up current. After start-up, only when both GATE pins are regulated in current limit will the current limit timer start to run. If at least one of the GATE pins stops limiting current before the TMR pin reaches the 2.56V threshold, then the TMR pin will discharge with 5µA. For HSSS, LSSS or Single Driver Modes, if the current sense voltage between the SENSE1<sup>+</sup> and SENSE1<sup>-</sup> pins reaches the current limit threshold level, then the current limit timer will start to run. For a given current limit time delay, t<sub>ACL</sub>, use Equation 1 for setting the timing capacitor's value:

$$C_{TMR} = t_{ACL} \cdot 8[nF/ms] \tag{1}$$

When the TMR pin reaches its 2.56V threshold, the LTC4238 turns off both GATEs and generates an overcurrent fault. The MOSFETs are turned off with a 10mA current from GATE to SOURCE and a 1mA current from GATE to ground. Open-drain output FLT# also pulls low. After the fault, the TMR pin begins discharging with a  $5\mu$ A pull-down current. When the TMR pin reaches its 200mV low threshold, it will cycle up with  $20\mu$ A and down with  $5\mu$ A 256 times to give the MOSFETs time to cool.

An overcurrent fault may be cleared by pulling the UV pin below its 1V UV reset threshold, which happens automatically if FLT# is tied to the UV pin. Once the TMR completes the cool down delay, the MOSFETs turn on if the fault has been cleared. The cool down time is  $150s/\mu F$ , resulting in a 0.08% duty cycle.

MOSFET manufacturers specify the safe limits on operating voltage, current and time as a set of curves referred to as the Safe Operating Area (SOA). The proper timer capacitance must be set to allow the worst-case operating condition to stay within the SOA limits. The worst-case operating condition could be completely charging a large bypass capacitor at the output during start-up, or riding through a large input step. With a basic current limit timer, once a timer capacitance is set, the MOSFET must be selected to withstand the worst-case SOA condition that occurs during any possible normal operating condition or fault condition.

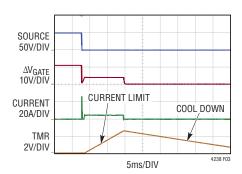

The waveform in Figure 3 shows how the output turns off following a short circuit.

Figure 3. GATE1, SOURCE, TMR Current vs Time

#### **Overcurrent Fault with the SOA Timer**

The LTC4238 features another mode for the TMR pin, SOA Timer, which better protects the MOSFET(s) when the power dissipated in the MOSFET varies widely. Instead of a constant  $20\mu\text{A}$  current, the TMR outputs a current proportional to the power dissipation in the MOSFET driven by GATE1 and the  $5\mu\text{A}$  internal TMR pull-down current is disabled. The assumption is made that in parallel mode the MOSFETs of both channels see the similar stresses. In other modes, the MOSFET at channel 1 sees more stress. The mode of TMR pin is configured using the CONFIG pins.

The SOA timer requires an RC network representing the MOSFET thermal model to be connected to TMR (Figure 1). At least two resistors and two capacitors are required for minimum accuracy of the thermal behavior. More RC elements provide better accuracy. Thus, the cost and board area are larger than the single-capacitor timer. The SOA timer voltage represents the real time rise in the junction temperature of the channel 1 MOSFET and its trip threshold 2.56V represents the maximum allowable peak temperature of the MOSFET. With the SOA timer, the selection of MOSFETs is much simpler: they just need to meet the worst-case operation requirements. In fault conditions such as output short, the SOA timer automatically protects the MOSFETs by turning them off once the maximum allowable peak temperature is reached (TMR tripped). With the single capacitor timer, the minimum capacitor must first be selected to keep the MOSFETs on during worst-case operating conditions, then the MOSFETs must be selected to withstand the worst-case SOA conditions during normal operating and fault conditions. The cost of MOSFETs selected based on the single capacitor timer for parallel mode or high stress staged start mode may be substantially higher than that using the SOA timer. It is recommended to use the SOA timer for high power applications using parallel mode or high stress staged start mode, especially for those with large input steps.

During all modes of operation an internal multiplier drives TMR with a current proportional to  $V_{SENSE1}$  multiplied by the voltage difference between  $V_{DD}$  and SOURCE pin as measured the  $V_{DSFB}$  pin (Equation 2).

$$I_{TMR} = \frac{400\mu A \cdot V_{SENSE1} \cdot (V_{DD} - V_{DSFB})}{20mV \cdot 12V}$$

(2)

For example, it produces  $100\mu A$  when  $V_{SENSE1}=10mV$  and  $V_{DD}-V_{DSFB}=6V$ . When the TMR voltage crosses its 2.56V threshold, the MOSFETs are shut off and an overcurrent fault is detected. When the multiplier output current is low, the TMR voltage drops as the RC network discharges. When it drops below 0.2V, Overcurrent Fault is cleared and MOSFETs can turn on if FLT# is connected to UV.

In order for the SOA timer to work properly, 12V is expected between  $V_{DD}$  and  $V_{DSFB}$  when  $V_{DD}$  is at its nominal and SOURCE is at ground. There is 120k of resistance

internally from  $V_{DD}$  to  $V_{DSFB}$ . For 12V systems,  $V_{DSFB}$  should be simply connected to SOURCE. For input voltages larger than 12V, add a resistance of  $10k\Omega/V$  between the  $V_{DSFB}$  and SOURCE pins. For example, for 48V systems, a 360k resistor is required to be added between the two pins.

Note that the SOA timer is independent of the current limit set via the ISET pin. The current limit may be adjusted with the ISET pin without the need to modify the thermal RC network. However, if the sense resistor value is changed, a modified thermal RC network will be required. Using a large current limit threshold, such as 20mV, achieves the greatest accuracy and dynamic range from the SOA timer. Refer to Typical Performance Characteristics for the SOA TMR pull-up currents at different  $\Delta V_{SENSE1}$  and different  $V_{DD}-V_{DSFB}$  voltages.

The configuration of the thermal RC network for a particular MOSFET starts with the selection of a desired number of resistive and capacitive elements. Their values are decided based on the thermal impedance plot provided by the MOSFET manufacturer. Three resistors and three capacitors are usually enough to fit the plot fairly well from 10µs to 100ms (Figure 1), which covers the timing range of typical operating and fault conditions. If better fitting accuracy or wider fitting range is desired, more elements may be used. After the thermal RC network is configured, the thermal quantities are then converted to electric quantities according to Equation 3.

$$R_{E} = k \cdot R_{\theta}$$

$$C_{E} = \frac{C_{\theta}}{k}$$

(3)

where  $R_E$  and  $C_E$  are electric resistance and capacitance, respectively and  $R_\theta$  and  $C_\theta$  are thermal resistance and capacitance, respectively. The conversion constant k is given by Equation 4.

$$k = \frac{V_{DS,MAX} \cdot I_{D,MAX}}{I_{TIMER(IJP),MAX}} \cdot \frac{V_{TIMER(TH)}}{\Delta T_{MAX}}$$

(4)

- $V_{DS,MAX}$  = The Maximum drain-to-source voltage that results in  $V_{DSFB}$  at 12V below  $V_{DD}$ .

- $I_{D,MAX} = 20 \text{mV/R}_{SENSE1}$ .

I<sub>TIMER(UP),MAX</sub> = The TMR pull-up current corresponding to the maximum power dissipation.

$$P_{MAX} = V_{DS,MAX} \cdot I_{D,MAX}$$

- V<sub>TMR(TH)</sub> = TMR rising threshold (2.56V).

- $\Delta T_{MAX}$  = The Maximum allowable temperature rise of the MOSFET.

For example, if  $V_{DS,MAX} = 58V$ ,  $I_{D,MAX} = 40A$ ,  $I_{TMR(UP),MAX} = 400\mu A$  and  $\Delta T_{MAX} = 110^{\circ}C$  (175°C  $T_{JMAX} - 65^{\circ}C$   $T_{A}$ ),  $k = 1.4 \cdot 10^{5}$  [V<sup>2</sup>/°C]. A thermal RC network consisting of three resistors and capacitors that represent the thermal behavior of PSMN3R7-100BSE is shown in Figure 1.

#### **FET-Bad Fault and Auto-Retry**

A damaged MOSFET may have leakage from gate to drain or have degraded  $R_{DS(ON)}$ . Debris on the board may also produce leakage or a short from the GATE pin to the SOURCE pin, the MOSFET drain, or to ground. In these conditions the LTC4238 may not be able to pull the GATE pin high enough to fully enhance the MOSFET, or the MOSFET may not reach the intended  $R_{DS(ON)}$  when the GATE pin is fully enhanced. This can put the MOSFET in a condition where the power in the MOSFET is higher than its continuous power handling capability, even though the current is below the current limit.

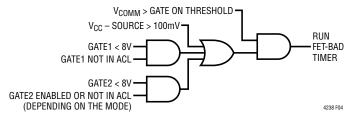

The LTC4238 monitors the integrity of the MOSFETs in two ways, and acts on both of them in the same manner. First, the LTC4238 monitors the voltage between the  $V_{DD}$  and SOURCE pins. A comparator detects a high DRAIN-to-SOURCE voltage ( $V_{DS}$ ) whenever  $V_{DD}$  to SOURCE voltage is greater than 100mV. Second, the LTC4238 monitors the GATE voltage. The GATE voltage may not fully enhance with a damaged MOSFET. A gate low condition is detected if Gate-to-Source voltage is lower than 8V, and that channel is not in active current limit.

When either a high DRAIN-to-SOURCE voltage or a gate low condition is present for either or both MOSFETs while they are commanded on, the FET-bad timer starts to run. The logic determining FET-bad condition is in Figure 4. The external timer capacitor on the TMRFET pin is charged with a  $20\mu\text{A}$  pull-up current. When the timer reaches the 2.56V rising threshold, a FET-bad fault condition is set, the

Figure 4. LOGIC Diagram for FET-Bad Timer

part turns off, and the GATE pins are pulled low with 10mA to SOURCE and 1mA to ground. If the DRAIN-to-SOURCE voltage falls below 100mV and the GATE low conditions are cleared before the TMRFET reaches 2.56V threshold, the TMRFET pin will discharge with 500µA. For a given FET-bad time delay, t<sub>FET-BAD</sub>, use Equation 5 for setting the timing capacitor's value:

$$C_{TMRFET} = t_{FET-BAD} \bullet 8[nF/ms]$$

(5)

Note that during start-up, the  $V_{DS}$  high condition is present because the voltage from drain-to-source is greater than 100mV. To avoid undesired turn-off, the FET-bad timer duration must be long enough for the largest allowable load to start up. FET-bad faults are disabled by grounding the TMRFET pin.

The LTC4238 treats a FET-bad fault similar to an overcurrent fault. If a FET-bad fault is detected, the MOSFETs are turned off and the TMRFET pin begins discharging with a 500 $\mu$ A pull-down current. When the TMRFET pin reaches its 0.2V threshold, it will cycle up with 20 $\mu$ A and down with 500 $\mu$ A 64 times to allow the MOSFET time to cool down. When automatically retrying with FLT# pin tied to UV pin, the resulting FET-bad duty cycle is 1.6%. After the final time the TMRFET pin falls below its 0.2V low threshold the MOSFETs are allowed to turn on again.

#### **Undervoltage and Overvoltage Faults**

The UV pin can be used to monitor a supply undervoltage condition using an external resistive voltage divider. An undervoltage fault occurs when the UV voltage falls below its 2.2V falling threshold. An overvoltage fault occurs when the OV voltage goes above its rising threshold of 2.56V. When either an undervoltage or overvoltage fault occurs, the LTC4238 shuts off the GATE pins with a 10mA current to SOURCE and a 1mA current to ground.

If the UV voltage subsequently rises back above the threshold for 40ms, the GATEs can turn on again. If the OV voltage subsequently falls back below the threshold, the GATEs can turn on again immediately. The UV and OV signals may be filtered by placing a capacitor,  $C_F$ , between the UV pin and GND.

#### **Dual Gate Operation Modes**

The LTC4238 features dual gate drivers that are configured by the CONFIG1 and CONFIG2 pins into four distinct operation modes: single driver, parallel, high stress staged start (HSSS), and low stress staged start (LSSS). As shown in Table 2, each mode features specific SOA or  $R_{DS(ON)}$  benefits, GATE(s) on/off behavior, power good signaling and fault detection logic.

All modes except LSSS support starting up with a resistive load such as a heating element or incandescent lamp. The modes of the dual gate drivers are selected together with the foldback profile and TMR behavior by the status of CONFIG1 and CONFIG2 pins as shown in Table 3.

#### **Parallel**

High current applications often demand several power MOSFETs in parallel to reach a target  $R_{DS(0N)}$  under  $1m\Omega$  that is unavailable in a single MOSFET. In addition, dividing the load current amongst multiple devices alleviates the PCB current crowding problem with the use of a single MOSFET.

Parallel MOSFETs share current well when their GATE-to-SOURCE voltages are fully enhanced. However, when the MOSFETs are limiting current, the mismatch between gate thresholds will cause the MOSFET with the lowest threshold to carry more current than the others. Since threshold voltage has a negative temperature coefficient, as this MOSFET heats it may carry even more current. Eventually all the load current may be carried by a single MOSFET. For this reason, when a group of MOSFETs are operated in parallel only the SOA (Safe Operating Area) of a single MOSFET is guaranteed.

The LTC4238 resolves this problem by offering two gate drivers, each with an independent current limit circuit and associated current sense pins. For configuration 4, 7, 8, and 9 as shown in Table 3, these two gate drivers operate

Table 2. LTC4238 Dual-Gate Operation Modes

| MODE            |                                       | SINGLE DRIVER                                                                                                                                    | PARALLEL                                                                                                                                            | HIGH STRESS STAGED START                                                                                                                                                       | LOW STRESS STAGED START                                                                                                                                                           |

|-----------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEATURE         |                                       | Simple                                                                                                                                           | SOA Doubled, R <sub>DS(ON)</sub> Halved                                                                                                             | GATE1 Drives High SOA<br>MOSFET.                                                                                                                                               | GATE1 Drives Low R <sub>DS(ON)</sub> ,<br>Small SOA MOSFET.                                                                                                                       |

|                 |                                       |                                                                                                                                                  |                                                                                                                                                     | GATE2 Drives Low R <sub>DS(ON)</sub><br>MOSFET                                                                                                                                 | GATE2 Drives Small SOA<br>MOSFET                                                                                                                                                  |

| TURN-0          | -                                     |                                                                                                                                                  | GATE1 and GATE2 Turn on at                                                                                                                          | GATE1 Turns on First.                                                                                                                                                          | GATE 2 Turns on First.                                                                                                                                                            |

| SEQUEN          | CE                                    |                                                                                                                                                  | the Same Time                                                                                                                                       | GATE2 Turns on after GATE1<br>Turns High and<br>V <sub>DD</sub> – V <sub>SOURCE</sub> < 2V and<br>Channel 1 Is Not in ACL                                                      | GATE1 Turns on if V <sub>FB</sub> > 2.56V<br>Once GATE2 Turns High                                                                                                                |

| POWER           | SET                                   | V <sub>DD</sub> – SOUI                                                                                                                           | RCE < 2V, and $V_{FB}$ > 2.56V, and $\Delta V_{FB}$                                                                                                 | $I_{\text{GATE1}} > 10\text{V}$ , and $(\Delta \text{V}_{\text{GATE2}} > 10\text{V})$                                                                                          | or Disabled)                                                                                                                                                                      |

| GOOD<br>LATCH   | GOOD LATCH RESET FB Drops Below 2.48V |                                                                                                                                                  |                                                                                                                                                     |                                                                                                                                                                                | FB Drops Below 2.48V or V <sub>COMM</sub><br>Drops Below 0.2V                                                                                                                     |

| GATE1 TI        | URN-OFF                               |                                                                                                                                                  | V <sub>COMM</sub> < 1.4V                                                                                                                            |                                                                                                                                                                                | V <sub>COMM</sub> < 0.2V or V <sub>FB</sub> < 2.56V                                                                                                                               |

|                 |                                       | $\begin{array}{l} \Delta V_{GATE1} < 8V \text{ or} \\ V_{DD} - SOURCE > 2V \text{ or} \\ Channel 1 \text{ is in ACL} \end{array}$                | V <sub>COMM</sub> < 1.4V                                                                                                                            | $\Delta V_{GATE1} < 8V$ or $V_{DD} - SOURCE > 2V$ or Channel is 1 in ACL                                                                                                       | V <sub>COMM</sub> < 0.2V                                                                                                                                                          |

| CURREN<br>TIMER | T LIMIT                               | Runs if V <sub>COMM</sub> > 3.5V or<br>Channel 1 is in ACL                                                                                       | Runs if V <sub>COMM</sub> > 3.5V or<br>During Start-Up:<br>Either Channel Is in ACL<br>After Start-Up:<br>Both Channels are in ACL                  | Runs if V <sub>COMM</sub> > 3.5V or<br>Channel 1 is in ACL                                                                                                                     | Runs if V <sub>COMM</sub> > 3.5V or<br>Channel 1 is in ACL                                                                                                                        |

| FET BAD         | TIMER                                 | Runs if $V_{COMM} > 1.4V$ and $[(V_{DD} - SOURCE > 100mV)$ or $(\Delta V_{GATE1} < 8V$ and Not in ACL) or $(\Delta V_{GATE2} < 8V$ and Enabled)] | Runs if $V_{COMM} > 1.4V$ and $[(V_{DD} - SOURCE > 100mV)$ or $(\Delta V_{GATE1} < 8V$ and Not in ACL) or $(\Delta V_{GATE2} < 8V$ and Not in ACL)] | Runs if $V_{COMM} > 1.4V$ and $[(V_{DD} - SOURCE > 100mV) \text{ or } (\Delta V_{GATE1} < 8V \text{ and Not in ACL}) \text{ or } (\Delta V_{GATE2} < 8V \text{ and Enabled})]$ | Runs if $V_{COMM} > 0.2V$ and $[(V_{DD} - SOURCE > 100mV) \text{ or } (\Delta V_{GATE1} < 8V \text{ and Not in ACL}) \text{ or } (\Delta V_{GATE2} < 8V \text{ and Not in ACL})]$ |

Table 3. LTC4238 Configurations

| CONFIGURATION | CONFIG2            | CONFIG1            | DUAL-GATE MODE | FOLDBACK PROFILE | TMR PIN TYPE        | 10% FOLDBACK DURING<br>Start-up |

|---------------|--------------------|--------------------|----------------|------------------|---------------------|---------------------------------|

| 1             | Ground             | Ground             | HSSS/Single    | High Power       | Current Limit Timer | No                              |

| 2             | Ground             | Open               | HSSS/Single    | Constant Power   | SOA Timer           | Yes                             |

| 3             | Ground             | INTV <sub>CC</sub> | HSSS/Single    | High Power       | SOA Timer           | No                              |

| 4             | Open               | Ground             | Parallel       | High Power       | SOA Timer           | No                              |

| 5             | Open               | Open               | LSSS           | Constant Power   | SOA Timer           | No                              |

| 6             | Open               | INTV <sub>CC</sub> | LSSS           | Constant Power   | Current Limit Timer | No                              |

| 7             | INTV <sub>CC</sub> | Ground             | Parallel       | Constant Power   | SOA Timer           | Yes                             |

| 8             | INTV <sub>CC</sub> | Open               | Parallel       | Constant Power   | SOA Timer           | No                              |

| 9             | INTV <sub>CC</sub> | INTV <sub>CC</sub> | Parallel       | High Power       | Current Limit Timer | No                              |

in parallel mode, in which GATE1 and GATE2 are turned on or off simultaneously. In this mode, the LTC4238 allows a group of parallel MOSFETs to be divided into two channels. During current limiting in an overcurrent event such as output short or input step, the independent gate control of the two channels divides the current evenly between them, resulting in twice the SOA performance of a Hot

Swap controller with a single current limit circuit. This allows the use of smaller, less expensive MOSFETs, can start up a load twice as big, or increase SOA margins. In addition, multiple LTC4238s can be connected in parallel using the COMM pin to coordinate turn on, turn off, and fault behavior to further improve SOA.

Figure 1 shows an application example providing 48V, 40A operating in the parallel mode. Two MOSFETs in each channel are used so that the power dissipation in each MOSFET is less than 1W when fully enhanced. After start-up, when the voltage across the MOSFETs drain and source is lower than 2V, the gate-to-source voltages for both MOSFETs are higher than 8V, and the FB voltage is higher than 2.56V, power is considered good. Open-drain output PG is then released to go high. After that, if the FB falls below 2.48V. PG will be reset to low.

If the current limit timer is selected with parallel mode (configuration 9), it will run if either channel is in current limit during start-up. Once start-up is finished and PG has been released, the current limit timer will run only if both channels are in current limit. If the SOA timer is selected, the RC network should represent the thermal behavior of a single MOSFET, since the TMR pull-up current is only related to the power dissipation in the channel 1 MOSFET. When TMR reaches 2.56V (representing the maximum allowable temperature rise in the MOSFET), both GATE1 and GATE2 are turned off and the overcurrent fault status will pull the FLT# pin low.

#### **High Stress Stage Start**

The two GATE drivers of the LTC4238 can also be configured to operate in high stress staged start mode by grounding the CONFIG2 pin (Table 3). In this mode GATE1 drives a high SOA MOSFET (M1) for start-up and to withstand overstresses; GATE2 drives less expensive bypass MOSFETs (M2A and M2B) with low  $R_{DS(ON)}$  and relaxed SOA requirements to carry the load, as shown in Figure 5a. The high stress staged start mode works well for systems where large input steps or supply surges may occur. M1 must be selected with large enough SOA to withstand these conditions, in which M1 not only carries the full load current, but also needs to deliver the current to charge up the load capacitor.

At power up, GATE1 is turned on first to charge the load and GATE2 is held off. As illustrated in Figure 5b, GATE2 is turned on when GATE1 is fully enhanced (GATE1 is more than 8V higher than SOURCE pin), the MOSFET drain to source voltage is lower than 2V and channel 1 is not in current limit. After GATE2 is more than 8V higher

than SOURCE pin, the open drain output PG pin is latched high given FB pin is higher than 2.56V. Most of the load current is delivered by M2A and M2B, which usually have much lower  $R_{DS(ON)}$  than M1.

In this mode the current sense resistor is connected between SENSE1+ and SENSE1-, while SENSE2+ and SENSE2- are connected to  $V_{DD}$  to disable the current limit circuit of GATE2. During overcurrent events such as an output short or an input step, the LTC4238 immediately switches off GATE2 to protect M2A and M2B from overstress, leaving the current limit of GATE1 to regulate the load current through M1. In this condition the TMR pullup current is turned on. When the TMR voltage reaches 2.56V, GATE1 is turned off and an overcurrent fault is logged.