Ultralow Distortion IF Amplifier/ADC Driver with Digitally Controlled Gain

### DESCRIPTION

The LT<sup>®</sup>5514 is a programmable gain amplifier (PGA) with bandwidth extending from low frequency (LF) to 850MHz. It consists of a digitally controlled variable attenuator, followed by a high linearity amplifier. The amplifier is configured with two identical transconductance amplifiers, hard wired in parallel with individual dedicated enable pins. When both amplifiers are enabled (Standard mode), the LT5514 offers an OIP3 of +47dBm (at 100MHz). Power dissipation can be reduced when a single amplifier is enabled (Low Power mode). Four parallel digital inputs control the gain over a 22.5dB range with 1.5dB step resolution. An on-chip power supply regulator/filter helps isolate the amplifier signal path from external noise sources.

The LT5514's open-loop architecture offers stable operation for any practical load conditions, including peakingfree AC response when driving capacitive loads, and excellent reverse isolation.

The LT5514 may be operated broadband, where the output differential RC time constant sets the bandwidth, or it may be used as a narrowband driver with the appropriate output filter.

T, LTC and LT are registered trademarks of Linear Technology Corporation.

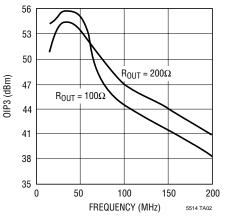

#### Output IP3 vs Frequency (Standard Mode)

# FEATURES

- Output IP3 at 100MHz: 47dBm

- Maximum Output Power: 21dBm

- Bandwidth: LF to 850MHz

- Propagation Delay: 0.8ns

- Maximum Gain: 33dB

- Noise Figure: 7.3dB (Max Gain)

- Gain Control Range: 22.5dB

- Gain Control Step: 1.5dB

- Gain Control Settling Time: 500ns

- Output Noise Floor: -134dBm/Hz (Max Gain)

- Reverse Isolation: –80dB

- Single Supply: 4.75V to 5.25V

- Low Power Mode

- Shutdown Mode

- Enable/Disable Time: 1µs

- Differential I/O Interface

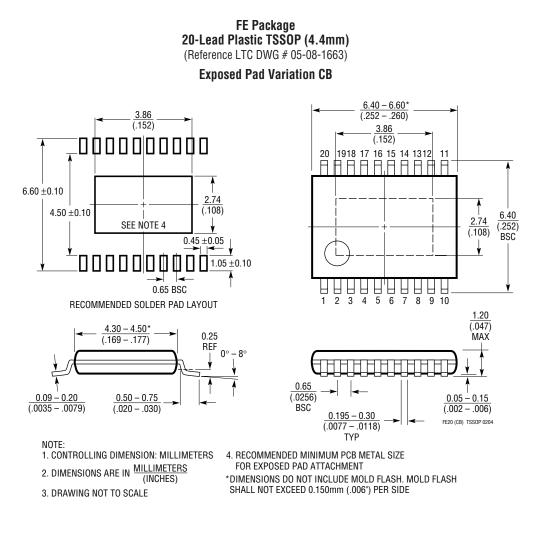

- 20-Lead TSSOP Package

## **APPLICATIONS**

- High Linearity ADC Driver

- IF Sampling Receivers

- VGA IF Power Amplifier

- 50Ω Driver

- Instrumentation Applications

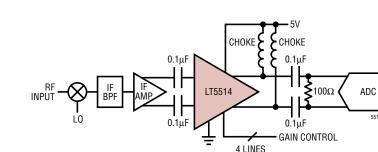

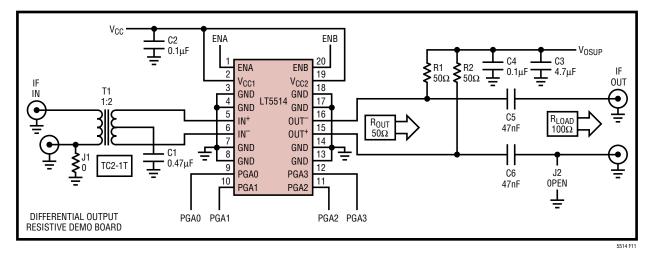

TYPICAL APPLICATION

## **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 2)

| Power Supply Voltage (V <sub>CC1</sub> , V <sub>CC2</sub> ) 6V        |

|-----------------------------------------------------------------------|

| Output Supply Voltage (OUT <sup>+</sup> , OUT <sup>-</sup> ) 8V       |

| Control Input Voltage (ENA, ENB, PGAx)0.5V to V <sub>CC</sub>         |

| Signal Input Voltage (IN <sup>+</sup> , IN <sup>-</sup> ) –0.5V to 3V |

| Operating Ambient Temperature Range 40°C to 85°C                      |

| Storage Temperature Range –65°C to 150°C                              |

| Lead Temperature (Soldering, 10 sec)                                  |

|                                                                       |

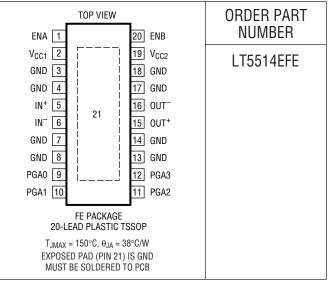

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

## **MODES OF OPERATION**

|   | MODES                 | ENA  | ENB  | AMP A | AMP B | LT5514 STATE             |

|---|-----------------------|------|------|-------|-------|--------------------------|

| 1 | Full Power (Standard) | High | High | On    | On    | Enable Amp A and Amp B   |

| 2 | Low Power A           | High | Low  | On    | Off   | Enable Amp A             |

| 3 | Low Power B           | Low  | High | Off   | On    | Enable Amp B             |

| 4 | Shutdown              | Low  | Low  | Off   | Off   | Sleep, All Amps Disabled |

## **PROGRAMMABLE GAIN SETTINGS**

|     | ATTENUATION STEP            | FION STEP |      |      | POWE | R GAIN          |                  |

|-----|-----------------------------|-----------|------|------|------|-----------------|------------------|

|     | <b>RELATIVE TO MAX GAIN</b> | PGAO      | PGA1 | PGA2 | PGA3 | STANDARD MODE*  | LOW POWER MODE** |

| 1   | 0dB                         | High      | High | High | High | 33.0dB          | 30.0dB           |

| 2   | -1.5dB                      | Low       | High | High | High | 31.5dB          | 28.5dB           |

| 3   | -3.0dB                      | High      | Low  | High | High | 30.0dB          | 27.0dB           |

| 4   | -4.5dB                      | Low       | Low  | High | High | 28.5dB          | 25.5dB           |

| 5   | -6.0dB                      | High      | High | Low  | High | 27.0dB          | 24.0dB           |

| 6   | -7.5dB                      | Low       | High | Low  | High | 25.5dB          | 22.5dB           |

| 7   | -9.0dB                      | High      | Low  | Low  | High | 24.0dB          | 21.0dB           |

| 8   | -10.5dB                     | Low       | Low  | Low  | High | 22.5dB          | 19.5dB           |

| 9   | -12.0dB                     | High      | High | High | Low  | 21.0dB          | 18.0dB           |

| 10  | -13.5dB                     | Low       | High | High | Low  | 19.5dB          | 16.5dB           |

| 11  | -15.0dB                     | High      | Low  | High | Low  | 18.0dB          | 15.0dB           |

| 12  | -16.5dB                     | Low       | Low  | High | Low  | 16.5dB          | 13.5dB           |

| 13  | -18.0dB                     | High      | High | Low  | Low  | 15.0dB          | 12.0dB           |

| 14  | -19.5dB                     | Low       | High | Low  | Low  | 13.5dB          | 10.5dB           |

| 15  | -21.0dB                     | High      | Low  | Low  | Low  | 12.0dB          | 9.0dB            |

| 16  | -22.5dB                     | Low       | Low  | Low  | Low  | 10.5dB (Note 3) | 7.5dB (Note 3)   |

| · D | - 2000 **Paula - 4000       |           |      | •    |      | ·               |                  |

$R_{0UT} = 200\Omega$   $R_{0UT} = 400\Omega$

5514f

# **DC ELECTRICAL CHARACTERISTICS** $V_{CC} = 5V$ , $V_{CCO} = 5V$ , ENA = ENB = 3V, $T_A = 25^{\circ}C$ , unless otherwise noted. (Note 7) (Test circuits shown in Figures 9 and 10)

| SYMBOL                   | PARAMETER                                                                            | CONDITIONS                                                                                                      | MIN  | ТҮР  | MAX  | UNITS       |

|--------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-------------|

| Normal Ope               | rating Conditions                                                                    |                                                                                                                 |      |      |      | ·           |

| V <sub>CC</sub>          | Supply Voltage (Pins 2, 19)                                                          | (Note 4)                                                                                                        | 4.75 | 5    | 5.25 | V           |

| V <sub>CCO</sub>         | OUT <sup>+</sup> , OUT <sup>-</sup> Output Pin DC Common Mode Voltage                | OUT <sup>+</sup> , OUT <sup>-</sup> Connected to V <sub>OSUP</sub> via<br>Choke Inductors or Resistors (Note 5) | 3    | 5    | 6    | V           |

| V <sub>OUT</sub>         | OUT <sup>+</sup> , OUT <sup>-</sup> Pin Instantaneous Voltage with<br>Respect to GND | Min/Max Limits Apply                                                                                            | 2    |      | 8    | V           |

| Shutdown D               | C Characteristics, ENA = ENB = 0.6V                                                  |                                                                                                                 |      |      |      |             |

| VIN(BIAS)                | IN <sup>+</sup> , IN <sup>-</sup> Bias Voltage                                       | Max Gain (Note 6)                                                                                               | 1.15 | 1.3  | 1.5  | V           |

| I <sub>IL(PGA)</sub>     | PGAO, PGA1, PGA2, PGA3 Input Current                                                 | V <sub>IN</sub> = 0.6V                                                                                          |      |      | 20   | μA          |

| I <sub>IH(PGA)</sub>     | PGAO, PGA1, PGA2, PGA3 Input Current                                                 | V <sub>IN</sub> = 5V                                                                                            |      |      | 20   | μA          |

| I <sub>OUT</sub>         | OUT <sup>+</sup> , OUT <sup>-</sup> Current                                          | All Gain Settings                                                                                               |      |      | 20   | μA          |

| I <sub>CC</sub>          | V <sub>CC</sub> Supply Current                                                       | All Gain Settings (Note 4)                                                                                      |      | 44   | 100  | μA          |

| Enable and               | PGA Inputs DC Characteristics                                                        |                                                                                                                 |      |      |      | ·           |

| V <sub>IL</sub>          | ENA, ENB and PGAx Input Low Voltage                                                  | x = 0, 1, 2, 3                                                                                                  |      |      | 0.6  | V           |

| V <sub>IH</sub>          | ENA, ENB and PGAx Input High Voltage                                                 | x = 0, 1, 2, 3                                                                                                  | 3    |      |      | V           |

| I <sub>IL(PGA)</sub>     | PGAO, PGA1, PGA2, PGA3 Input Current                                                 | V <sub>IN</sub> = 0.6V                                                                                          |      |      | 20   | μA          |

| I <sub>IH(PGA)</sub>     | PGAO, PGA1, PGA2, PGA3 Input Current                                                 | V <sub>IN</sub> = 3V and 5V                                                                                     |      | 15   | 30   | μA          |

| I <sub>IL(EN)</sub>      | ENA, ENB Input Current                                                               | V <sub>IN</sub> = 0.6V                                                                                          |      | 4    | 20   | μA          |

| I <sub>IH(EN)</sub>      | ENA, ENB Input Current                                                               | V <sub>IN</sub> = 3V                                                                                            |      | 18   |      | μA          |

|                          |                                                                                      | V <sub>IN</sub> = 5V                                                                                            |      | 38   | 100  | μA          |

| Standard M               | ode DC Characteristics, ENA = ENB = 3V                                               | 1                                                                                                               | 1    |      |      | <del></del> |

| V <sub>IN(BIAS)</sub>    | IN+, IN <sup>-</sup> Bias Voltage                                                    | Max Gain (Note 6)                                                                                               | 1.34 | 1.49 | 1.65 | V           |

| R <sub>IN</sub>          | Input Differential Resistance                                                        | All Gain Settings (DC)                                                                                          |      | 108  |      | Ω           |

| g <sub>m</sub>           | Amplifier Transconductance                                                           | Max Gain                                                                                                        |      | 0.3  |      | S           |

| I <sub>OUT</sub>         | OUT <sup>+</sup> , OUT <sup>-</sup> Quiescent Current                                | All Gain Settings, V <sub>OUT</sub> = 5V                                                                        | 33   | 40   | 47   | mA          |

| I <sub>OUT(OFFSET)</sub> | Output Current Mismatch                                                              | All Gain Settings, IN <sup>+</sup> , IN <sup>-</sup> Open                                                       |      | 200  |      | μA          |

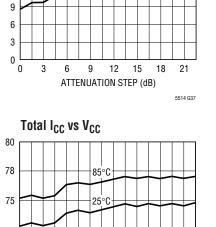

| I <sub>CC</sub>          | V <sub>CC1</sub> + V <sub>CC2</sub> Supply Current                                   | Max Gain (Note 4)                                                                                               |      | 64   | 75   | mA          |

|                          |                                                                                      | Min Gain (Note 4)                                                                                               |      | 68   | 80   | mA          |

| ICC(TOTAL)               | Total Supply Current                                                                 | I <sub>CC</sub> + 2 • I <sub>OUT</sub> (Max Gain)                                                               |      | 148  | 174  | mA          |

|                          | Mode DC Characteristics, ENA = 0.6V, ENB = 3V or E                                   | ,                                                                                                               |      |      | 4.05 |             |

| V <sub>IN(BIAS)</sub>    | IN+, IN <sup>-</sup> Bias Voltage                                                    | Max Gain (Note 6)                                                                                               | 1.34 | 1.48 | 1.65 | V           |

| R <sub>IN</sub>          | Input Differential Resistance                                                        | All Gain Settings (DC)                                                                                          |      | 122  |      | Ω           |

| g <sub>m</sub>           | Amplifier Transconductance                                                           | Max Gain                                                                                                        |      | 0.15 |      | S           |

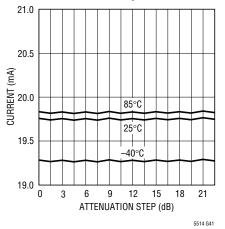

| I <sub>OUT</sub>         | OUT <sup>+</sup> , OUT <sup>-</sup> Quiescent Current                                | All Gain Settings, V <sub>OUT</sub> = 5V                                                                        | 17   | 20   | 24   | mA          |

| I <sub>OUT(OFFSET)</sub> | Output Current Mismatch                                                              | All Gain Settings, IN <sup>+</sup> , IN <sup>-</sup> Open                                                       |      | 100  |      | μA          |

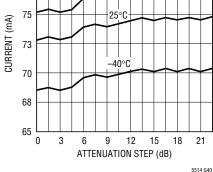

| I <sub>CC</sub>          | V <sub>CC1</sub> + V <sub>CC2</sub> Supply Current                                   | Max Gain (Note 4)                                                                                               |      | 34   | 40   | mA          |

|                          | Tatal Cupply Current                                                                 | Min Gain (Note 4)                                                                                               |      | 36   | 43   | mA          |

| ICC(TOTAL)               | Total Supply Current                                                                 | $I_{CC} + 2 \bullet I_{OUT}$ (Max Gain)                                                                         |      | 76   | 91   | mA          |

**AC ELECTRICAL CHARACTERISTICS** (Standard Mode)  $V_{CC} = 5V$ ,  $V_{CCO} = 5V$ , ENA = ENB = 3V,  $T_A = 25^{\circ}C$ ,  $R_{OUT} = 200\Omega$ . Maximum gain specifications are with respect to differential inputs and differential outputs, unless otherwise noted. (Note 7) (Test circuits shown in Figures 9 and 10)

| SYMBOL                          | PARAMETER                                                                          | CONDITIONS                                                                                              | MIN          | ТҮР                    | MAX    | UNITS            |

|---------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------|------------------------|--------|------------------|

| Dynamic P                       | erformance                                                                         |                                                                                                         |              |                        |        |                  |

| BW                              | Large-Signal –3dB Bandwidth                                                        | All Gain Settings (Note 8)<br>$R_{OUT} = 100\Omega$<br>$R_{OUT} = 200\Omega$ ; L1, L2 = 33nH (Figure 9) |              | LF to 850<br>LF to 500 |        | MHz<br>MHz       |

| P <sub>OUT(MAX)</sub>           | Clipping Limited Maximum Sinusoidal<br>Output Power                                | All Gain Settings, Single Tone, $R_{OUT}$ = 150 $\Omega$ $f_{IN}$ = 100MHz (Note 10)                    |              | 21                     |        | dBm              |

| 9m                              | Amplifier Transconductance                                                         | Max Gain, f <sub>IN</sub> = 100MHz<br>PGA1 = Low, f <sub>IN</sub> = 100MHz                              | 0.30<br>0.21 |                        | S<br>S |                  |

| S12                             | Reverse Isolation                                                                  | $f_{IN} = 100MHz (Note 9)$<br>$f_{IN} = 400MHz (Note 9)$                                                | -92<br>-78   |                        |        | dB<br>dB         |

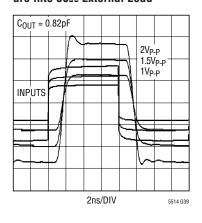

| t <sub>r</sub> , t <sub>f</sub> | Step Response Rise and Fall Time                                                   | All Gain Settings, 10% to 90%, $R_{OUT}$ = 100 $\Omega$                                                 |              | 500                    |        | ps               |

|                                 | Group Delay                                                                        | All Gain Settings, $R_{OUT} = 100\Omega$                                                                |              | 800                    |        | ps               |

|                                 | Group Delay Variation                                                              | $30 MHz$ to $300 MHz$ Frequency Range, $R_{0UT}$ = $100 \Omega$                                         |              | ±50                    |        | ps               |

|                                 | PGA Settling Time                                                                  |                                                                                                         |              | 500                    |        | ns               |

|                                 | Enable/Disable Time                                                                |                                                                                                         |              | 600                    |        | ns               |

| Distortion                      | and Noise                                                                          |                                                                                                         |              |                        |        |                  |

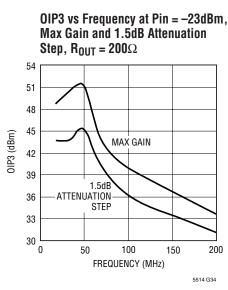

| OIP3                            | Output Third Order Intercept Point for<br>PGA0 = High (PGA1, PGA2, PGA3 Any State) | $P_{OUT}$ = 9dBm (Each Tone), 200kHz Tone Spacing $f_{\rm IN}$ = 100MHz $f_{\rm IN}$ = 200MHz           |              | +47.0<br>+40.5         |        | dBm<br>dBm       |

|                                 | Output Third Order Intercept Point for<br>PGA0 = Low (PGA1, PGA2, PGA3 Any State)  | $P_{OUT}$ = 9dBm (Each Tone), 200kHz Tone Spacing<br>$f_{IN}$ = 100MHz<br>$f_{IN}$ = 200MHz             |              | +42.0<br>+37.5         |        | dBm<br>dBm       |

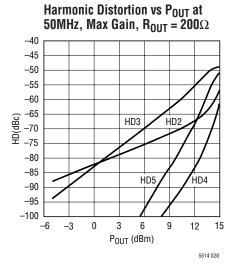

| HD2                             | Second Harmonic Distortion                                                         | P <sub>OUT</sub> = 11dBm (Single Tone), f <sub>IN</sub> = 50MHz                                         |              | -82                    |        | dBc              |

| HD3                             | Third Harmonic Distortion                                                          | P <sub>OUT</sub> = 11dBm (Single Tone), f <sub>IN</sub> = 50MHz                                         |              | -72                    |        | dBc              |

| N <sub>FLOOR</sub>              | Output Noise Floor<br>(PGAO, PGA2, PGA3 Any State)                                 | PGA1 = High, f <sub>IN</sub> = 100MHz<br>PGA1 = Low, f <sub>IN</sub> = 100MHz                           |              | -134<br>-136           |        | dBm/Hz<br>dBm/Hz |

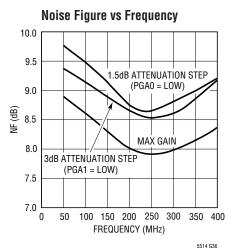

| NF                              | Noise Figure                                                                       | Max Gain, f <sub>IN</sub> = 100MHz<br>–3dB Step, f <sub>IN</sub> = 100MHz                               |              | 7.4<br>7.7             |        | dB<br>dB         |

| Amplifier I                     | Power Gain and Gain Step                                                           |                                                                                                         |              |                        |        | •                |

| G <sub>MAX</sub>                | Maximum Gain                                                                       | f <sub>IN</sub> = 20MHz and 200MHz                                                                      |              | 33                     |        | dB               |

| G <sub>MIN</sub>                | Minimum Gain                                                                       | f <sub>IN</sub> = 20MHz and 200MHz                                                                      |              | 10.5                   |        | dB               |

| G <sub>STEP</sub>               | Gain Step Size                                                                     | f <sub>IN</sub> = 20MHz and 200MHz                                                                      | 1.05         | 1.5                    | 1.95   | dB               |

|                                 | Gain Step Accuracy                                                                 | f <sub>IN</sub> = 20MHz and 200MHz                                                                      |              | ±0.1                   |        | dB               |

| Amplifier I                     | /O Impedance (Parallel Values Specified Diffe                                      | rentially)                                                                                              |              |                        |        |                  |

| R <sub>IN</sub>                 | Input Resistance                                                                   | f <sub>IN</sub> = 100MHz                                                                                |              | 108                    |        | Ω                |

| C <sub>IN</sub>                 | Input Capacitance                                                                  | f <sub>IN</sub> = 100MHz                                                                                |              | 2.8                    |        | pF               |

| R <sub>0</sub>                  | Output Resistance                                                                  | f <sub>IN</sub> = 100MHz                                                                                |              | 3.4                    |        | kΩ               |

| Co                              | Output Capacitance                                                                 | f <sub>IN</sub> = 100MHz                                                                                |              | 1.9                    |        | pF               |

5514f

**AC ELECTRICAL CHARACTERISTICS** (Low Power Mode)  $V_{CC} = 5V$ ,  $V_{CCO} = 5V$ , ENA = 3V, ENB = 0.6V,  $T_A = 25^{\circ}C$ ,  $R_{OUT} = 200\Omega$ . Maximum gain specifications are with respect to differential inputs and differential outputs, unless otherwise noted. (Note 7) (Test circuits shown in Figures 9 and 10)

| SYMBOL                | PARAMETER                                                                          | CONDITIONS                                                                    | MIN  | ТҮР          | MAX  | UNITS                                        |

|-----------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|--------------|------|----------------------------------------------|

| Dynamic P             | erformance                                                                         | ·                                                                             |      |              |      | <u> </u>                                     |

| BW                    | Large-Signal –3dB Bandwidth                                                        | All Gain Settings (Note 8), $R_{0UT}$ = 100 $\Omega$                          |      | LF to 540    |      | MHz                                          |

| P <sub>OUT(MAX)</sub> | Clipping Limited Maximum Sinusoidal<br>Output Power                                | All Gain Settings, Single Tone, $f_{\text{IN}} = 100 \text{MHz}$ (Note 10)    |      | 16           |      | dBm                                          |

| g <sub>m</sub>        | Amplifier Transconductance                                                         | Max Gain, f <sub>IN</sub> = 100MHz                                            |      | 0.15         |      | S                                            |

| S12                   | Reverse Isolation                                                                  | f <sub>IN</sub> = 100MHz (Note 9)                                             | -92  |              |      | dB                                           |

| Distortion            | and Noise                                                                          | ·                                                                             |      |              |      |                                              |

| OIP3                  | Output Third Order Intercept Point for<br>PGA0 = High (PGA1, PGA2, PGA3 Any State) | $P_{OUT} = 4dBm$ (Each Tone), 200kHz Tone Spacing, $f_{IN} = 100MHz$          |      | +40          |      | dBm                                          |

|                       | Output Third Order Intercept Point for<br>PGA0 = Low (PGA1, PGA2, PGA3 Any State)  | $P_{OUT}$ = 4dBm (Each Tone), 200kHz Tone Spacing, $f_{IN}$ = 100MHz          |      | +36          |      | dBm                                          |

| HD2                   | Second Harmonic Distortion                                                         | $P_{OUT} = 5dBm$ (Single Tone), $f_{IN} = 50MHz$                              |      | -76          |      | dBc                                          |

| HD3                   | Third Harmonic Distortion                                                          | P <sub>OUT</sub> = 5dBm (Single Tone), f <sub>IN</sub> = 50MHz                |      | -72          |      | dBc                                          |

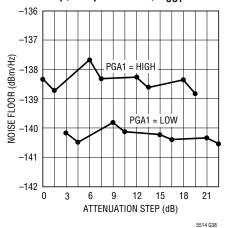

| N <sub>FLOOR</sub>    | Output Noise Floor<br>(PGAO, PGA2, PGA3 Any State)                                 | PGA1 = High, f <sub>IN</sub> = 100MHz<br>PGA1 = Low, f <sub>IN</sub> = 100MHz |      | -138<br>-140 |      | dBm/Hz<br>dBm/Hz                             |

| NF                    | Noise Figure                                                                       | Max Gain Setting, f <sub>IN</sub> = 100MHz                                    |      | 8.6          |      | dB                                           |

| Amplifier F           | Power Gain and Gain Step                                                           | · · · · · ·                                                                   |      |              |      | <u>.                                    </u> |

| G <sub>MAX</sub>      | Maximum Gain                                                                       | f <sub>IN</sub> = 20MHz and 200MHz                                            |      | 27           |      | dB                                           |

| G <sub>MIN</sub>      | Minimum Gain                                                                       | f <sub>IN</sub> = 20MHz and 200MHz                                            |      | 4.5          |      | dB                                           |

| G <sub>STEP</sub>     | Gain Step Size                                                                     | f <sub>IN</sub> = 20MHz and 200MHz                                            | 1.05 | 1.5          | 1.95 | dB                                           |

|                       | Gain Step Accuracy                                                                 | f <sub>IN</sub> = 20MHz and 200MHz                                            |      | ±0.1         |      | dB                                           |

| Amplifier I           | /O Impedance                                                                       |                                                                               |      |              |      |                                              |

| R <sub>IN</sub>       | Input Resistance                                                                   | f <sub>IN</sub> = 100MHz, Parallel Values Specified<br>Differentially         |      | 122          |      | Ω                                            |

| C <sub>IN</sub>       | Input Capacitance                                                                  | f <sub>IN</sub> = 100MHz, Parallel Values Specified<br>Differentially         |      | 2            |      | pF                                           |

| R <sub>0</sub>        | Output Resistance                                                                  | f <sub>IN</sub> = 100MHz, Parallel Values Specified<br>Differentially         | 5    |              | kΩ   |                                              |

| C <sub>0</sub>        | Output Capacitance                                                                 | f <sub>IN</sub> = 100MHz, Parallel Values Specified<br>Differentially         | 1.7  |              | pF   |                                              |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 2: All voltage values are with respect to ground.

Note 3: Default state for open PGA inputs.

**Note 4:** V<sub>CC1</sub> and V<sub>CC2</sub> (Pins 2 and 19) are internally connected.

Note 5: External V<sub>OSUP</sub> is adjusted such that V<sub>CCO</sub> output pin common mode voltage is as specified when resistors are used. For choke inductors or transformer,  $V_{OSUP} = V_{CCO} = 5V$  typ.

Note 6: Internally generated common mode input bias voltage requires capacitive or transformer coupling to the signal source.

Note 7: Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls. Gain always refers to power gain. Input matching is assumed.  $P_{IN}$  is the available input power.  $P_{OUT}$  is the power into the external load, R<sub>OUT</sub>, as seen by the LT5514 differential outputs. All dBm figures are with respect to  $50\Omega$ .

Note 8: High frequency operation is limited by the RC time constants at the input and output ports. The low frequency (LF) roll-off is set by I/O interface choice.

Note 9: Limited by package and board isolation.

Note 10: See "Clipping Free Operation" in the Applications Information section. Refer to Figure 7.

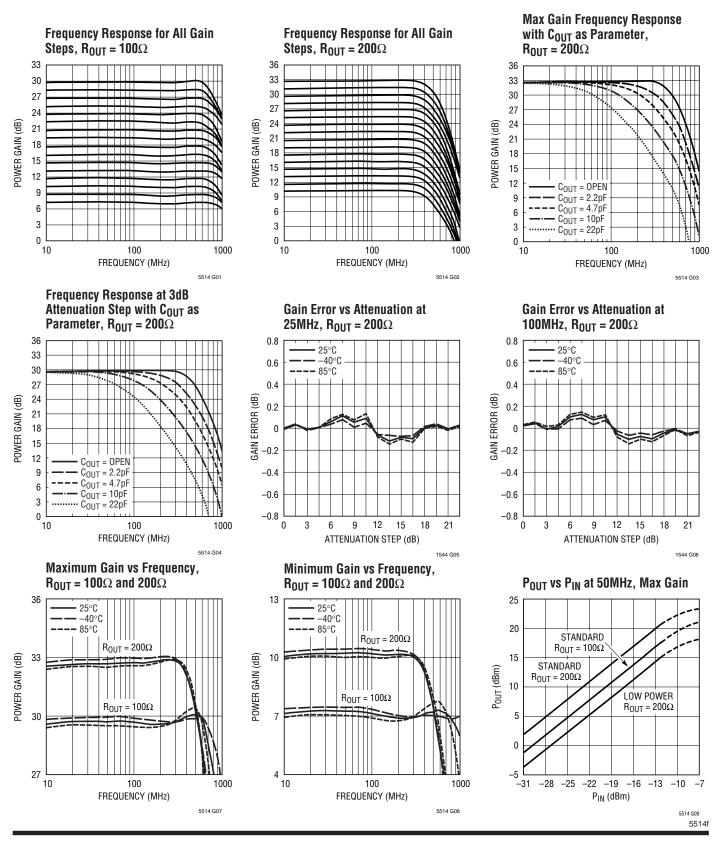

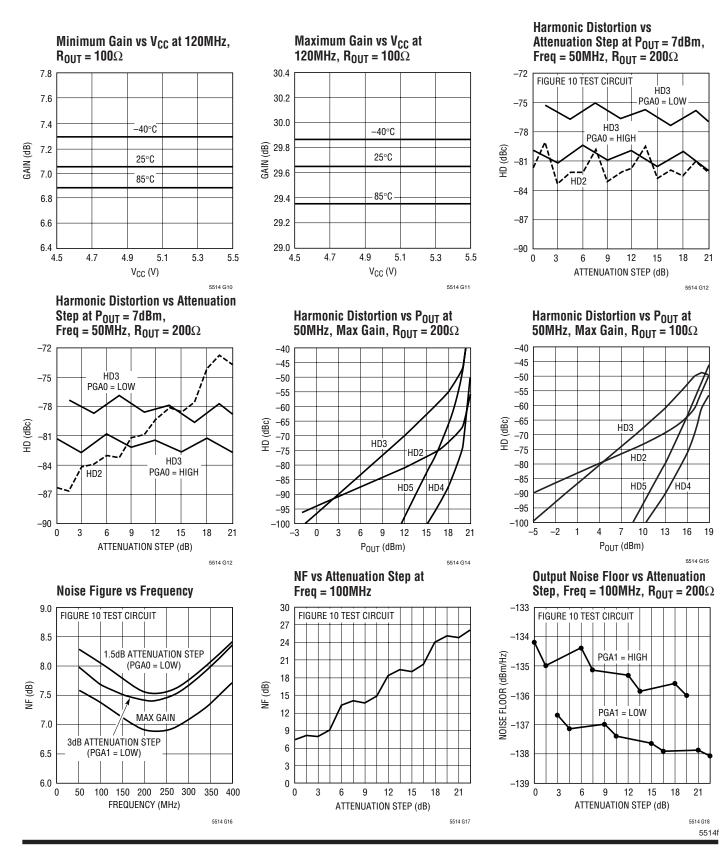

# **TYPICAL PERFORMANCE CHARACTERISTICS** (Standard Mode) $T_A = 25^{\circ}C$ , $V_{CC} = 5V$ , $V_{CCO} = 5V$ , ENA = ENB = 3V, control input levels $V_{IL} = 0.6V$ , $V_{IH} = 3V$ unless otherwise noted. (Test circuit shown in Figure 9)

www.datasheetall.com

**TYPICAL PERFORMANCE CHARACTERISTICS** (Standard Mode)  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V$ ,  $V_{CCO} = 5V$ , ENA = ENB = 3V, control input levels  $V_{IL} = 0.6V$ ,  $V_{IH} = 3V$  unless otherwise noted. (Test circuit shown in Figure 9)

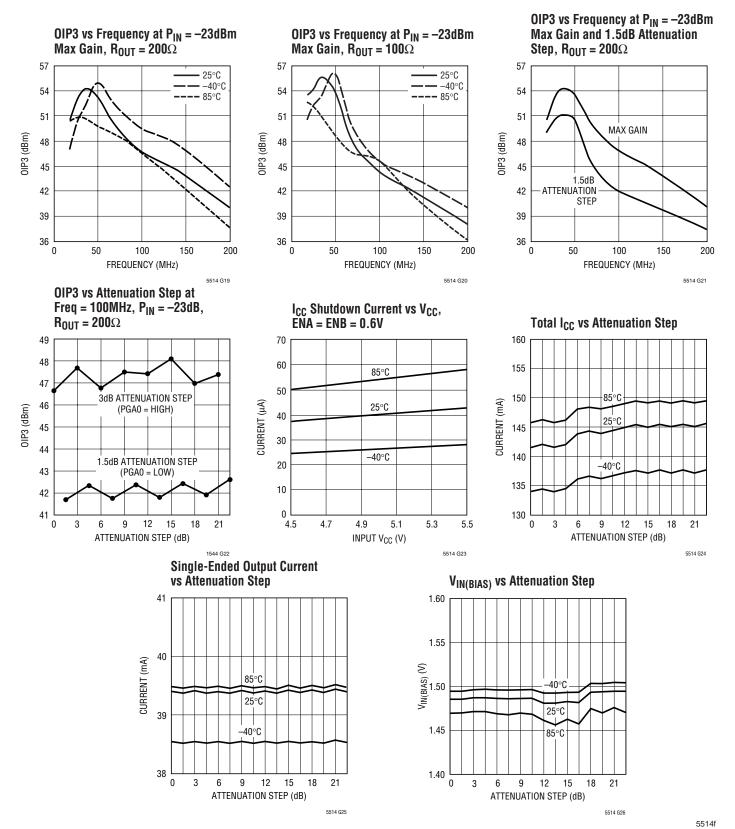

**TYPICAL PERFORMANCE CHARACTERISTICS** (Standard Mode) Two tones, 200kHz spacing,  $T_A = 25^{\circ}C$ , ENA = ENB = 5V,  $V_{CC} = 5V$ ,  $V_{CC} = 3V$ , control input levels  $V_{IL} = 0.6V$ ,  $V_{IH} = 3V$  unless otherwise noted. (Test circuit shown in Figure 10)

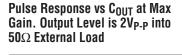

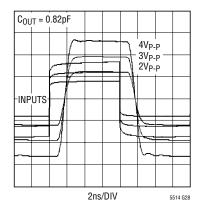

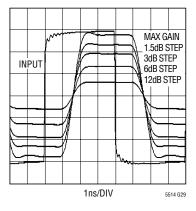

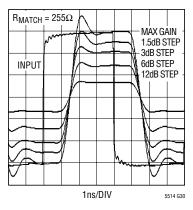

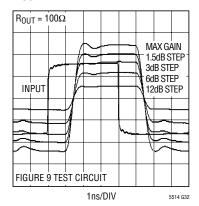

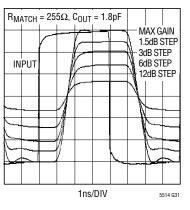

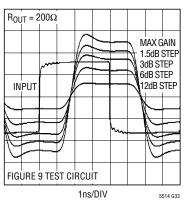

**TYPICAL PERFORMANCE CHARACTERISTICS** (Standard Mode)  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V$ ,  $V_{CCO} = 5V$ , ENA = ENB = 3V, control input levels  $V_{IL} = 0.6V$ ,  $V_{IH} = 3V$  unless otherwise noted. Test circuit shown in Figure 10 unless otherwise noted. Note 1: Subtract 0.75ns calibration delay from output plots to estimate the LT5514 group delay. Note 2: When specified,  $C_{OUT}$ is connected differentially across the LT5514 OUT<sup>+</sup>, OUT<sup>-</sup> output pins.

Pulse Response vs Output Level at Max Gain. Indicated Voltage Levels are into 50 $\Omega$  External Load

Pulse Response vs Attenuation, Output Level is 4V<sub>P-P</sub> at Max Gain into 50 $\Omega$  External Load

Pulse Response vs Attenuation, Output Level is 2V<sub>P-P</sub> at Max Gain into 50 $\Omega$  External Load

Pulse Response vs Attenuation, LT5514 Levels are:  $V_{IN} = 66mV_{P-P}$ , V<sub>OUT</sub> = 2V<sub>P-P</sub> at Max Gain

Pulse Response vs Attenuation, Output Level is 2VP-P at Max Gain into 50 $\Omega$  External Load

Pulse Response vs Attenuation, LT5514 Levels are:  $V_{IN} = 66mV_{P-P}$ , V<sub>OUT</sub> = 4V<sub>P-P</sub> at Max Gain

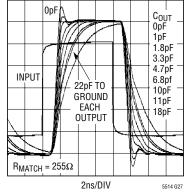

**TYPICAL PERFORMANCE CHARACTERISTICS** (Low Power Mode)  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V$ ,  $V_{CCO} = 5V$ , ENA = 3V, ENB = 0.6V or ENA = 0.6V, ENB = 3V, control input levels  $V_{IL} = 0.6V$ ,  $V_{IH} = 3V$  unless otherwise noted. (Test circuit shown in Figure 10)

NF vs Attenuation Step at

Freq = 100MHz

30

27

24

21

18 NF (dB)

15

12

**Output Noise Floor vs Attenuation** Step, Freq = 100MHz,  $R_{OUT}$  = 200 $\Omega$

Single-Ended Output Current vs Attenuation Step

Pulse Response vs Output Level at Max Gain. Indicated Voltage Levels are into 50 $\Omega$  External Load

VIN(BIAS) vs Attenuation Step 1.60 1.55 V<sub>IN(BIAS)</sub> (V) 1.50 40°C 25°C 1.45 85°C 1.40 0 3 6 9 12 15 18 21 ATTENUATION STEP (dB) 5514 G42 5514f

## PIN FUNCTIONS

**ENA (Pin 1):** Enable Pin for Amplifier A. When the input voltage is higher than 3V, amplifier A is turned on. When the input voltage is less than or equal to 0.6V, amplifier A is turned off. This pin is internally pulled to ground if not connected.

$V_{CC1}$  (Pin 2): Power Supply. This pin is internally connected to  $V_{CC2}$  (Pin 19). Decoupling capacitors (1000pF and 0.1µF for example) may be required in some applications.

GND (Pins 3, 4, 7, 8, 13, 14, 17, 18): Ground.

**IN<sup>+</sup> (Pin 5):** Positive Signal Input Pin with Internal DC Bias.

**IN<sup>-</sup> (Pin 6):** Negative Signal Input Pin with Internal DC Bias.

**PGA0 (Pin 9):** Amplifier PGA Control Input Pin for the 1.5dB Attenuation Step (see Programmable Gain table). Input is high when input voltage is greater than 3V. Input is low when input voltage is less than or equal to 0.6V. This pin is internally pulled to ground if not connected.

**PGA1 (Pin 10):** Amplifier PGA Control Input Pin for the 3dB Attenuation Step (see Programmable Gain table). Input is high when input voltage is greater than 3V. Input is low when input voltage is less than or equal to 0.6V. This pin is internally pulled to ground if not connected.

**PGA2 (Pin 11):** Amplifier PGA Control Input Pin for the 6dB Attenuation Step (see Programmable Gain table).

Input is high when input voltage is greater than 3V. Input is low when input voltage is less than or equal to 0.6V. This pin is internally pulled to ground if not connected.

**PGA3 (Pin 12):** Amplifier PGA Control Input Pin for 12dB Attenuation Step (see Programmable Gain table). Input is high when input voltage is greater than 3V. Input is low when input voltage is less than or equal to 0.6V. This pin is internally pulled to ground if not connected.

**OUT+ (Pin 15):** Positive Amplifier Output. A transformer with center tap tied to  $V_{CC}$  or a choke inductor is recommended to source the DC quiescent current.

$\textbf{OUT}^-$  (**Pin 16**): Negative Amplifier Output. A transformer with center tap tied to  $V_{CC}$  or a choke inductor is recommended to source the DC quiescent current.

$V_{CC2}\ (Pin\ 19):$  Power Supply. This pin is internally connected to  $V_{CC1}\ (Pin\ 2).$

**ENB (Pin 20):** Enable Pin for Amplifier B. When the input voltage is higher than 3V, amplifier B is turned on. When the input voltage is less than or equal to 0.6V, amplifier B is turned off. This pin is internally pulled to ground if not connected.

**Exposed Pad (Pin 21):** Ground. This pin must be soldered to the printed circuit board ground plane for good heat transfer.

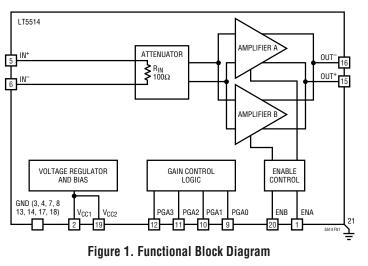

## **BLOCK DIAGRAM**

#### **Circuit Operation**

The LT5514 is a high linearity amplifier with high impedance output (Figure 1). It consists of the following sections:

- An input variable attenuator "gain-control" block with 100  $\!\Omega$  input impedance

- Two parallel, differential transconductance amplifiers, each with independent enable inputs

- An internal bias block with internal voltage regulator

- A gain control logic block

The LT5514 amplifier provides amplification with very low distortion using a linearized open-loop architecture. In contrast with high linearity amplifiers employing negative feedback, the LT5514 offers:

- Stable operation for any practical load

- A capacitive output reactance (not inductive) that provides peaking free AC response to capacitive loads

- Exceptional reverse isolation of -100dB at 50MHz and -78dB at 300MHz (package and board leakage limited)

The LT5514 is a transconductance amplifier and its operation can be understood conceptually as consisting of two steps: First, the input signal voltage is converted to an output current. The intermodulation distortion (in dBc) of the LT5514 output current is determined by the input signal level, and is almost independent of the output load conditions. Thus, the LT5514's input IP3 is also nearly independent of the output load.

Next, the external output load ( $R_{OUT}$ ) converts the output current to output voltage (or power). The LT5514's voltage and power gain both increase with increasing  $R_{OUT}$ . Accordingly, the output power and output IP3 also improve with increasing  $R_{OUT}$ . The actual output linearity performance in the application will thus be set by the choice of output load, as well as by the output network.

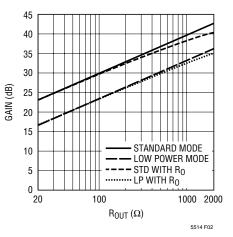

### **Maximum Gain Calculation**

The maximum power gain (with the OdB attenuation step) is:

$G_{PWR}(dB) = 10 \cdot \log(g_m^2 \cdot R_{IN} \cdot R_{OUT})$

where:

$g_m$  is the LT5514 transconductance = 0.3S in Standard mode (0.15S in Low Power mode).

$R_{IN}$  is the LT5514 differential input impedance  $\cong 108\Omega$  in Standard mode (122 $\Omega$  in Low Power mode). Input impedance matching is assumed.

$R_{OUT}$  is the external differential output impedance as seen by the LT5514's differential outputs.  $R_{OUT}$  should be distinguished from the actual load impedance,  $R_{LOAD}$ , which will typically be coupled to the LT5514 output by an impedance transformation network.

The power gain as a function of  $R_{OUT}$  is plotted in Figure 2. The ideal curves are straight lines. The curved lines indicate the roll-off due to the finite (noninfinite) output resistance of the LT5514.

Figure 2. Power Gain as a Function of  $R_{\text{OUT}}$

The actual available output power (as well as power gain and OIP3) will be reduced by losses in the output interface, consisting of:

- The insertion loss of the output impedance transformation network (for example the transformer insertion loss in Figure 6)

- About –3dB loss if a matching resistor (R<sub>MATCH</sub> in Figure 6) is used to provide output load impedance back-matching (for example when driving transmission lines)

#### Input Interface

For the lowest noise and highest linearity, the LT5514 should be driven with a differential input signal. Singleended drive will severely degrade linearity and noise performance.

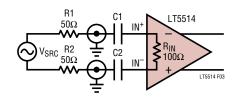

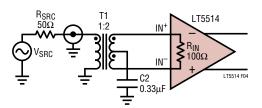

Example input matching networks are shown in Figures 3 and 4.

Input matching network design criteria are:

- DC block the LT5514 internal bias voltage (see Input Bias Voltage section for DC coupling information)

- Match the source impedance to the LT5514,  $R_{IN}\!\cong\!108\Omega$

- Provide well balanced differential input drive (capacitor C2 in Figure 4)

- Minimize insertion loss to avoid degrading the noise figure (NF)

Figure 3. Input Capacitively-Coupled to a Differential Source

Figure 4. Input Transformer-Coupled to a Single-Ended Source

### **Output Interface**

The output interface network provides an impedance transformation between the actual load impedance,  $R_{LOAD}$ , and the LT5514 output loading,  $R_{OUT}$ , chosen to maximize power or linearity, or to minimize output noise, or for some other criteria as explained in the following sections.

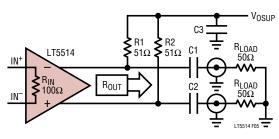

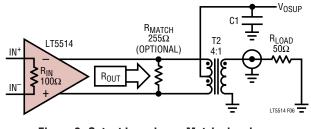

Two examples of output matching networks are shown in Figures 5 and 6 (as implemented in the LT5514 demo boards).

Figure 5. Output Impedance-Matched and Capacitively Coupled to a Differential Load

Note: In Figure 5, (choke) inductors may be placed in parallel with or used to replace resistors R1 and R2, thus eliminating the DC voltage drop across these resistors.

Figure 6. Output Impedance-Matched and Transformer-Coupled to a Single-Ended Load

Output network design criteria are:

- Provide DC isolation between the LT5514 DC output voltage and R<sub>LOAD</sub>.

- Provide a path for the output DC current from the output voltage source V<sub>OSUP</sub>.

- Provide an impedance transformation, if required, between the load impedance,  ${\sf R}_{\sf LOAD},$  and the optimum  ${\sf R}_{\sf OUT}$  loading.

- Set the bandwidth of the output network.

- Optional: Provide board output impedance matching using resistor  ${\rm R}_{\rm MATCH}$  (when driving a transmission line).

- Use high linearity passive parts to avoid introducing noninearity.

Note that there is a noise penalty of up to 6dB when using power delivered by only one output in Figure 5.

5514

#### **Clipping Free Operation**

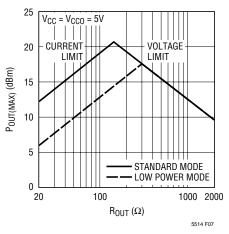

The LT5514 is a class A amplifier. To avoid signal distortion, the user must ensure that the LT5514 outputs do not enter into current or voltage limiting. The following discussion applies to standard mode operation at maximum gain.

To avoid current clipping, the output signal current should not exceed the DC quiescent current,  $I_{OUT} = 40$ mA (typical). Correspondingly, the maximum input voltage,  $V_{IN(MAX)}$ , is  $I_{OUT}/g_m = 133$ mV (peak). In power terms,  $P_{IN(MAX)} = -10.8$ dBm (assuming  $R_{IN} = 108\Omega$ ).

To avoid output voltage clipping (due to LT5514 output stage saturation or breakdown), the single-ended output voltage swing should stay within the specified limits; i.e.,  $2V \le V_{OUT} \le 8V$ . For a DC output bias of 5V, the maximum single ended swing will be 3Vpeak and the maximum differential swing will be 6Vpeak. The simultaneous onset of both current and voltage limiting occurs when  $R_{OUT} = 6Vpeak/40mA = 150\Omega$  (typ) for a maximum  $P_{OUT} = 20.8dBm$ . This calculation applies for a sinusoidal signal. For nonsinusoidal signals, use the appropriate crest factor to calculate the actual maximum power that avoids output clipping.

For nonoptimal R<sub>OUT</sub> values, the maximum available output power will be lower and can be calculated (considering current limiting for R<sub>OUT</sub> <  $150\Omega$ , and voltage limiting for R<sub>OUT</sub> >  $150\Omega$ ). The result of this calculation is shown in Figure 7.

The LT5514 input should not be overdriven (P\_{IN} > -10dBm). The consequences of overdrive are reduced

Figure 7. Maximum Output Power as a Function of  $\ensuremath{\mathsf{R}}_{\ensuremath{\mathsf{OUT}}}$

bandwidth and, when the frequency is greater than 50MHz, reduced output power.

#### **Input Bias Voltage**

The LT5514 IN<sup>+</sup>, IN<sup>-</sup> signal inputs are internally biased to 1.48V common mode when enabled, and to 1.26V in shutdown mode. These inputs are typically coupled by means of a capacitor or a transformer to a signal source, and impedance matching is assumed. In shutdown mode, the internal bias can handle up to 1 $\mu$ A leakage on the input coupling capacitors. This reduces the turn-on delay due to the input coupling RC time constant when exiting shutdown mode.

If DC coupling to the input is required, the external common mode bias should track the LT5514's internal common mode level. The DC current from the LT5514 inputs should not exceed  $I_{IN(SINK)} = -400\mu$ A and  $I_{IN(SOURCE)} = 800\mu$ A in Standard mode and half of these values in Low Power mode.

#### **Stability Considerations**

The LT5514's open-loop architecture allows it to drive any practical load. Note that LT5514 gain is proportional to the load impedance, and may exceed the reverse isolation at frequencies above 1GHz if the LT5514's outputs are left unloaded, with instability as the undesirable consequence. In such cases, placing a resistive differential load (e.g., 2k) or a small capacitor at the LT5514 outputs can be used to limit the maximum gain.

The LT5514 has about 30GHz gain-bandwidth product. Hence, attention must be paid to the printed circuit board layout to avoid output pin to input pin signal coupling (the evaluation board layout is a good example). Due to the LT5514's internal power supply regulator, external supply decoupling capacitors typically are not required. Likewise, decoupling capacitors on the LT5514 control inputs typically are not needed. Note, however, that the Exposed Pad on the LT5514 package must be soldered to a good ground plane on the PCB.

### PGA Function, Linearity and NF

As described in the Circuit Operation section, the LT5514 consists of a variable (step) attenuator followed by a high

gain output amplifier. The overall gain of the LT5514 is digitally controlled by means of four gain control pins with internal pull-down. Minimum gain is programmed when the gain control pins are set low or left floating. In shutdown mode, these PGA inputs draw <10 $\mu$ A leakage current, regardless of the applied voltage.

The 6dB and 12dB attenuation steps (PGA2 and PGA3) are implemented by switching the amplifier inputs to an input attenuator tap. The 3dB attenuation step (PGA1) changes the amplifier transconductance. The output IP3 is approximately independent of the PGA1, PGA2 and PGA3 gain settings. However, the 1.5dB attenuation step utilizes a current steering technique that disables the internal linearity compensation circuit, and the OIP3 can be reduced by as much as 6dB when PGA0 is low. Therefore, to achieve the LT5514's highest linearity performance, the PGA0 pin should be set high.

The LT5514 noise figure is 7.3dB in the maximum gain state. For the -3dB attenuation setting, the NF is 7.6dB. The noise figure increases in direct proportion to the amount of programmed gain reduction for the 1.5dB, 6dB and 12dB steps.

The output noise floor is proportional to the output load impedance,  $R_{OUT}$ . It is almost constant for PGA1 = high and for any PGA0, PGA2, PGA3 state. When PGA1 = low, the output noise floor is 2.7dB lower (see Typical Performance Characteristics).

#### **Other Linearity Considerations**

LT5514 linearity is a strong function of signal frequency. OIP3 decreases about 13dB for every octave of frequency increase above 100MHz.

As noted in the Circuit Operation section, at any given frequency and input level, the LT5514 provides a current output with fairly constant intermodulation distortion figure in dBc, regardless of the output load value. For higher  $R_{OUT}$  values, more gain and output power is available, and better OIP3 figures can be achieved. However, high  $R_{OUT}$  values are not easily implemented in practice, limited by the availability of high ratio output impedance transformation networks.

Linearity can also be limited by the output RC time constant (bandwidth limitations), particularly for high  $R_{OUT}$

values. A solution is outlined in the Bandpass Applications section.

The LT5514 linearity degrades when common mode signal is present. The input transformer center tap should be decoupled to ground to provide a balanced input differential signal and to avoid linearity degradation for high attenuation steps. When the signal frequency is lower than 50MHz, and there is significant common mode signal, then high attenuation settings may result in degraded linearity.

At signal frequencies below 100MHz, the LT5514's internal linearity compensation circuitry may provide "sweet spots" with very high OIP3, in excess of +60dBm. This almost perfect distortion correction cannot be sustained over the full operating temperature range and with variations of the LT5514 output load (complex impedance  $Z_{OUT}$ ). Users are advised to rely on data shown in the Typical Performance Characteristics curves to estimate the dependable linearity performance.

### Wideband Applications

At low frequencies, the value of the decoupling capacitors, choke inductors and choice of transformer will set the minimum frequency of operation. Output DC coupling is possible, but this typically reduces the LT5514's output DC bias voltage, and thus the output swing and available power.

At high frequencies, the output RC time constants set an upper limit to the maximum frequency of operation in the case of the wideband output networks presented so far. For example the LT5514 output capacitance,  $C_{OUT} = 1.9pF$ , and a pure resistive load,  $R_{OUT} = 200\Omega$ , will set the -3dB bandwidth to about 400MHz. In an actual application, the  $R_{LOAD} \bullet C_{LOAD}$  product may be even more restrictive. The use of wideband output networks will not only limit the bandwidth, but will also degrade linearity because part of the available power is wasted driving the capacitive load.

The LT5514's output reactance is capacitive. Therefore improved AC response is possible by using external series output inductors. When driving purely resistive loads, an inductor in series with the LT5514 output may help to achieve maximally flat AC response as exemplified in the characterization setup schematic (Figure 9).

For example, for  $R_{OUT}$  = 200 $\Omega$ , L1, L2 = 33nH results in 500MHz bandwidth.

The series inductor can extend the application bandwidth, but it provides no improvement in linearity performance.

Series inductance may also produce peaking in the AC response. This can be the case when (high Q) choke inductors are used in an output interface such as in Figure 5, and the PCB trace (connection) to the load is too long. Since the LT5514's output impedance is relatively high, the PCB trace acts as a series inductor. The most direct solution is to shorten the connection lines by placing the driver closer to the load. Another solution to flatten the AC response is to place resistance close to the LT5514 outputs. In this way the connection line behaves more like a terminated transmission line, and the AC peaking due to the capacitive load can be removed.

#### **Bandpass Applications**

For narrow band IF applications, the LT5514's output capacitance and the application load capacitance can be incorporated as part of an LC impedance transformation network, giving improved linearity performance for signal frequencies greater than 100MHz. Figure 8 is an example of such a network.

The network consists of two parallel resonant LC tank circuits critically coupled by capacitors C1 and C2. The  $R_{OUT}$  to  $R_{LOAD}$  transformation ratio in this particular implementation is 2. The choice of impedance transformation ratio is more flexible than in the wideband case.

The LC network is a bandpass filter, a useful feature in many applications.

A variety of bandpass matching network configurations are conceivable, depending on the requirements of the particular application. The design of these networks is facilitated by the fact that the LT5514 outputs are not destabilized by reactive loading.

Note that these LC networks may distort the output signal if their amplitude and phase response exhibit nonlinear behavior. For example, if resistors R1 and R2 in Figure 5 are replaced with LC resonant tank circuits, then severe OIP3 degradation may occur (e.g., 4dB to 6dB at 200MHz).

#### Low Output Noise Floor Applications

In some applications the maximum output noise floor is specified. The LT5514 output noise floor is elevated above the available noise power (-174dBm/Hz into  $50\Omega$ ) by the NF + Gain. Consequently, reduction of the LT5514's power gain is the only way to reduce the output noise floor.

In fixed gain applications, the LT5514 can be set to 3dB attenuation relative to maximum gain. As shown in the Typical Performance Characteristics, this gives a 2.8dB reduction in the output noise floor with no loss of linearity.

In general, the output noise floor can be reduced by decreasing  ${\rm R}_{\rm OUT}$  (and hence power gain), at the cost of reduced OIP3.

In some situations, it may be feasible to use two LT5514 parts in parallel. In this case, the effective  $g_m$  doubles,

Figure 8. Bandpass Output Transformation Network Example

allowing all impedances to be scaled downward by a factor of two. The NF and power gain remain the same in this case, but the OIP3 increases by 3dB. Then, with a further reduction of  $R_{OUT}$  by a factor of two, the gain and output noise floor decrease by 3dB, while yielding the same linearity as for one part. As an added benefit, two LT5514 parts in parallel can drive an  $R_{OUT}$  reduced by a factor of four, thus relaxing or eliminating the need in some cases for an output impedance transformation network.

#### Low Power Mode

As described in the Circuit Operation section, the LT5514 consists of two parallel gain blocks. These blocks are independently enabled or disabled. "Low Power mode" refers to circuit operation with only a single block enabled. An amplifier in Low Power mode will have the same basic characteristics as in Standard mode (both gain blocks enabled), except that the  $g_m$  decreases from 0.3S to 0.15S, and the maximum output current is halved. In Low Power mode, the standard LT5514 evaluation board will produce about 6dB less gain, (because the LT5514's  $g_m$  is reduced, while  $R_{IN}$  and  $R_{OUT}$  are the same) and 6dB lower OIP3.

#### LT5514 Characterization

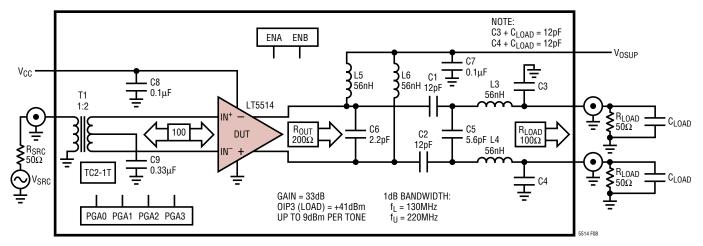

The LT5514's typical performance data are based on the test circuits shown in Figures 9 and 10. Figure 9 does not necessarily reflect the use of the LT5514 in an actual application. (For that, see the Application Boards section.)

Figure 9. Characterization Board (Simplified Schematic)

Rather, it represents a compromise that most accurately measures the actual operation of the part by itself, undistorted by the artifacts of the impedance transformation network, or by external bandwidth limiting factors. Balun transformers are used to interface with single-ended test equipment. Input and output resistive attenuators (not shown) provide broadband I/O impedance control. The L1, L2 inductors are selected for maximally flat AC output response.  $C_{OUT}$  (normally open) shows the placement of capacitive loading when this is specified as a characterization variable. The V<sub>CCO</sub> monitor pin allows setting the output DC level (5V typical) by adjusting voltage V<sub>OSUP</sub>.

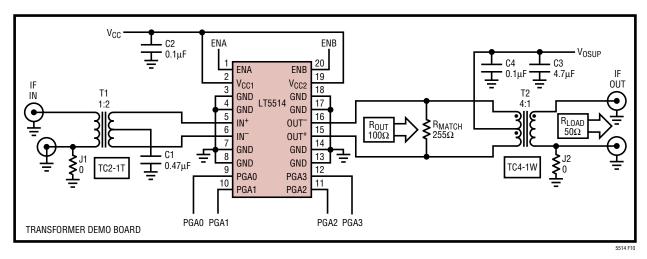

#### **Application (Demo) Boards**

The LT5514 demo boards are provided in the versions shown in Figure 10 (with output transformer) and Figure 11 (without output transformer). All I/O signal ports are matched to  $50\Omega$ . Moreover, 1k resistors (not shown) connect all six control pins (ENA, ENB, PGA0, PGA1, PGA2, PGA3) to V<sub>CC</sub>, such that the LT5514 is shipped in maximum gain state and with both amplifier blocks enabled (Standard mode).

The gain setting can be changed by connecting the control pins to ground. Test points (TP1, TP2, TP3) are provided to monitor the input and output DC bias voltage. Jumper J1 can be removed when differential input is desired, but

in that case, T1 should be changed to a 1:1 center-tap transformer to preserve  $50\Omega$  input matching. The demo board is shipped with optional output back-matching resistor  $R_{MATCH} = 255\Omega$ . This results in a net output load,  $R_{OUT} = 100\Omega$ , presented to the LT5514.

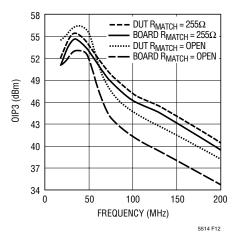

The Output Transformer Application Board (Figure 10) is one example of an output impedance transformation (T2 transformer). For the Typical Performance Characteristics curves, all linearity tests are performed on this board. By removing  $R_{MATCH}$ , the performance with  $R_{OUT}$ = 200 $\Omega$  can be evaluated (provided the lack of impedance back-matching is suitably remedied). Measured OIP3 for both cases,  $R_{OUT}$  = 100 $\Omega$  and 200 $\Omega$ , is shown in Figure 12.

Figure 12. Typical OIP3 for Transformer Board

5514f

At high frequency, the difference between the top and bottom curves in Figure 12 is simply power loss. Starting from the LT5514 intrinsic performance at  $R_{OUT} = 200\Omega$  (top curve), the next lower curve takes into account the transformer insertion loss. The next curve below this shows the LT5514 OIP3 with  $R_{OUT} = 100\Omega$ . The bottom curve in the plot includes the effects of transformer insertion loss, with  $R_{OUT} = 100\Omega$ , and the additional effect of loss due to  $R_{MATCH}$ .

The transformer board can provide a differential output when Jumper J2 is removed.

The Wideband Differential Output Application Board (Figure 11) is an example of direct coupling (no transformer) to the load, and has wider output bandwidth. This board gives direct access to the LT5514's output pins, and was used for stability tests. Higher  $V_{OSUP}$  (7V) is required to compensate for the DC voltage drop on R1 and R2. Use TP2, TP3 to monitor the actual LT5514 output bias voltage. By replacing R1 and R2 with inductors, this board can operate with a 5V supply. However, this may limit the minimum signal frequency. For example, an 820nH choke inductor will limit the lowest signal frequency to 40MHz.

### PACKAGE DESCRIPTION

## **RELATED PARTS**

| PART NUMBER                                   | DESCRIPTION                                                            | COMMENTS                                                                                                                 |  |  |  |  |

|-----------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Infrastructure                                |                                                                        |                                                                                                                          |  |  |  |  |

| LT5511                                        | High Linearity Upconverting Mixer                                      | RF Output to 3GHz, 17dBm IIP3, Integrated LO Buffer                                                                      |  |  |  |  |

| LT5512                                        | DC-3GHz High Signal Level Downconverting Mixer                         | DC to 3GHz, 21dBm IIP3, Integrated LO Buffer                                                                             |  |  |  |  |

| LT5515                                        | 1.5GHz to 2.5GHz Direct Conversion Quadrature Demodulator              | 20dBm IIP3, Integrated LO Quadrature Generator                                                                           |  |  |  |  |

| LT5516                                        | 0.8GHz to 1.5GHz Direct Conversion Quadrature Demodulator              | 21.5dBm IIP3, Integrated LO Quadrature Generator                                                                         |  |  |  |  |

| LT5517                                        | 40MHz to 900MHz Quadrature Demodulator                                 | 21dBm IIP3, Integrated LO Quadrature Generator                                                                           |  |  |  |  |

| LT5519                                        | 0.7GHz to 1.4GHz High Linearity Upconverting Mixer                     | 17.1dBm IIP3 at 1GHz, Integrated RF Output Transformer with 50 $\Omega$ Matching, Single-Ended LO and RF Ports Operation |  |  |  |  |

| LT5520                                        | 1.3GHz to 2.3GHz High Linearity Upconverting Mixer                     | 15.9dBm IIP3 at 1.9GHz, Integrated RF Output Transformer with 50C<br>Matching, Single-Ended LO and RF Ports Operation    |  |  |  |  |

| LT5522                                        | 600MHz to 2.7GHz High Signal Level Downconverting Mixer                | 4.5V to 5.25V Supply, 25dBm IIP3 at 900MHz, NF = 12.5dB, $50\Omega$ Single-Ended RF and LO Ports                         |  |  |  |  |

| <b>RF Power Detec</b>                         | tors                                                                   |                                                                                                                          |  |  |  |  |

| LT5504 800MHz to 2.7GHz RF Measuring Receiver |                                                                        | 80dB Dynamic Range, Temperature Compensated, 2.7V to 5.25V Supply                                                        |  |  |  |  |

| LTC <sup>®</sup> 5505                         | RF Power Detectors with >40dB Dynamic Range                            | 300MHz to 3GHz, Temperature Compensated, 2.7V to 6V Supply                                                               |  |  |  |  |

| LTC5507                                       | 100kHz to 1000MHz RF Power Detector                                    | 100kHz to 1GHz, Temperature Compensated, 2.7V to 6V Supply                                                               |  |  |  |  |

| LTC5508                                       | 300MHz to 7GHz RF Power Detector                                       | 44dB Dynamic Range, Temperature Compensated, SC70 Package                                                                |  |  |  |  |

| LTC5509                                       | 300MHz to 3GHz RF Power Detector                                       | 36dB Dynamic Range, Low Power Consumption, SC70 Package                                                                  |  |  |  |  |

| LTC5530                                       | 300MHz to 7GHz Precision RF Power Detector                             | Precision $V_{\mbox{OUT}}$ Offset Control, Shutdown, Adjustable Gain                                                     |  |  |  |  |

| LTC5531                                       | 300MHz to 7GHz Precision RF Power Detector                             | Precision $V_{\mbox{OUT}}$ Offset Control, Shutdown, Adjustable Offset                                                   |  |  |  |  |

| LTC5532                                       | 300MHz to 7GHz Precision RF Power Detector                             | Precision $V_{\mbox{OUT}}$ Offset Control, Adjustable Gain and Offset                                                    |  |  |  |  |

| Low Voltage RF                                | Building Blocks                                                        |                                                                                                                          |  |  |  |  |

| LT5500                                        | 1.8GHz to 2.7GHz Receiver Front End                                    | 1.8V to 5.25V Supply, Dual-Gain LNA, Mixer, LO Buffer                                                                    |  |  |  |  |

| LT5502                                        | 400MHz Quadrature IF Demodulator with RSSI                             | 1.8V to 5.25V Supply, 70MHz to 400MHz IF, 84dB Limiting Gair<br>90dB RSSI Range                                          |  |  |  |  |

| LT5503                                        | 1.2GHz to 2.7GHz Direct IQ Modulator and<br>Upconverting Mixer         | 1.8V to 5.25V Supply, Four-Step RF Power Control,<br>120MHz Modulation Bandwidth                                         |  |  |  |  |

| LT5506                                        | 500MHz Quadrature IF Demodulator with VGA                              | 1.8V to 5.25V Supply, 40MHz to 500MHz IF, –4dB to 57dB<br>Linear Power Gain, 8.8MHz Baseband Bandwidth                   |  |  |  |  |

| LT5546                                        | 500MHz Ouadrature IF Demodulator with VGA and 17MHz Baseband Bandwidth | 17MHz Baseband Bandwidth, 40MHz to 500MHz IF, 1.8V to 5.25V<br>Supply, –7dB to 56dB Linear Power Gain                    |  |  |  |  |