### MicroConverter<sup>®</sup> Multichannel 24-/16-Bit ADCs with Embedded 62 kB Flash and Single-Cycle MCU

# **ADuC845**

#### **FEATURES**

High resolution  $\Sigma$ - $\Delta$  ADCs 2 independent 24-bit ADCs on the ADuC845 Single 24-bit ADC on the ADuC847 and single 16-bit ADC on the ADuC848 Up to 10 ADC input channels on all devices 24-bit no missing codes 22-bit rms (19.5 bit p-p) effective resolution Offset drift 10 nV/°C, gain drift 0.5 ppm/°C chop enabled Memory 62-kbyte on-chip Flash/EE program memory 4-kbyte on-chip Flash/EE data memory Flash/EE, 100-year retention, 100 kcycle endurance 3 levels of Flash/EE program memory security In-circuit serial download (no external hardware) High speed user download (5 sec) 2304 bytes on-chip data RAM 8051-based core 8051-compatible instruction set High performance single-cycle core 32 kHz external crystal **On-chip programmable PLL (12.58 MHz max)** 3 × 16-bit timer/counter 24 programmable I/O lines, plus 8 analog or digital input lines 11 interrupt sources, two priority levels Dual data pointer, extended 11-bit stack pointer **On-chip peripherals** Internal power-on reset circuit 12-bit voltage output DAC Dual 16-bit Σ-Δ DACs On-chip temperature sensor (ADuC845 only) Dual excitation current sources (200 µA) Time interval counter (wake-up/RTC timer) UART, SPI®, and I<sup>2</sup>C<sup>®</sup> serial I/O High speed dedicated baud rate generator (incl. 115,200) Watchdog timer (WDT) Power supply monitor (PSM)

#### Power

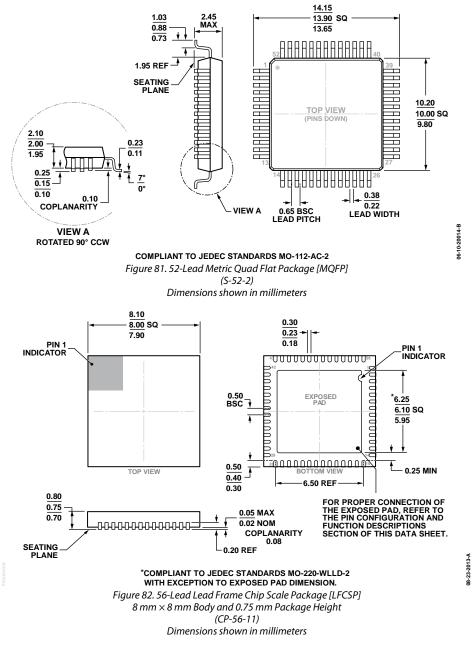

Normal: 4.8 mA max at 3.6 V (core CLK = 1.57 MHz) Power-down: 20  $\mu$ A max with wake-up timer running Specified for 3 V and 5 V operation Package and temperature range: 52-lead MQFP (14 mm × 14 mm), -40°C to +125°C 56-lead LFCSP (8 mm × 8 mm), -40°C to +85°C

#### **APPLICATIONS**

Multichannel sensor monitoring Industrial/environmental instrumentation Weigh scales, pressure sensors, temperature monitoring Portable instrumentation, battery-powered systems Data logging, precision system monitoring

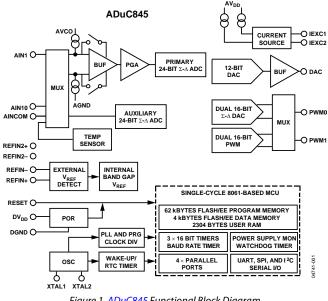

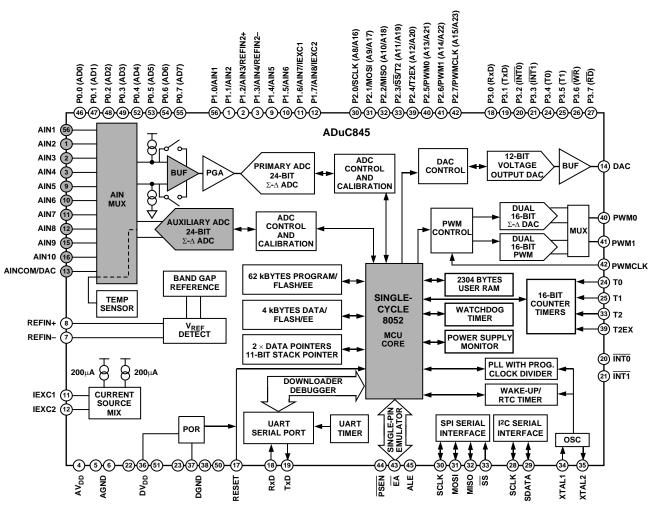

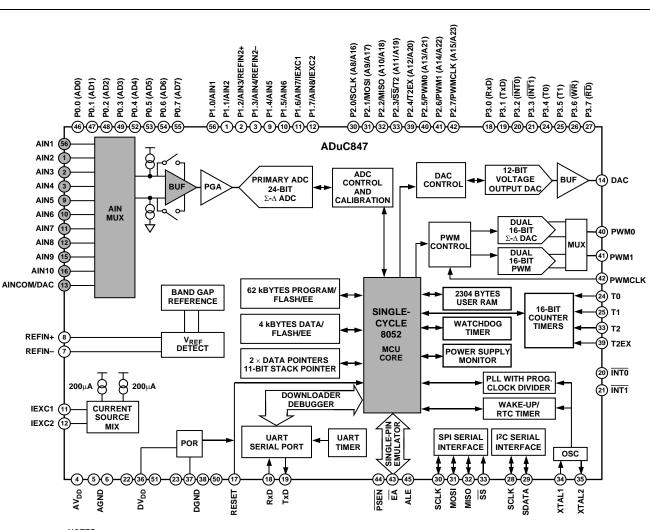

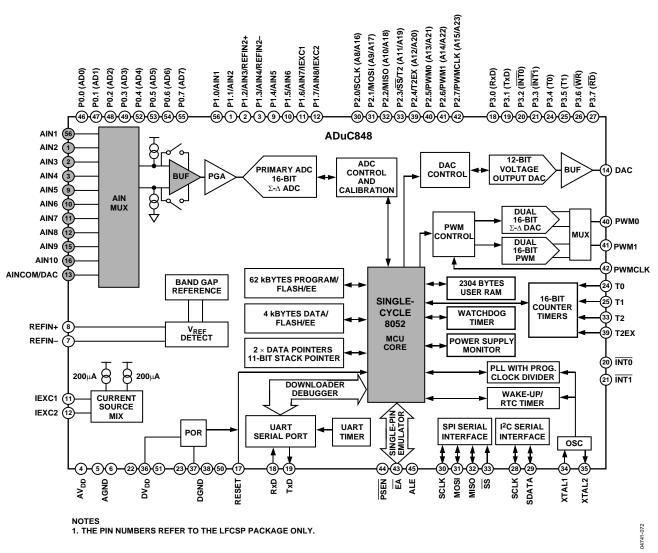

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1. ADuC845 Functional Block Diagram

#### Rev. D

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2004–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| Revision History                             |

| Specifications                               |

| Abosolute Maximum Ratings10                  |

| ESD Caution10                                |

| Pin Configurations and Function Descriptions |

| General Description                          |

| 8052 Instruction Set                         |

| Timer Operation                              |

| ALE                                          |

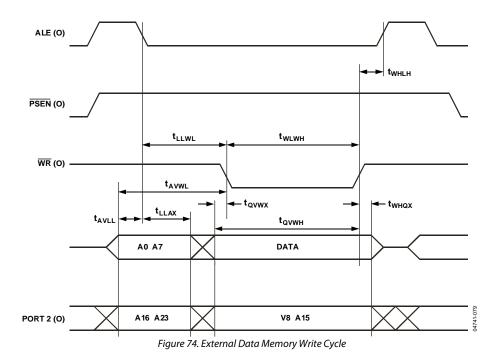

| External Memory Access                       |

| Complete SFR Map19                           |

| Functional Description                       |

| 8051 Instruction Set 20                      |

| Memory Organization                          |

| Special Function Registers (SFRs)            |

| ADC Circuit Information26                    |

| Auxiliary ADC (ADuC845 Only)                 |

| Reference Inputs                             |

| Burnout Current Sources                      |

| Reference Detect Circuit                     |

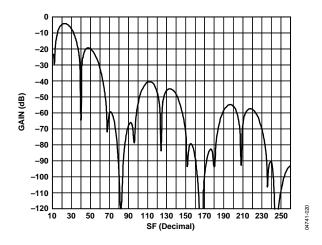

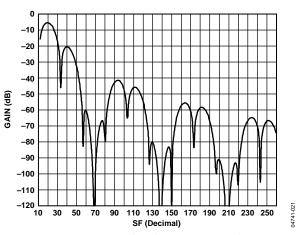

| Sinc Filter Register (SF)                    |

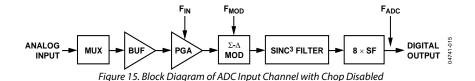

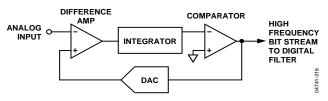

| $\Sigma$ - $\Delta$ Modulator                |

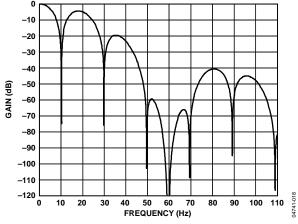

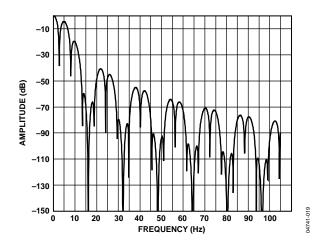

| Digital Filter                               |

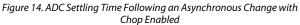

| ADC Chopping                                 |

| Calibration                                  |

| Programmable Gain Amplifier                  |

| Bipolar/Unipolar Configuration               |

| Data Output Coding                           |

| Excitation Currents                          |

| ADC Power-On                                       | . 36 |

|----------------------------------------------------|------|

| Typical Performance Characteristics                | . 37 |

| Functional Description                             | . 39 |

| ADC SFR Interface                                  | . 39 |

| ADCSTAT (ADC Status Register)                      | . 40 |

| ADCMODE (ADC Mode Register)                        | . 41 |

| ADC0CON1 (Primary ADC Control Register)            | . 43 |

| ADC0CON2 (Primary ADC Channel Select Register)     | . 44 |

| SF (ADC Sinc Filter Control Register)              | . 46 |

| ICON (Excitation Current Sources Control Register) | . 47 |

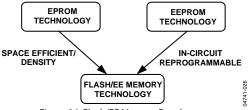

| Nonvolatile Flash/EE Memory Overview               | . 48 |

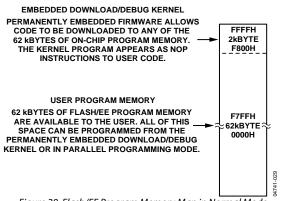

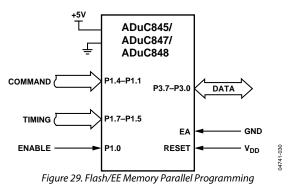

| Flash/EE Program Memory                            | . 49 |

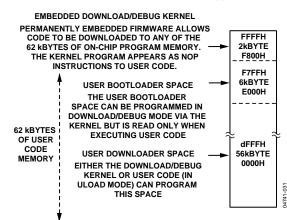

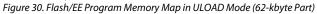

| User Download Mode (ULOAD)                         | . 50 |

| Using Flash/EE Data Memory                         | . 51 |

| Flash/EE Memory Timing                             | . 52 |

| DAC Circuit Information                            | . 53 |

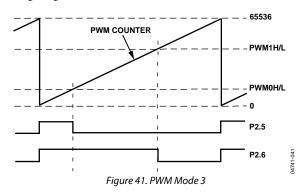

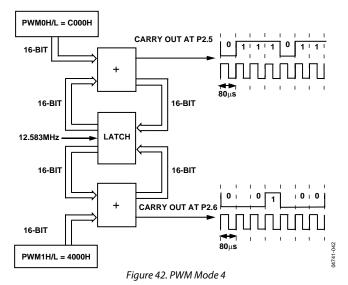

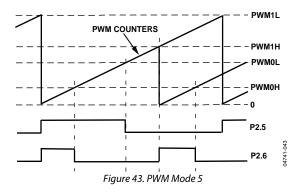

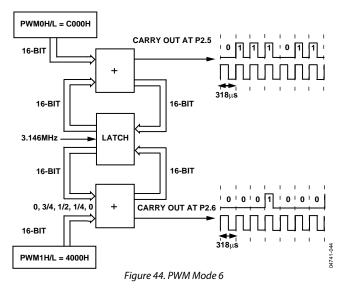

| Pulse-Width Modulator (PWM)                        | . 55 |

| On-Chip PLL (PLLCON)                               | . 60 |

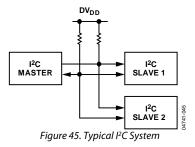

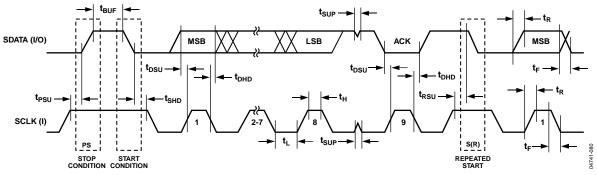

| I²C Serial Interface                               | . 61 |

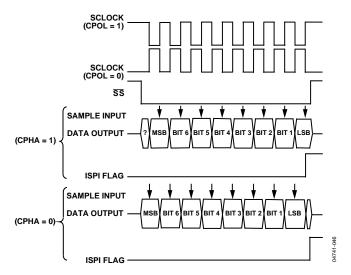

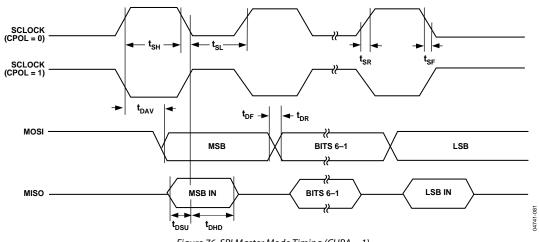

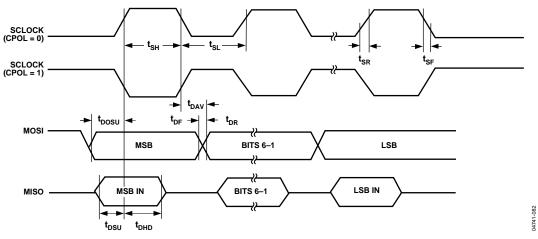

| SPI Serial Interface                               | . 63 |

| Using the SPI Interface                            | . 66 |

| Dual Data Pointers                                 | . 67 |

| Power Supply Monitor                               | . 68 |

| Watchdog Timer                                     | . 69 |

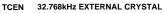

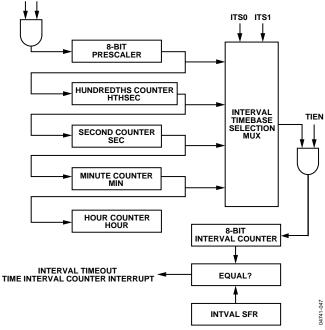

| Time Interval Counter (TIC)                        | . 70 |

| 8052-Compatible On-Chip Peripherals                | . 73 |

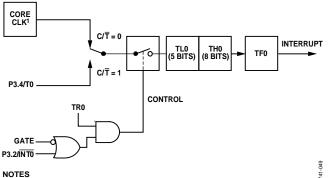

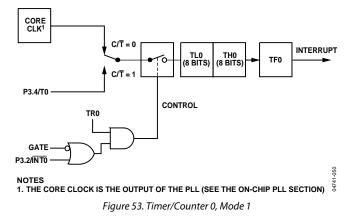

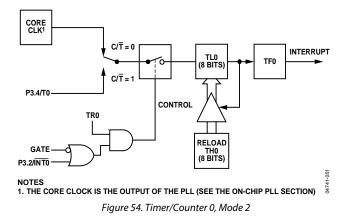

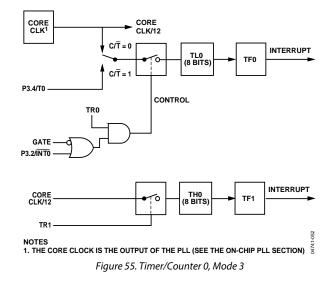

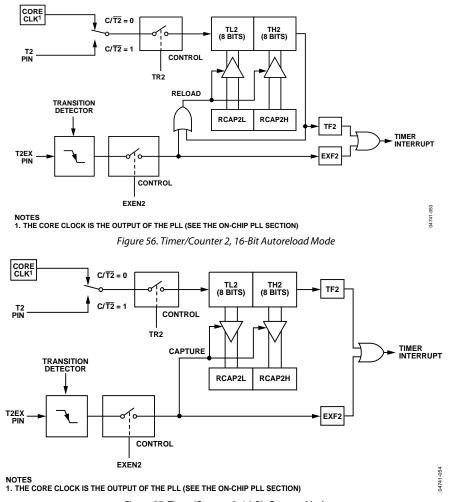

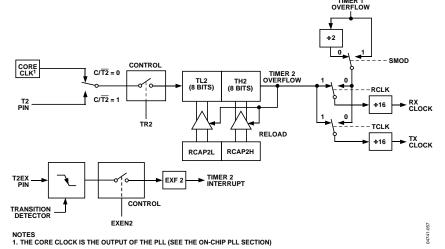

| Timers/Counters                                    | . 75 |

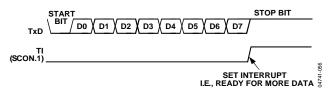

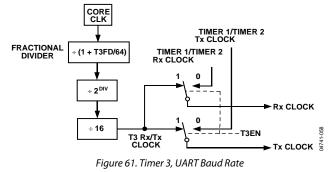

| UART Serial Interface                              | . 80 |

| Interrupt System                                   | . 87 |

| Interrupt Priority                                 | . 88 |

| Interrupt Vectors                                  | . 88 |

| Hardware Design Considerations             | 89 |

|--------------------------------------------|----|

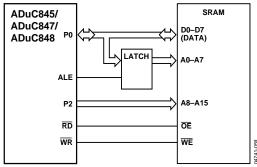

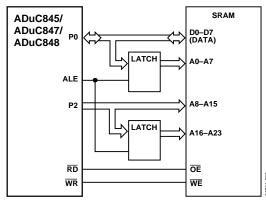

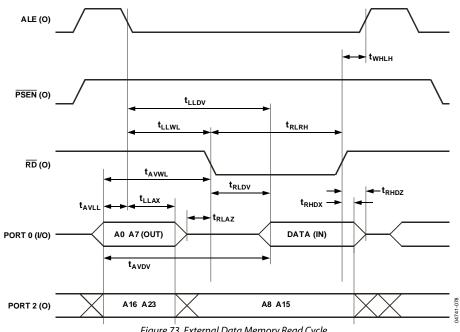

| External Memory Interface                  | 89 |

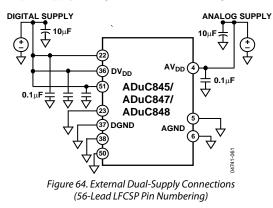

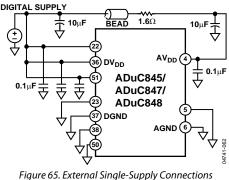

| Power Supplies                             | 89 |

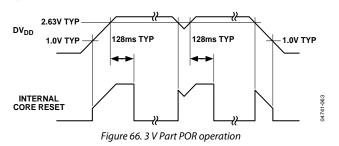

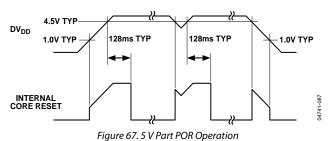

| Power-On Reset Operation                   | 90 |

| Power Consumption                          | 90 |

| Power-Saving Modes                         | 90 |

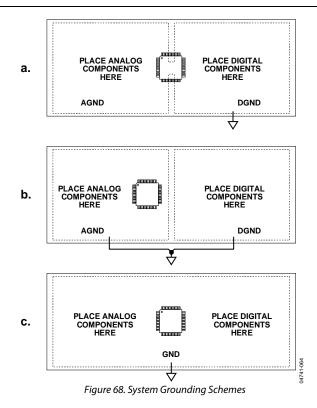

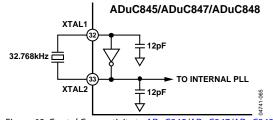

| Grounding and Board Layout Recommendations | 91 |

### **REVISION HISTORY**

#### 5/2016—Rev. C to Rev. D

| Changed uC004 to AN-1074   | . Throughout |

|----------------------------|--------------|

| Updated Outline Dimensions | 108          |

| Changes to Ordering Guide  | 109          |

#### 12/2012-Rev. B to Rev. C

| Changes to Figure 3 and Table 3                                     | 11  |

|---------------------------------------------------------------------|-----|

| Changes to Burnout Current Sources Section                          | 32  |

| Change to ADCMODE (ADC Mode Register) Section                       | 42  |

| Changes to Mode 4 (Dual NRZ 16-Bit $\Sigma$ - $\Delta$ DAC) Section | 58  |

| Change to Hardware Slave Mode Section                               | 63  |

| Updated Outline Dimensions                                          | 104 |

| Changes to Ordering Guide                                           |     |

|                                                                     |     |

#### 2/2005—Rev. A to Rev. B

| Changes to Figure 1                                     | 1  |

|---------------------------------------------------------|----|

| Changes to the Burnout Current Sources Section          | 32 |

| Changes to the Excitation Currents Section              | 36 |

| Changes to Table 30                                     | 47 |

| Changes to the Flash/EE Memory on the ADuC845, ADuC847, |    |

| ADuC848 Section                                         | 48 |

| Changes to Figure 39                                    | 57 |

| Changes to On-Chip PLL (PLLCON) Section                 | 60 |

| Added 3 V Part Section Heading                          | 88 |

| Added 5 V Part Section                                  | 88 |

| Changes to Figure 70                                    | 91 |

| Changes to Figure 71                                    | 93 |

|                                                         |    |

| Other Hardware Considerations      | 92  |

|------------------------------------|-----|

| QuickStart Development System      | 96  |

| QuickStart-PLUS Development System | 96  |

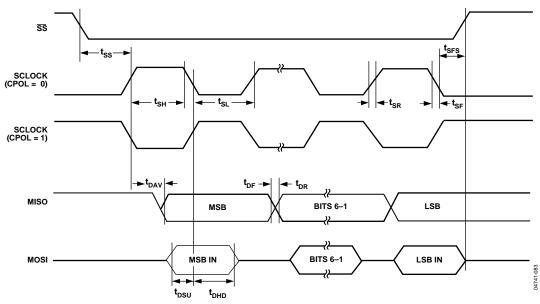

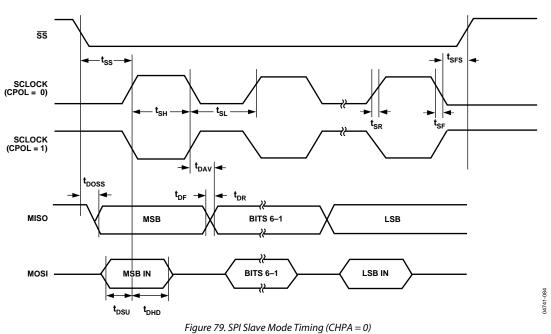

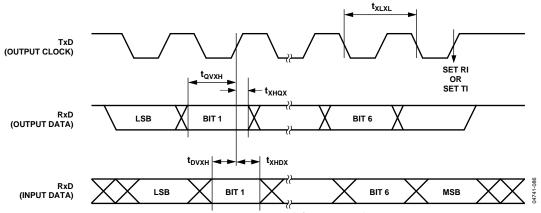

| Timing Specifications              | 97  |

| Outline Dimensions                 | 106 |

| Ordering Guide                     | 107 |

#### 6/2004—Rev. 0 to Rev. A

| Changes to Figure 5                                     | 17 |

|---------------------------------------------------------|----|

| Changes to Figure 6                                     | 18 |

| Changes to Figure 7                                     |    |

| Changes to Table 5                                      |    |

| Changes to Table 24                                     | 41 |

| Changes to Table 25                                     |    |

| Changes to Table 26                                     |    |

| Changes to Table 27                                     |    |

| Changes to User Download Mode Section                   |    |

| Added Figure 51 and Renumbered Subsequent Figures       |    |

| Edits to the DACH/DACL Data Registers Section           | 53 |

| Changes to Table 34                                     |    |

| Added SPIDAT: SPI Data Register Section                 |    |

| Changes to Table 42                                     |    |

| Changes to Table 43                                     | 68 |

| Changes to Table 44                                     |    |

| Changes to Table 45                                     | 71 |

| Changes to Table 50                                     |    |

| Changes to Timer/Counter 0 and 1 Data Registers Section |    |

| Changes to Table 54                                     | 80 |

| Added the SBUF-UART Serial Port Data Register Section   | 80 |

| Addition to the Timer 3 Generated Baud Rates Section    | 83 |

| Added Table 57 and Renumbered Subsequent Tables         | 84 |

| Changes to Table 61                                     | 86 |

4/2004—Revision 0: Initial Version

# ADuC845

# SPECIFICATIONS<sup>1</sup>

$AV_{DD} = 2.7 \text{ V}$  to 3.6 V or 4.75 V to 5.25 V,  $DV_{DD} = 2.7 \text{ V}$  to 3.6 V or 4.75 V to 5.25 V, REFIN(+) = 2.5 V, REFIN(-) = AGND; AGND = DGND = 0 V; XTAL1/XTAL2 = 32.768 kHz crystal; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Input buffer on for primary ADC, unless otherwise noted. Core speed = 1.57 MHz (default CD = 3), unless otherwise noted.

| Parameter                                         | Min       | Тур                                   | Max  | Unit              | Test Conditions/Comments                                                                                                   |

|---------------------------------------------------|-----------|---------------------------------------|------|-------------------|----------------------------------------------------------------------------------------------------------------------------|

| PRIMARY ADC                                       |           |                                       |      |                   |                                                                                                                            |

| Conversion Rate                                   | 5.4       |                                       | 105  | Hz                | Chop on (ADCMODE.3 = $0$ )                                                                                                 |

|                                                   | 16.06     |                                       | 1365 | Hz                | Chop off (ADCMODE.3 = 1)                                                                                                   |

| No Missing Codes <sup>2</sup>                     | 24        |                                       |      | Bits              | $\leq$ 26.7 Hz update rate with chop enabled                                                                               |

| -                                                 | 24        |                                       |      | Bits              | ≤80.3 Hz update rate with chop disabled                                                                                    |

| Resolution (ADuC845/ADuC847)                      | See Table | 11 and Table 1                        | 5    |                   |                                                                                                                            |

| Resolution (ADuC848)                              | See Table | 13 and Table 1                        | 7    |                   |                                                                                                                            |

| Output Noise (ADuC845/ADuC847)                    | See Table | e 10 and Table 14                     | 4    | μV (rms)          | Output noise varies with selected update rates gain range, and chop status.                                                |

| Output Noise (ADuC848)                            | See Table | e 12 and Table 10                     | 5    | μV (rms)          | Output noise varies with selected update rates gain range, and chop status.                                                |

| Integral Nonlinearity                             |           |                                       | ±15  | ppm of FSR        | 1 LSB <sub>16</sub>                                                                                                        |

| Offset Error <sup>3</sup>                         |           | ±3                                    |      | μV                | Chop on                                                                                                                    |

|                                                   |           |                                       |      |                   | Chop off, offset error is in the order of the noise<br>for the programmed gain and update rate<br>following a calibration. |

| Offset Error Drift vs. Temperature <sup>2</sup>   |           | ±10                                   |      | nV/°C             | Chop on (ADCMODE.3 = $0$ )                                                                                                 |

|                                                   |           | ±200                                  |      | nV/°C             | Chop off (ADCMODE.3 = 1)                                                                                                   |

| Full-Scale Error <sup>4</sup>                     |           |                                       |      |                   |                                                                                                                            |

| ADuC845/ADuC847                                   |           | ±10                                   |      | μV                | ±20 mV to ±2.56 V                                                                                                          |

| ADuC848                                           |           | ±10                                   |      | μV                | ±20 mV to ±640 mV                                                                                                          |

|                                                   |           | ±0.5                                  |      | LSB <sub>16</sub> | ±1.28 V to ±2.56 V                                                                                                         |

| Gain Error Drift vs. Temperature <sup>4</sup>     |           | ±0.5                                  |      | ppm/°C            |                                                                                                                            |

| Power Supply Rejection                            |           |                                       |      |                   |                                                                                                                            |

|                                                   | 80        |                                       |      | dB                | AIN = 1 V, $\pm 2.56$ V, chop enabled                                                                                      |

|                                                   |           | 113                                   |      | dB                | $AIN = 7.8 \text{ mV}, \pm 20 \text{ mV}, \text{ chop enabled}$                                                            |

|                                                   |           | 80                                    |      | dB                | AIN = 1 V, $\pm 2.56$ V, chop disabled <sup>2</sup>                                                                        |

| PRIMARY ADC ANALOG INPUTS                         |           |                                       |      |                   |                                                                                                                            |

| Differential Input Voltage Ranges <sup>5, 6</sup> |           |                                       |      |                   | Gain = 1 to 128                                                                                                            |

| Bipolar Mode (ADC0CON1.5 = 0)                     |           | $\pm 1.024 \times$                    |      | V                 | $V_{REF} = REFIN(+) - REFIN(-) \text{ or } REFIN2(+) -$                                                                    |

|                                                   |           | V <sub>REF</sub> /GAIN                |      |                   | REFIN2(–) (or Int 1.25 V <sub>REF</sub> )                                                                                  |

| Unipolar Mode (ADC0CON1.5 = 1)                    |           | 0 – 1.024 ×<br>V <sub>REF</sub> /GAIN |      | V                 | $V_{REF} = REFIN(+) - REFIN(-) \text{ or } REFIN2(+) - REFIN2(-) \text{ (or Int 1.25 } V_{REF})$                           |

| ADC Range Matching                                |           | ±2                                    |      | μV                | AIN = 18 mV, chop enabled                                                                                                  |

| Common-Mode Rejection DC                          |           |                                       |      |                   | Chop enabled, chop disabled                                                                                                |

| On AIN                                            | 95        |                                       |      | dB                | $AIN = 7.8 \text{ mV}$ , range = $\pm 20 \text{ mV}$                                                                       |

|                                                   |           | 113                                   |      | dB                | $AIN = 1 V$ , range = $\pm 2.56 V$                                                                                         |

| Common-Mode Rejection<br>50 Hz/60 Hz <sup>2</sup> |           |                                       |      |                   | 50 Hz/60 Hz $\pm$ 1 Hz, 16.6 Hz and 50 Hz update rate, chop enabled, REJ60 enabled                                         |

| On AIN                                            | 95        |                                       |      | dB                | $AIN = 7.8 \text{ mV}$ , range = $\pm 20 \text{ mV}$                                                                       |

|                                                   | 90        |                                       |      | dB                | $AIN = 1 V$ , range $= \pm 2.56 V$                                                                                         |

# ADuC845

| Parameter                                         | Min                     | Тур             | Max                       | Unit              | Test Conditions/Comments                                                               |

|---------------------------------------------------|-------------------------|-----------------|---------------------------|-------------------|----------------------------------------------------------------------------------------|

| Normal Mode Rejection 50 Hz/60 Hz <sup>2</sup>    |                         |                 |                           |                   |                                                                                        |

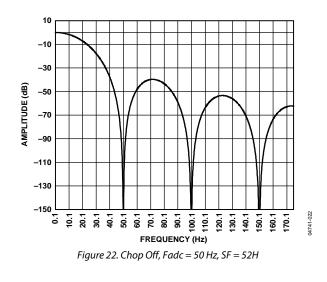

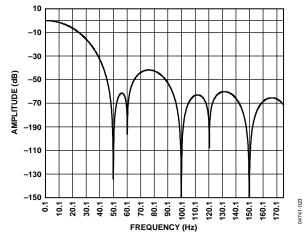

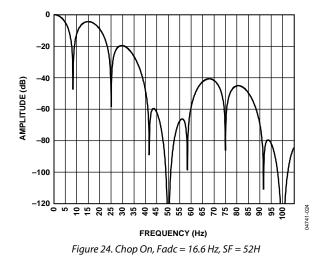

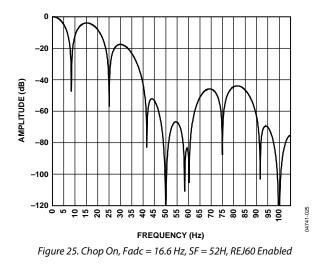

| On AIN                                            | 75                      |                 |                           | dB                | 50 Hz/60 Hz ± 1 Hz, 16.6 Hz Fadc, SF = 52H, chop<br>on, REJ60 on                       |

|                                                   | 100                     |                 |                           | dB                | 50 Hz $\pm$ 1 Hz, 16.6 Hz Fadc, SF = 52H, chop on                                      |

|                                                   | 67                      |                 |                           | dB                | 50 Hz/60 Hz ± 1 Hz, 50 Hz Fadc, SF = 52H, chop<br>off, REJ60 on                        |

|                                                   | 100                     |                 |                           | dB                | 50 Hz $\pm$ 1 Hz, 50 Hz Fadc, SF = 52H, chop off                                       |

| Analog Input Current <sup>2</sup>                 |                         |                 | ±1                        | nA                | T <sub>MAX</sub> = 85°C, buffer on                                                     |

|                                                   |                         |                 | ±5                        | nA                | T <sub>MAX</sub> = 125°C, buffer on                                                    |

| Analog Input Current Drift                        |                         | ±5              |                           | pA/°C             | T <sub>MAX</sub> = 85°C, buffer on                                                     |

|                                                   |                         | ±15             |                           | pA/°C             | T <sub>MAX</sub> = 125°C, buffer on                                                    |

| Average Input Current                             |                         | ±125            |                           | nA/V              | ±2.56 V range, buffer bypassed                                                         |

| Average Input Current Drift                       |                         | ±2              |                           | pA/V/°C           | Buffer bypassed                                                                        |

| Absolute AIN Voltage Limits <sup>2</sup>          | A <sub>GND</sub> + 0.1  |                 | AV <sub>DD</sub> –<br>0.1 | v                 | AIN1 AIN10 and AINCOM with buffer enabled                                              |

| Absolute AIN Voltage Limits <sup>2</sup>          | A <sub>GND</sub> – 0.03 |                 | AV <sub>DD</sub> + 0.03   | v                 | AIN1 AIN10 and AINCOM with buffer bypassed                                             |

| EXTERNAL REFERENCE INPUTS                         |                         |                 |                           |                   |                                                                                        |

| REFIN(+) to REFIN(–) Voltage                      |                         | 2.5             |                           | V                 | <b>REFIN refers to both REFIN and REFIN2</b>                                           |

| REFIN(+) to REFIN(-) Range <sup>2</sup>           | 1                       |                 | AVDD                      | V                 | <b>REFIN</b> refers to both REFIN and REFIN2                                           |

| Average Reference Input Current                   |                         | ±1              |                           | μA/V              | Both ADCs enabled                                                                      |

| Average Reference Input Current<br>Drift          |                         | ±0.1            |                           | nA/V/°C           |                                                                                        |

| NOXREF Trigger Voltage                            | 0.3                     |                 | 0.65                      | v                 | NOXREF (ADCSTAT.4) bit active if $V_{REF} > 0.3$ V, and inactive if $V_{REF} > 0.65$ V |

| Common-Mode Rejection                             |                         |                 |                           |                   |                                                                                        |

| DC Rejection                                      |                         | 125             |                           | dB                | $AIN = 1 V$ , range = $\pm 2.56 V$                                                     |

| 50 Hz/60 Hz Rejection <sup>2</sup>                | 90                      |                 |                           | dB                | 50 Hz/60 Hz ± 1 Hz, AIN = 1 V, range = ±2.56 V,<br>SF = 82                             |

| Normal Mode Rejection<br>50 Hz/60 Hz <sup>2</sup> | 75                      |                 |                           | dB                | 50 Hz/60 Hz $\pm$ 1 Hz, AIN = 1 V, range = $\pm$ 2.56 V, SF = 52H, chop on, REJ60 on   |

|                                                   | 100                     |                 |                           | dB                | 50 Hz $\pm$ 1 Hz, AlN = 1 V, range = $\pm$ 2.56 V,<br>SF = 52H, chop on                |

|                                                   | 67                      |                 |                           | dB                | 50 Hz/60 Hz ± 1 Hz, AIN = 1 V, range = ±2.56 V,<br>SF = 52H, chop off, REJ60 on        |

|                                                   | 100                     |                 |                           | dB                | 50 Hz $\pm$ 1 Hz, AlN = 1 V, range = $\pm$ 2.56 V, SF = 52H, chop off                  |

| AUXILIARY ADC (ADuC845 Only)                      |                         |                 |                           |                   |                                                                                        |

| Conversion Rate                                   | 5.4                     |                 | 105                       | Hz                | Chop on                                                                                |

|                                                   | 16.06                   |                 | 1365                      | Hz                | Chop off                                                                               |

| No Missing Codes <sup>2</sup>                     | 24                      |                 |                           | Bits              | ≤26.7 Hz update rate, chop enabled                                                     |

|                                                   | 24                      |                 |                           | Bits              | 80.3 Hz update rate, chop disabled                                                     |

| Resolution                                        | See Table               | 19 and Table 2  | 1                         |                   |                                                                                        |

| Output Noise                                      | See Table               | 18 and Table 20 | D                         |                   | Output noise varies with selected update rates.                                        |

| Integral Nonlinearity                             |                         |                 | ±15                       | ppm of FSR        | 1 LSB <sub>16</sub>                                                                    |

| Offset Error <sup>3</sup>                         |                         | ±3              |                           | μV                | Chop on                                                                                |

|                                                   |                         | ±0.25           |                           | LSB <sub>16</sub> | Chop off                                                                               |

| Offset Error Drift <sup>2</sup>                   |                         | 10              |                           | nV/°C             | Chop on                                                                                |

|                                                   |                         | 200             |                           | nV/°C             | Chop off                                                                               |

| Full-Scale Error <sup>4</sup>                     |                         | ±0.5            |                           | LSB <sub>16</sub> |                                                                                        |

| Gain Error Drift <sup>₄</sup>                     |                         | ±0.5            |                           | ppm/°C            |                                                                                        |

| Power Supply Rejection                            | 80                      |                 |                           | dB                | AIN = 1 V, range = $\pm 2.56$ V, chop enabled                                          |

|                                                   |                         | 80              |                           | dB                | AIN = 1 V, range = ±2.56 V, chop disabled                                              |

| Parameter                                                    | Min                                  | Тур                                   | Мах                | Unit            | Test Conditions/Comments                                     |

|--------------------------------------------------------------|--------------------------------------|---------------------------------------|--------------------|-----------------|--------------------------------------------------------------|

| AUXILIARY ADC ANALOG INPUTS                                  |                                      |                                       |                    |                 |                                                              |

| (ADuC845 ONLY)                                               |                                      |                                       |                    |                 |                                                              |

| Differential Input Voltage Ranges <sup>5,6</sup>             |                                      |                                       |                    |                 |                                                              |

| Bipolar Mode (ADC1CON.5 = 0)                                 |                                      | ±V <sub>REF</sub>                     |                    | V               | $REFIN = REFIN(+) - REFIN(-) \text{ (or Int 1.25 } V_{REF})$ |

| Unipolar Mode (ADC1CON.5 = 1)                                |                                      | $0 - V_{REF}$                         |                    | V               | $REFIN = REFIN(+) - REFIN(-)$ (or Int 1.25 $V_{REF}$ )       |

| Average Analog Input Current                                 |                                      | 125<br>±2                             |                    | nA/V<br>pA/V/°C |                                                              |

| Analog Input Current Drift<br>Absolute AIN/AINCOM Voltage    | Δ                                    | ±Ζ                                    | AV <sub>DD</sub> + | V V             |                                                              |

| Limits <sup>2,7</sup>                                        | A <sub>GND</sub> –<br>0.03           |                                       | 0.03               | v               |                                                              |

| Normal Mode Rejection 50 Hz/60 Hz <sup>2</sup>               |                                      |                                       |                    |                 |                                                              |

| On AIN and REFIN                                             | 75                                   |                                       |                    | dB              | 50 Hz/60 Hz ± 1 Hz, 16.6 Hz Fadc, SF = 52H, chop             |

|                                                              |                                      |                                       |                    |                 | on, REJ60 on                                                 |

|                                                              | 100                                  |                                       |                    | dB              | 50 Hz $\pm$ 1 Hz, 16.6 Hz Fadc, SF = 52H, chop on            |

|                                                              | 67                                   |                                       |                    | dB              | 50 Hz/60 Hz ± 1 Hz, 50 Hz Fadc, SF = 52H, chop               |

|                                                              |                                      |                                       |                    |                 | off, REJ60 on                                                |

|                                                              | 100                                  |                                       |                    | dB              | 50 Hz $\pm$ 1 Hz, 50 Hz Fadc, SF = 52H, chop off             |

| ADC SYSTEM CALIBRATION                                       |                                      |                                       |                    | V               |                                                              |

| Full-Scale Calibration Limit<br>Zero-Scale Calibration Limit |                                      |                                       | +1.05 × FS         | V               |                                                              |

|                                                              | $-1.05 \times FS$<br>$0.8 \times FS$ |                                       | 2.1 	imes FS       | V               |                                                              |

| Input Span<br>DAC                                            | 0.0 X F3                             |                                       | 2.1 × F3           | V               |                                                              |

| Voltage Range                                                |                                      | $0 - V_{\text{REF}}$                  |                    | v               | DACCON.2 = 0                                                 |

| voltage hange                                                |                                      | $0 - V_{REF}$<br>0 - AV <sub>DD</sub> |                    | v               | DACCON.2 = 0<br>DACCON.2 = 1                                 |

| Resistive Load                                               |                                      | 10                                    |                    | kΩ              | From DAC output to AGND                                      |

| Capactive Load                                               |                                      | 100                                   |                    | pF              | From DAC output to AGND                                      |

| Output Impedance                                             |                                      | 0.5                                   |                    | Ω               | ·····                                                        |

| I <sub>SINK</sub>                                            |                                      | 50                                    |                    | μA              |                                                              |

| DC Specifications <sup>8</sup>                               |                                      |                                       |                    |                 |                                                              |

| Resolution                                                   | 12                                   |                                       |                    | Bits            |                                                              |

| Relative Accuracy                                            |                                      | ±3                                    |                    | LSB             |                                                              |

| Differential Nonlinearity                                    |                                      |                                       | -1                 | LSB             | Guaranteed 12-bit monotonic                                  |

| Offset Error                                                 |                                      |                                       | ±50                | mV              |                                                              |

| Gain Error                                                   |                                      |                                       | ±1                 | %               | AV <sub>DD</sub> range                                       |

|                                                              |                                      | ±1                                    |                    | %               | V <sub>REF</sub> range                                       |

| AC Specifications <sup>2, 8</sup>                            |                                      |                                       |                    |                 |                                                              |

| Voltage Output Settling Time                                 |                                      | 15                                    |                    | μs              | Settling time to 1 LSB of final value                        |

| Digital-to-Analog Glitch Energy                              |                                      | 10                                    |                    | nVs             | 1 LSB change at major carry                                  |

| INTERNAL REFERENCE                                           |                                      |                                       |                    |                 |                                                              |

| ADC Reference                                                | 1 35 10/                             | 1 25                                  | 1 75 . 10/         | V               | Chop enabled                                                 |

| Reference Voltage                                            | 1.25 – 1%                            | 1.25                                  | 1.25 + 1%          | V               | Initial tolerance @ $25^{\circ}$ C, V <sub>DD</sub> = 5 V    |

| Power Supply Rejection<br>Reference Tempco                   |                                      | 45<br>100                             |                    | dB              |                                                              |

| DAC Reference                                                |                                      | 100                                   |                    | ppm/°C          |                                                              |

| Reference Voltage                                            | 2.5 – 1%                             | 2.5                                   | 2.5 + 1%           | ±1% V           | Initial tolerance @ 25°C, $V_{DD} = 5 V$                     |

| Power Supply Rejection                                       | 2.2 1/0                              | 2.5<br>50                             | 0/ I ⊤ <b>נ</b> יב | dB              |                                                              |

| Reference Tempco                                             |                                      | ±100                                  |                    | ppm/°C          |                                                              |

| TEMPERATURE SENSOR                                           |                                      |                                       |                    |                 |                                                              |

| (ADuC845 ONLY)                                               |                                      |                                       |                    |                 |                                                              |

| Accuracy                                                     |                                      | ±2                                    |                    | °C              |                                                              |

| Thermal Impedance                                            |                                      | 90                                    |                    | °C/W            | MQFP                                                         |

|                                                              |                                      | 52                                    |                    | °C/W            | LFCSP                                                        |

| Parameter                                                  | Min  | Тур  | Мах             | Unit   | Test Conditions/Comments                                                   |

|------------------------------------------------------------|------|------|-----------------|--------|----------------------------------------------------------------------------|

| TRANSDUCER BURNOUT CURRENT<br>SOURCES                      |      |      |                 |        |                                                                            |

| AIN+ Current                                               |      | -100 |                 | nA     | AIN+ is the selected positive input (AIN4 or AIN6 only) to the primary ADC |

| AIN– Current                                               |      | 100  |                 | nA     | AIN– is the selected negative input (AIN5 or AIN7 only) to the primary ADC |

| Initial Tolerance at 25°C                                  |      | ±10  |                 | %      |                                                                            |

| Drift                                                      |      | 0.03 |                 | %/°C   |                                                                            |

| EXCITATION CURRENT SOURCES                                 |      |      |                 |        |                                                                            |

| Output Current                                             |      | 200  |                 | μA     | Available from each current source                                         |

| Initial Tolerance at 25°C                                  |      | ±10  |                 | %      |                                                                            |

| Drift                                                      |      | 200  |                 | ppm/°C |                                                                            |

| Initial Current Matching at 25°C                           |      | ±1   |                 | %      | Matching between both current sources                                      |

| Drift Matching                                             |      | 20   |                 | ppm/°C |                                                                            |

| Line Regulation (AV <sub>DD</sub> )                        |      | 1    |                 | μA/V   | $AV_{DD} = 5 V \pm 5\%$                                                    |

| Load Regulation                                            |      | 0.1  |                 | μA/V   |                                                                            |

| Output Compliance <sup>2</sup>                             | AGND |      | $AV_{DD} - 0.6$ | V      |                                                                            |

| POWER SUPPLY MONITOR (PSM)                                 |      |      |                 |        |                                                                            |

| AV <sub>DD</sub> Trip Point Selection Range                | 2.63 |      | 4.63            | V      | Four trip points selectable in this range                                  |

| AV <sub>DD</sub> Trip Point Accuracy                       |      |      | ±3.0            | %      | $T_{MAX} = 85^{\circ}C$                                                    |

|                                                            |      |      | ±4.0            | %      | T <sub>MAX</sub> = 125°C                                                   |

| DV <sub>DD</sub> Trip Point Selection Range                | 2.63 |      | 4.63            | V      | Four trip points selectable in this range                                  |

| DV <sub>DD</sub> Trip Point Accuracy                       |      |      | ±3.0            | %      | $T_{MAX} = 85^{\circ}C$                                                    |

|                                                            |      |      | ±4.0            | %      | T <sub>MAX</sub> = 125°C                                                   |

| CRYSTAL OSCILLATOR (XTAL1 AND                              |      |      |                 |        |                                                                            |

| XTAL2)                                                     |      |      |                 |        |                                                                            |

| Logic Inputs, XTAL1 Only <sup>2</sup>                      |      |      |                 |        |                                                                            |

| V <sub>INL</sub> , Input Low Voltage                       |      |      | 0.8             | V      | $DV_{DD} = 5 V$                                                            |

|                                                            |      |      | 0.4             | V      | $DV_{DD} = 3 V$                                                            |

| V <sub>INH</sub> , Input Low Voltage                       | 3.5  |      |                 | V      | $DV_{DD} = 5 V$                                                            |

|                                                            | 2.5  |      |                 | V      | $DV_{DD} = 3 V$                                                            |

| XTAL1 Input Capacitance                                    |      | 18   |                 | pF     |                                                                            |

| XTAL2 Output Capacitance                                   |      | 18   |                 | pF     |                                                                            |

| LOGIC INPUTS                                               |      |      |                 |        |                                                                            |

| All Inputs Except SCLOCK, RESET,<br>and XTAL1 <sup>2</sup> |      |      |                 |        |                                                                            |

| V <sub>INL</sub> , Input Low Voltage                       |      |      | 0.8             | V      | $DV_{DD} = 5 V$                                                            |

|                                                            |      |      | 0.4             | V      | $DV_{DD} = 3 V$                                                            |

| V <sub>INH</sub> , Input Low Voltage                       | 2.0  |      |                 | V      |                                                                            |

| SCLOCK and RESET Only                                      |      |      |                 |        |                                                                            |

| (Schmidt Triggered Inputs) <sup>2</sup>                    | 1.2  |      | 2.0             |        |                                                                            |

| V <sub>T+</sub>                                            | 1.3  |      | 3.0             | V      | $DV_{DD} = 5 V$                                                            |

|                                                            | 0.95 |      | 2.5             | V      | $DV_{DD} = 3V$                                                             |

| V <sub>T-</sub>                                            | 0.8  |      | 1.4             | V      | $DV_{DD} = 5 V$                                                            |

|                                                            | 0.4  |      | 1.1             | V      | $DV_{DD} = 3 V$                                                            |

| $V_{T+} - V_{T-}$                                          | 0.3  |      | 0.85            | V      | $DV_{DD} = 5 V \text{ or } 3 V$                                            |

| Input Currents                                             |      |      | . 10            |        |                                                                            |

| Port 0, P1.0 to P1.7, EA                                   |      |      | ±10             | μA     | $V_{IN} = 0 V \text{ or } V_{DD}$                                          |

| RESET                                                      |      |      | ±10             | μA     | $V_{\rm IN} = 0 \text{ V},  \text{DV}_{\rm DD} = 5 \text{ V}$              |

|                                                            | 35   |      | 105             | μA     | $V_{IN} = DV_{DD}, DV_{DD} = 5 V$ , internal pull-down                     |

| Port 2, Port 3                                             |      |      | ±10             | μA     | $V_{IN} = DV_{DD}, DV_{DD} = 5 V$                                          |

|                                                            | -180 |      | -660            | μA     | $V_{IN} = 2 V, DV_{DD} = 5 V$                                              |

|                                                            | -20  |      | -75             | μA     | $V_{IN} = 0.45 V, DV_{DD} = 5 V$                                           |

| Input Capacitance                                          |      | 10   |                 | pF     | All digital inputs                                                         |

| Parameter                                                                          | Min     | Тур | Max  | Unit   | Test Conditions/Comments                                                                          |

|------------------------------------------------------------------------------------|---------|-----|------|--------|---------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (ALL DIGITAL<br>OUTPUTS EXCEPT XTAL2)                                |         |     |      |        |                                                                                                   |

| V <sub>он</sub> , Output High Voltage <sup>2</sup>                                 | 2.4     |     |      | v      | $DV_{DD} = 5 V$ , $I_{SOURCE} = 80 \mu A$                                                         |

|                                                                                    | 2.4     |     |      | v      | $DV_{DD} = 3 V$ , Isource = 20 $\mu$ A                                                            |

| Vo∟, Output Low Voltage                                                            |         |     | 0.4  | v      | I <sub>SINK</sub> = 8 mA, SCLOCK, SDATA                                                           |

|                                                                                    |         |     | 0.4  | v      | $I_{SINK} = 1.6 \text{ mA on P0, P1, P2}$                                                         |

| Floating State Leakage Current <sup>2</sup>                                        |         |     | ±10  | μA     |                                                                                                   |

| Floating State Output Capacitance                                                  |         | 10  | 10   | pF     |                                                                                                   |

| START-UP TIME                                                                      |         | 10  |      |        |                                                                                                   |

| At Power-On                                                                        |         | 600 |      | ms     |                                                                                                   |

| After Ext RESET in Normal Mode                                                     |         | 3   |      | ms     |                                                                                                   |

| After WDT RESET in Normal Mode                                                     |         | 2   |      | ms     | Controlled via WDCON SFR                                                                          |

| From Power-Down Mode                                                               |         | 2   |      | 1115   |                                                                                                   |

| Oscillator Running                                                                 |         |     |      |        | PLLCON.7 = 0                                                                                      |

| Wake-Up with INTO Interrupt                                                        |         | 20  |      |        |                                                                                                   |

| Wake-Up with SPI Interrupt                                                         |         | 20  |      | μs     |                                                                                                   |

| Wake-Up with TIC Interrupt                                                         |         |     |      | μs     |                                                                                                   |

| Oscillator Powered Down                                                            |         | 20  |      | μs     |                                                                                                   |

|                                                                                    |         | 20  |      |        | PLLCON.7 = 1                                                                                      |

| Wake-Up with INTO Interrupt                                                        |         | 30  |      | μs     |                                                                                                   |

| Wake-Up with SPI Interrupt                                                         |         | 30  |      | μs     |                                                                                                   |

| FLASH/EE MEMORY RELIABILITY<br>CHARACTERISTICS                                     |         |     |      |        |                                                                                                   |

| Endurance <sup>9</sup>                                                             | 100,000 |     |      | Cycles |                                                                                                   |

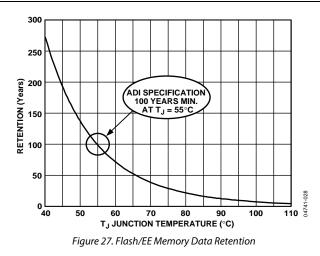

| Data Retention <sup>10</sup>                                                       | 100     |     |      | Years  |                                                                                                   |

| POWER REQUIREMENTS                                                                 |         |     |      |        |                                                                                                   |

| Power Supply Voltages                                                              |         |     |      |        |                                                                                                   |

| AV <sub>DD</sub> 3 V Nominal                                                       | 2.7     |     | 3.6  | V      |                                                                                                   |

| AV <sub>DD</sub> 5 V Nominal                                                       | 4.75    |     | 5.25 | V      |                                                                                                   |

| DV <sub>DD</sub> 3 V Nominal                                                       | 2.7     |     | 3.6  | V      |                                                                                                   |

| DV <sub>DD</sub> 5 V Nominal                                                       | 4.75    |     | 5.25 | V      |                                                                                                   |

| 5 V Power Consumption                                                              |         |     |      |        | $4.75 \text{ V} < \text{DV}_{\text{DD}} < 5.25 \text{ V}, \text{AV}_{\text{DD}} = 5.25 \text{ V}$ |

| Normal Mode <sup>11, 12</sup>                                                      |         |     |      |        |                                                                                                   |

| DV <sub>DD</sub> Current                                                           |         |     | 10   | mA     | Core clock = 1.57 MHz                                                                             |

|                                                                                    |         | 25  | 31   | mA     | Core clock = 12.58 MHz                                                                            |

| AV <sub>DD</sub> Current                                                           |         |     | 180  | μΑ     |                                                                                                   |

| Power-Down Mode <sup>11, 12</sup>                                                  |         |     |      |        |                                                                                                   |

| DV <sub>DD</sub> Current                                                           |         | 40  | 53   | μΑ     | $T_{MAX} = 85^{\circ}C$ ; OSC on; TIC on                                                          |

|                                                                                    |         | 50  |      | μΑ     | T <sub>MAX</sub> = 125°C; OSC on; TIC on                                                          |

|                                                                                    |         | 20  | 33   | μΑ     | $T_{MAX} = 85^{\circ}C; OSC off$                                                                  |

|                                                                                    |         | 30  |      | μΑ     | $T_{MAX} = 125^{\circ}C$ ; OSC off                                                                |

| AV <sub>DD</sub> Current                                                           |         |     | 1    | μΑ     | $T_{MAX} = 85^{\circ}C$ ; OSC on or off                                                           |

|                                                                                    |         |     | 3    | μΑ     | $T_{MAX} = 125^{\circ}C$ ; OSC on or off                                                          |

| Typical Additional Peripheral<br>Currents (Al <sub>DD</sub> and DI <sub>DD</sub> ) |         |     |      |        | 5 V V <sub>DD</sub> , CD = 3                                                                      |

| Primary ADC                                                                        |         | 1   |      | mA     |                                                                                                   |

| Auxiliary ADC (ADuC845 Only)                                                       |         | 0.5 |      | mA     |                                                                                                   |

| Power Supply Monitor                                                               |         | 30  |      | μA     |                                                                                                   |

| DAC                                                                                |         | 60  |      | μA     | DACH/L = 000H                                                                                     |

| Dual Excitation Current Sources                                                    |         | 200 |      | μA     | 200 $\mu$ A each. Can be combined to give 400 $\mu$ A on a single output.                         |

| ALE Off                                                                            |         | -20 |      | μA     | PCON.4 = 1 (see Table 6)                                                                          |

| WDT                                                                                |         | 10  |      | μA     |                                                                                                   |

### ADuC845

| Parameter                         | Min | Тур | Max | Unit | Test Conditions/Comments                                                                       |

|-----------------------------------|-----|-----|-----|------|------------------------------------------------------------------------------------------------|

| PWM                               |     |     |     |      |                                                                                                |

| –Fxtal                            |     | 3   |     | μΑ   |                                                                                                |

| –Fvco                             |     | 0.5 |     | mA   |                                                                                                |

| TIC                               |     | 1   |     | μΑ   |                                                                                                |

| 3 V Power Consumption             |     |     |     |      | $2.7 \text{ V} < \text{DV}_{\text{DD}} < 3.6 \text{ V}, \text{AV}_{\text{DD}} = 3.6 \text{ V}$ |

| Normal Mode <sup>11, 12</sup>     |     |     |     |      |                                                                                                |

| DV <sub>DD</sub> Current          |     |     | 4.8 | mA   | Core clock = 1.57 MHz                                                                          |

|                                   |     | 9   | 11  | mA   | Core clock = 6.29 MHz (CD = 1)                                                                 |

| AV <sub>DD</sub> Current          |     |     | 180 | μΑ   | ADC not enabled                                                                                |

| Power-Down Mode <sup>11, 12</sup> |     |     |     |      |                                                                                                |

| DV <sub>DD</sub> Current          |     | 20  | 26  | μΑ   | $T_{MAX} = 85^{\circ}C$ ; OSC on; TIC on                                                       |

|                                   |     | 29  |     | μΑ   | $T_{MAX} = 125^{\circ}C$ ; OSC on; TIC on                                                      |

|                                   |     | 14  | 20  | μΑ   | $T_{MAX} = 85^{\circ}C; OSC off$                                                               |

|                                   |     | 21  |     | μΑ   | $T_{MAX} = 125^{\circ}C$ ; OSC off                                                             |

| AV <sub>DD</sub> Current          |     |     | 1   | μΑ   | T <sub>MAX</sub> = 85°C; OSC on or off                                                         |

|                                   |     |     | 3   | μΑ   | $T_{MAX} = 125^{\circ}C$ ; OSC on or off                                                       |

<sup>1</sup> Temperature range is for ADuC845BS; for the ADuC847BS and ADuC848BS (MQFP package), the range is –40°C to +125°C. Temperature range for ADuC845BCP, ADuC847BCP, and ADuC848BCP (LFCSP package) is –40°C to +85°C.

<sup>2</sup> These numbers are not production tested but are guaranteed by design and/or characterization data on production release.

<sup>3</sup> System zero-scale calibration can remove this error.

<sup>4</sup> Gain error drift is a span drift. To calculate full-scale error drift, add the offset error drift to the gain error drift times the full-scale input.

<sup>5</sup> In general terms, the bipolar input voltage range to the primary ADC is given by the ADC range =  $\pm (V_{REF} 2^{RN})/1.25$ , where:

$V_{REF} = REFIN(+)$  to REFIN(-) voltage and  $V_{REF} = 1.25$  V when internal ADC  $V_{REF}$  is selected. RN = decimal equivalent of RN2, RN1, RN0. For example, if  $V_{REF} = 2.5$  V and RN2, RN1, RN0 = 1, 1, 0, respectively, then the ADC range = ±1.28 V. In unipolar mode, the effective range is 0 V to 1.28 V in this example.

<sup>6</sup> 1.25 V is used as the reference voltage to the ADC when internal V<sub>REF</sub> is selected via XREF0/XREF1 or AXREF bits in ADC0CON2 and ADC1CON, respectively. (AXREF is available only on the ADuC845.)

<sup>7</sup> In bipolar mode, the auxiliary ADC can be driven only to a minimum of AGND – 30 mV as indicated by the auxiliary ADC absolute AIN voltage limits. The bipolar range is still – V<sub>REF</sub> to +V<sub>REF</sub>.

$^{8}$  DAC linearity and ac specifications are calculated using a reduced code range of 48 to 4095, 0 V to V<sub>REF</sub>, reduced code range of 100 to 3950, 0 V to V<sub>DD</sub>.

<sup>9</sup> Endurance is qualified to 100 kcycle per JEDEC Std. 22 method A117 and measured at -40°C, +25°C, +85°C, and +125°C. Typical endurance at 25°C is 700 kcycles.

<sup>10</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature.

<sup>11</sup> Power supply current consumption is measured in normal mode following the power-on sequence, and in power-down modes under the following conditions: Normal mode: reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, core executing internal software loop. Power-down mode: reset = 0.4 V, all P0 pins and P1.2 to P1.7 pins = 0.4 V. All other digital I/O pins are open circuit, core Clk changed via CD bits in PLLCON, PCON.1 = 1, core

execution suspended in power-down mode, OSC turned on or off via OSC\_PD bit (PLLCON.7) in PLLCON SFR.

<sup>12</sup> DV<sub>DD</sub> power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

#### **General Notes about Specifications**

- DAC gain error is a measure of the span error of the DAC.

- The ADuC845BCP, ADuC847BCP, and ADuC848BCP (LFCSP package) have been qualified and tested with the base of the LFCSP package floating. The base of the LFCSP package should be soldered to the board, but left floating electrically, to ensure good mechanical stability.

- Flash/EE memory reliability characteristics apply to both the Flash/EE program memory and Flash/EE data memory.

### **ABOSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 2.

| Parameter                                 | Rating                             |

|-------------------------------------------|------------------------------------|

| AV <sub>DD</sub> to AGND                  | –0.3 V to +7 V                     |

| AV <sub>DD</sub> to DGND                  | –0.3 V to +7 V                     |

| DV <sub>DD</sub> to DGND                  | –0.3 V to +7 V                     |

| DV <sub>DD</sub> to DGND                  | –0.3 V to +7 V                     |

| AGND to DGND <sup>1</sup>                 | –0.3 V to +0.3 V                   |

| AV <sub>DD</sub> to DV <sub>DD</sub>      | –2 V to +5 V                       |

| Analog Input Voltage to AGND <sup>2</sup> | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| Reference Input Voltage to AGND           | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| AIN/REFIN Current (Indefinite)            | 30 mA                              |

| Digital Input Voltage to DGND             | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Digital Output Voltage to DGND            | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Operating Temperature Range               | –40°C to +125°C                    |

| Storage Temperature Range                 | –65°C to +150°C                    |

| Junction Temperature                      | 150°C                              |

| $\theta_{JA}$ Thermal Impedance (MQFP)    | 90°C/W                             |

| $\theta_{JA}$ Thermal Impedance (LFCSP)   | 52°C/W                             |

| Lead Temperature, Soldering               |                                    |

| Vapor Phase (60 sec)                      | 215°C                              |

| Infrared (15 sec)                         | 220°C                              |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>1</sup> AGND and DGND are shorted internally on the ADuC845, ADuC847, and ADuC848.

<sup>2</sup> Applies to the P1.0 to P1.7 pins operating in analog or digital input modes.

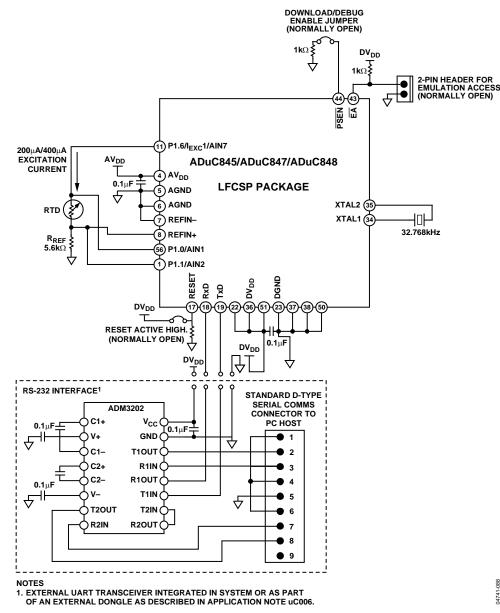

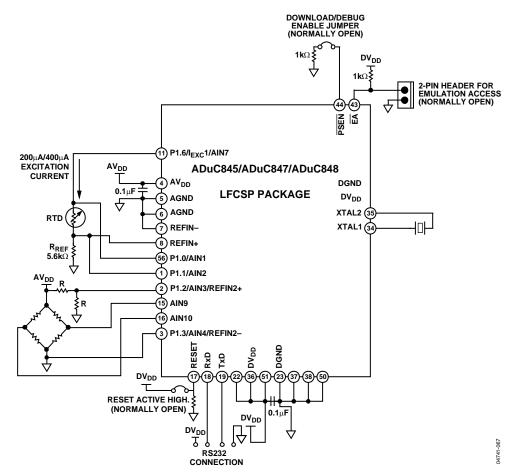

#### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS** P0.7/AD7 P0.6/AD6 P0.5/AD5 P0.4/AD4 P0.4/AD4 DVbD DGND P0.3/AD3 P0.2/AD2 P0.1/AD1 P0.0/AD0 ALE ALE ALE P0.7/AD7 P0.5/AD5 P0.4/AD4 DV bD DG ND P0.3/AD3 P0.3/AD1 P0.1/AD1 P0.0/AD0 P1.0/AIN1 P0.6/AD6 ALE PSEN EA 52 51 50 49 48 47 46 45 44 43 42 41 40 55 54 53 52 51 50 49 48 47 46 45 43 56 44 P2.7/PWMCLK P1.0/AIN1 1 P2.7/PWMCLK PIN 1 IDENTIFIER P1.1/AIN2 42 P2.7/PWMCI P2.6/PWM1 P2.5/PWM0 P2.4/T2EX DGND DGND DVDD P1.1/AIN2 2 P2.6/PWM1 P1.2/AIN3/REFIN2+ 41 2 P2.5/PWM0 P1.2/AIN3/REFIN2+ P1.3/AIN4/REFIN2-3 37 3 40 P2.4/T2EX AV<sub>DD</sub> AGND P1.3/AIN4/REFIN2-4 39 DGND $AV_{DD}$ 5 5 38 ADuC845/ADuC847/ADuC848 ADuC845/ADuC847/ AGND AGND $\mathrm{DV}_{\mathrm{DD}}$ 6 37 6 ADuC848 REFIN-REFIN-7 XTAL2 7 36 33 DVDD XTAL2 XTAL1 P2.3/55/T2 P2.2/MISO P2.1/MOSI P2.0/SCLOCK (SPI) SDATA TOP VIEW (Not to Scale) REFIN+ REFIN+ 8 TOP VIEW (Not to Scale) 35 8 XTAL1 P1.4/AIN5 34 9 P1.4/AIN5 9 P2.3/SS/T2 P1.5/AIN6 P1.6/AIN7/IEXC1 P1.7/AIN8/IEXC2 AINCOM/DAC DAC 33 10 P1.5/AIN6 P2.2/MISO 10 11 32 P2.1/MOSI P1.6/AIN7/IEXC1 11 12 31 28 P2.0/SCLOCK (SPI) P1.7/AIN8/IEXC2 12 13 30 AINCOM/DAC 13 27 SDATA DAC 29 œ 19 20 22 23 25 25 25 25 25 27 8 14 15 16 17 18 19 20 21 22 23 24 25 26 DAC B RESET 1 RESET 1 P3.0/RXD 2 P3.0/RXD 2 P3.1/TXD 2 P3.3/INT1 2 P3.4/T0 2 P3.5/RT 2 P3.1/TxD P3.2/INT0 P3.2/INT0 P3.3/INT1 P3.4/T0 P3.6/WR P3.7/RD 0/RxD AIN9 **AIN10** RESET SCLK (12C) 04741-002 ñ NOTES 1. THE EXPOSED PADDLE MUST BE LEFT UNCONNECTED. Figure 2. 52-Lead MQFP Pin Configuration Figure 3. 56-Lead LFCSP Pin Configuration

#### **Table 3. Pin Function Descriptions**

| Pin               | No.      |                   |                   |                                                                                                                                                                                                                                                                                      |

|-------------------|----------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP           | 56-LFCSP | Mnemonic          | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                          |

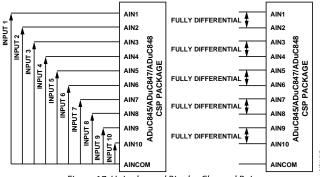

| 1                 | 56       | P1.0/AIN1         | I                 | By power-on default, P1.0/AIN1 is configured as the AIN1 analog input.                                                                                                                                                                                                               |

|                   |          |                   |                   | AIN1 can be used as a pseudo differential input when used with AINCOM or as the positive input of a fully differential pair when used with AIN2.                                                                                                                                     |

|                   |          |                   |                   | P1.0 has no digital output driver. It can function as a digital input for which 0 must be written to the port bit. As a digital input, this pin must be driven high or low externally.                                                                                               |

| 2                 | 1        | P1.1/AIN2         | 1                 | On power-on default, P1.1/AIN2 is configured as the AIN2 analog input.                                                                                                                                                                                                               |

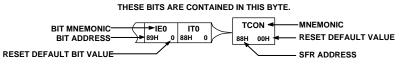

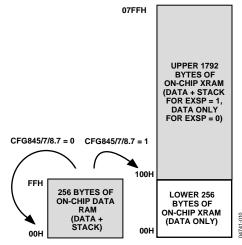

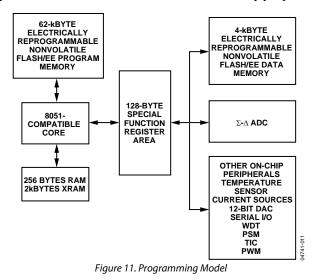

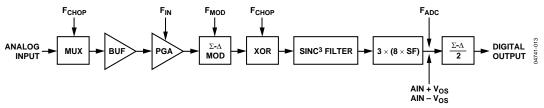

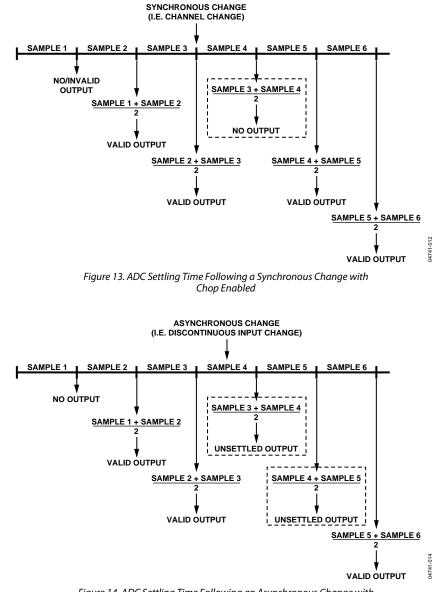

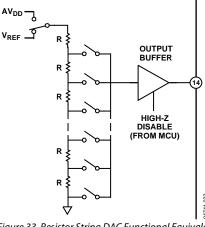

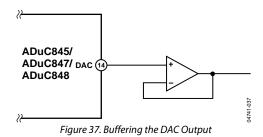

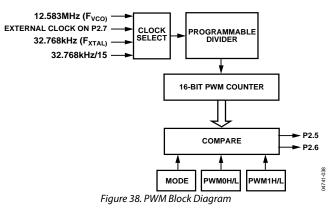

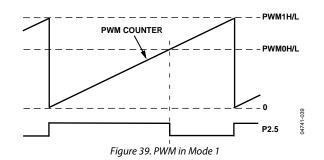

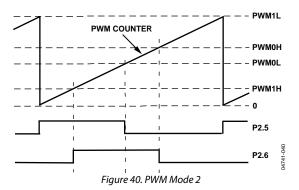

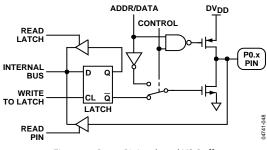

|                   |          |                   |                   | AIN2 can be used as a pseudo differential input when used with AINCOM or as the negative input of a fully differential pair when used with AIN1.                                                                                                                                     |