## 16-Channel Multicell Battery Monitor

#### **FEATURES**

- ▶ Measures up to 16 battery cells in series

- Maximum lifetime TME: ±1.8 mV at 3.3 V per cell (−40°C to +125°C)

- ▶ Simultaneous and continuous measurement of cell voltages

- Configurable integrated low-pass filtering

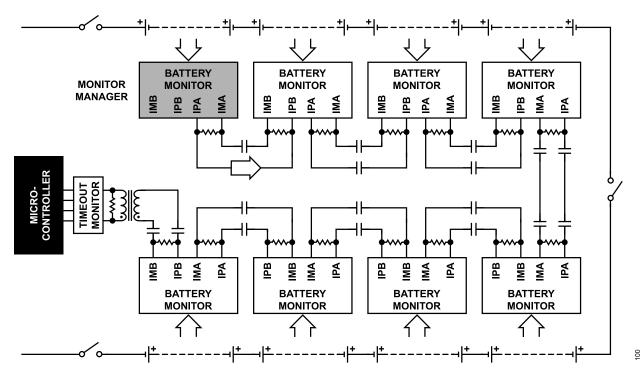

- ▶ Stackable architecture for high voltage battery packs

- ▶ Built-in isoSPI interface

- ▶ 2 Mbps isolated serial communications

- ▶ Uses a single twisted pair, up to 20 meters per segment

- Low EMI susceptibility and emissions

- ▶ Bidirectional for broken wire protection

- Capacitor or transformer-coupled

- ▶ Hot plug tolerant without external protection

- Passive cell balancing up to 300 mA per channel with programmable PWM

- ▶ Up to 10 general-purpose analog inputs or digital I/O

- Temperature or other sensor inputs

- Configurable as an I<sup>2</sup>C or SPI master

- ▶ LPCM for cell and temperature monitoring in key-off state

- ▶ 4 µA sleep mode supply current

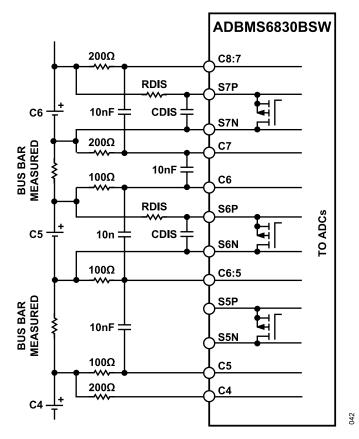

- Provisions for bus bars

### **APPLICATIONS**

- Backup battery systems

- Grid energy storage

- Battery cell and pack management

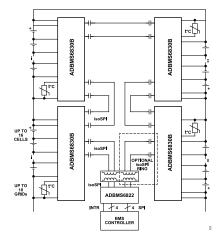

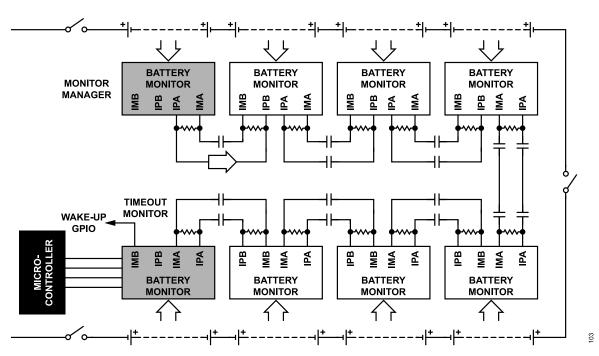

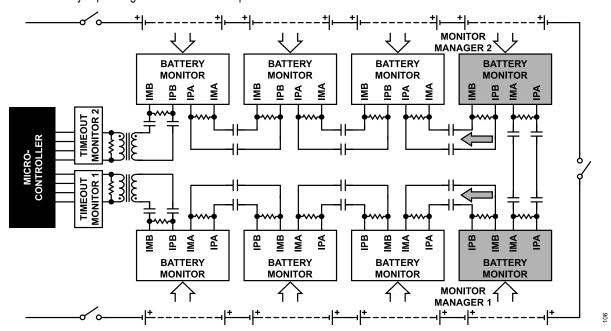

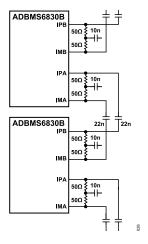

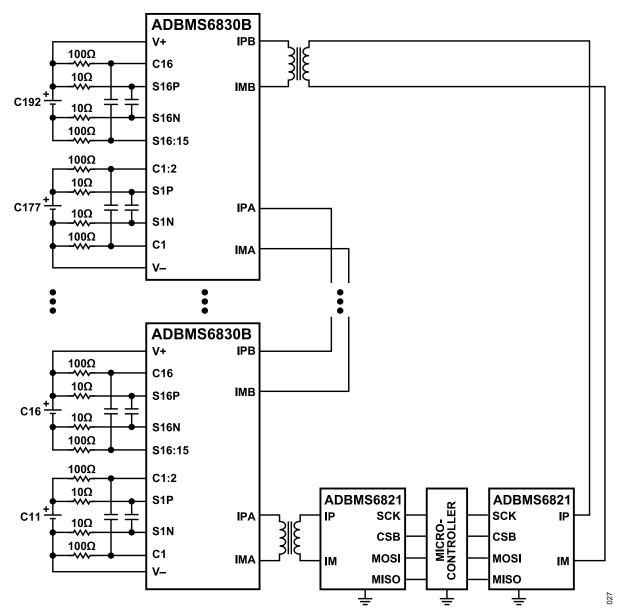

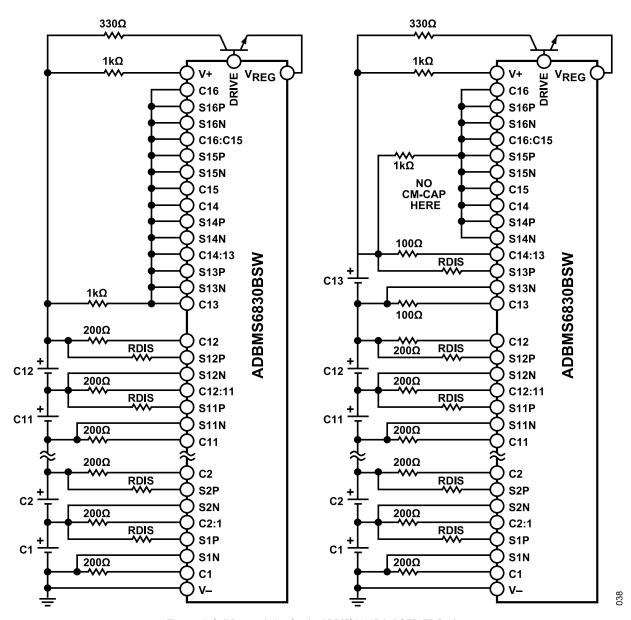

#### TYPICAL APPLICATION CIRCUIT

Figure 1. Typical Application Circuit

#### **GENERAL DESCRIPTION**

The ADBMS6830B is a multicell battery stack monitor that measures up to 16 series-connected battery cells with a lifetime total measurement error (TME) of less than 2 mV over the full temperature range. The measurement input range of −2 V to +5.5 V makes the ADBMS6830B suitable for most battery chemistries and allows the measurement of voltages across bus bars. Provisions are made for bypassing bus bars without dedicating any measurement channels.

All cells can be measured simultaneously and redundantly with two individual analog-to-digital converters (ADCs). The continuously operating ADCs with a high sampling rate of 4.096 MHz allow reduced external analog filtering and aliasing-free measurement results. Higher noise reduction can be achieved by subsequent programmable infinite impulse response (IIR) filters.

Multiple ADBMS6830Bs can be connected in series, permitting simultaneous cell monitoring of long, high voltage battery strings. Each ADBMS6830B has an isolated serial port interface (isoSPI™) for high speed, RF immune, long distance communications. Multiple devices are connected in a daisy chain with one host processor connection. This daisy chain can be operated bidirectionally, ensuring communication integrity even in the event of a fault along the communication path.

The ADBMS6830B can be powered from the battery stack or an isolated supply. The ADBMS6830B includes passive balancing with individual pulse-width modulation (PWM) duty cycle control and up to 300 mA discharge current for each cell. Other features include an on-board 5 V regulator, up to 10 GPIOs, and a sleep mode, where current consumption is reduced to 4  $\mu A$ .

www.datasheetall.com

**Data Sheet**

## **TABLE OF CONTENTS**

| eatures 1                                      | Clear Overvoltage and Undervoltage                        |    |

|------------------------------------------------|-----------------------------------------------------------|----|

| Applications1                                  | Command                                                   | 28 |

| Typical Application Circuit1                   | Cell Discharge and PWM for Discharge                      | 29 |

| General Description1                           | Sx Pin Muting                                             | 29 |

| Functional Block Diagram4                      | Cell Discharge with Cell Measurements and                 |    |

| Specifications5                                | Diagnostics                                               | 30 |

| isoSPI Pulse Timing Specifications8            | Watchdog and Discharge Timer                              |    |

| SPI Timing Requirements9                       | Discharge Timer Monitor                                   |    |

| isoSPI Timing Specifications9                  | Low Power Cell Monitoring                                 |    |

| Absolute Maximum Ratings10                     | LPCM Operation                                            |    |

| Thermal Resistance10                           | LPCM Bridgeless Timeout Monitor                           |    |

| Electrostatic Discharge (ESD) Ratings10        | LPCM with Reversible isoSPI                               |    |

| ESD Caution10                                  | Using the LPCM and the Discharge Timer                    | 39 |

| Pin Configurations and Function Descriptions11 | LPCM Expanded State Diagram                               |    |

| Typical Performance Characteristics13          | LPCM Power Consumption                                    |    |

| Γheory of Operation15                          | LPCM System Diagnostics                                   |    |

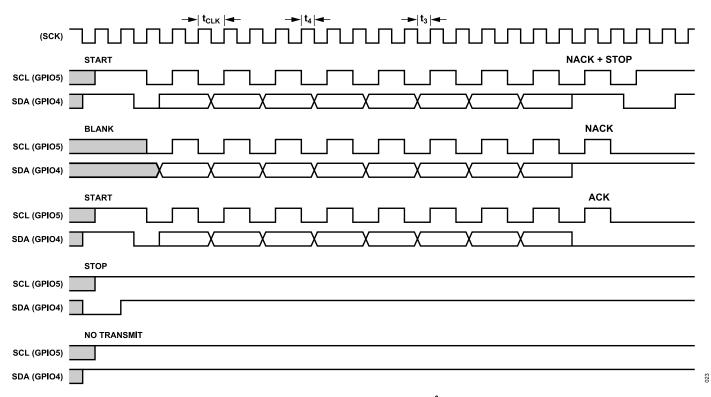

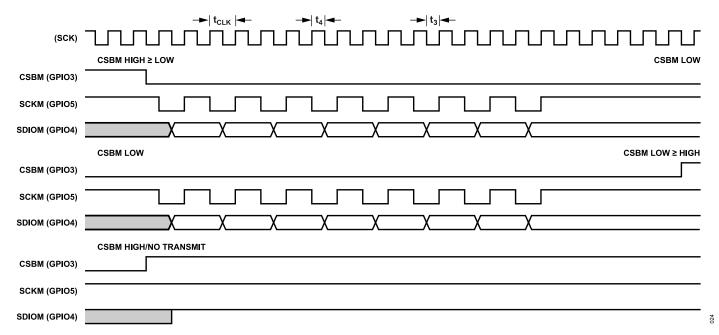

| Core State Descriptions                        | I <sup>2</sup> C/SPI Master Using GPIOs                   |    |

| isoSPI State Description17                     | COMM Register                                             |    |

| Power Supply18                                 | COMM Commands                                             |    |

| Cell Voltage Measurements19                    | Timing Specifications of I <sup>2</sup> C and SPI Master. |    |

| C-ADC and S-ADC Operations and                 | Serial Interface Overview                                 |    |

| Commands19                                     | 4-Wire SPI Physical Layer                                 |    |

| Continuous or Single Shot Measurements20       | Reversible 2-Wire isoSPI Physical Layer                   |    |

| Redundant Measurements20                       | Network Layer                                             |    |

| Discharge During Measurements20                | Command PEC                                               |    |

| Open Wire Switches21                           | Data PEC                                                  |    |

| Internal Digital Filtering21                   | Command Counter                                           |    |

| GPIO and Device Parameter Measurements 23      | Polling Methods                                           |    |

| AUX ADC Operation and Commands23               | Bus Protocols                                             |    |

| System Diagnostic24                            | Commands                                                  |    |

| Cell Measurement Diagnostic and Reporting24    | Read All and Snapshot Commands                            |    |

| Cell Open Wire Detection24                     | Read All Commands                                         |    |

| Algorithm for Cell Measurement with            | Snapshot Commands                                         |    |

| Diagnostics25                                  | Retention Register Commands                               |    |

| GPIO Measurement Diagnostic26                  | Memory Map                                                |    |

| GPIO Open Wire Detection26                     | Applications Information                                  |    |

| Communication Diagnostic and Reporting26       | Providing Power by Linear Regulator                       |    |

| Thermal Shutdown26                             | Input Filtering                                           |    |

| Test Mode Detection26                          | Cell Balancing                                            |    |

| Sleep State Detection26                        | Cell Depopulation                                         |    |

| Soft Reset Command                             | Bus Bar Monitoring and Bypassing                          |    |

| Revision Code                                  | Internal Protection                                       |    |

| Serial ID                                      | Outline Dimensions                                        |    |

| Clear ADC Memory Commands26                    | Ordering Guide                                            |    |

| Clear Flag Command27                           | Evaluation Boards                                         |    |

| 2.2                                            |                                                           | 55 |

analog.com Rev. 0 | 2 of 83

## **REVISION HISTORY**

1/2024—Revision 0: Initial Version

analog.com Rev. 0 | 3 of 83

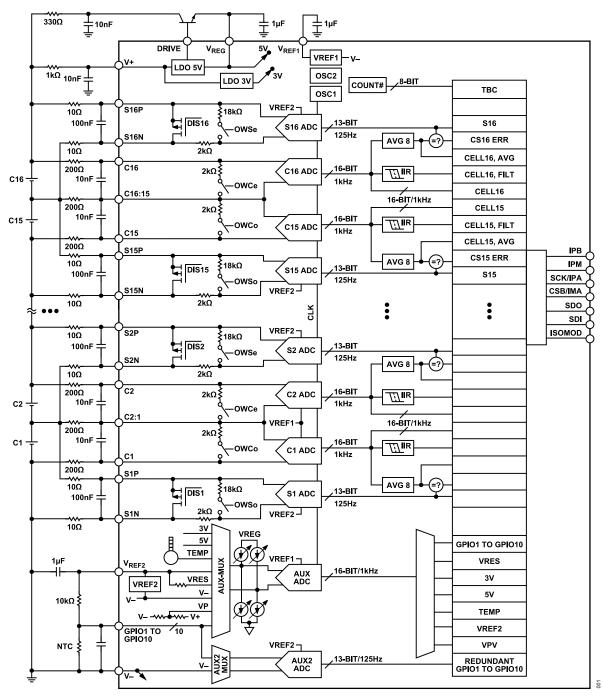

#### **FUNCTIONAL BLOCK DIAGRAM**

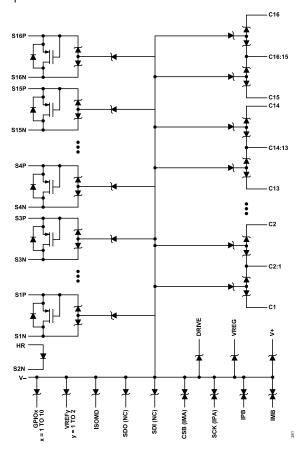

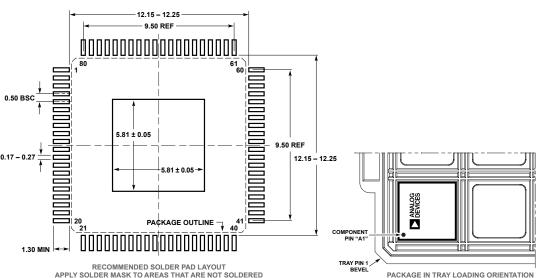

Figure 2. ADBMS6830B in 80-Lead LQFP\_EP Package

analog.com Rev. 0 | 4 of 83

## **SPECIFICATIONS**

Specifications apply over the full V+ operating voltage range and full operating junction temperature range ( $T_J = -40$ °C to +125°C), unless otherwise noted.

Table 1. C-ADC DC Specifications

| Parameter                                                   | Symbol              | Test Conditions/Comments   | Min | Тур   | Max  | Unit   |

|-------------------------------------------------------------|---------------------|----------------------------|-----|-------|------|--------|

| MEASUREMENT RESOLUTION                                      |                     |                            |     | 0.15  |      | mV/bit |

| DIFFERENTIAL INPUT RANGE                                    | V <sub>DIF</sub>    | -0.1 V < (Cx to V-) < 80 V | -2  |       | +5.5 | V      |

| ADC OFFSET VOLTAGE <sup>1</sup>                             |                     |                            |     | ±0.1  |      | mV     |

| ADC GAIN ERROR <sup>1</sup>                                 |                     |                            |     | ±0.01 |      | %      |

| ADC UPDATE RATE                                             |                     |                            | 0.9 | 1     | 1.1  | kHz    |

| ADC TRANSITION NOISE                                        |                     |                            |     | 40    |      | μV rms |

| LIFETIME CELL TOTAL MEASUREMENT ERROR                       | C-TME               |                            |     |       |      |        |

|                                                             |                     | V <sub>DIF</sub> ≤ ±2.0 V  |     |       | ±1.5 | mV     |

|                                                             |                     | V <sub>DIF</sub> ≤ 3.3 V   |     |       | ±1.8 | mV     |

|                                                             |                     | V <sub>DIF</sub> ≤ 4.5 V   |     |       | ±2   | mV     |

|                                                             |                     | V <sub>DIF</sub> ≤ 5.5 V   |     |       | ±3   | mV     |

| INPUT LEAKAGE CURRENT                                       |                     | ADC off                    |     | 0     | ±250 | nA     |

| DIFFERENTIAL INPUT RESISTANCE                               | R <sub>IN_ADC</sub> | ADC on                     | 1.6 | 2.2   | 3    | ΜΩ     |

| DIFFERENTIAL INPUT RESISTANCE<br>DURING OPEN WIRE DETECTION |                     |                            |     | 1.75  |      | kΩ     |

| ADC SAMPLING FREQUENCY                                      | f <sub>S</sub>      |                            | 3.7 | 4.1   | 4.5  | MHz    |

<sup>&</sup>lt;sup>1</sup> The ADC specifications are guaranteed by the total measurement error specification.

Table 2. S-ADC DC Specifications

| Parameter                                                   | Symbol             | Test Conditions/Comments                                    | Min  | Тур              | Max  | Unit   |

|-------------------------------------------------------------|--------------------|-------------------------------------------------------------|------|------------------|------|--------|

| MEASUREMENT RESOLUTION                                      |                    |                                                             |      | 1.5 <sup>1</sup> |      | mV/bit |

| INPUT RANGE                                                 | V <sub>DIF_S</sub> | -0.1 V < (Sx to V-) < 80 V                                  | -0.3 |                  | +5.5 | V      |

| ADC OFFSET VOLTAGE <sup>2</sup>                             | _                  |                                                             |      | ±0.2             |      | mV     |

| ADC GAIN ERROR <sup>2</sup>                                 |                    |                                                             |      | ±0.03            |      | %      |

| ADC UPDATE RATE                                             |                    |                                                             | 110  | 125              | 140  | Hz     |

| ADC TRANSITION NOISE                                        |                    |                                                             |      | 20               |      | μV rms |

| S-ADC TOTAL MEASUREMENT ERROR                               | S-TME              |                                                             |      |                  |      |        |

|                                                             |                    | $0 \text{ V} \le \text{V}_{\text{DIF S}} \le 4.5 \text{ V}$ |      |                  | ±7   | mV     |

|                                                             |                    | $V_{DIF\_S} \le 5.5 \text{ V}$                              |      |                  | ±8   | mV     |

| INPUT LEAKAGE CURRENT                                       |                    | ADC off, V <sub>DIF S</sub> = 5.5 V                         |      | 10               | ±300 | nA     |

| DIFFERENTIAL INPUT RESISTANCE                               |                    | ADC on                                                      | 1    | 1.8              | 2.6  | ΜΩ     |

| DIFFERENTIAL INPUT RESISTANCE<br>DURING OPEN WIRE DETECTION |                    |                                                             |      | 20               |      | kΩ     |

| GAIN DURING OPEN WIRE DETECTION                             |                    | No open wire fault                                          | 85   | 90               | 95   | %      |

| ADC SAMPLING FREQUENCY                                      | f <sub>S</sub>     |                                                             | 3.7  | 4.1              | 4.5  | MHz    |

<sup>1</sup> The S-ADC result registers are normalized to the weight of the C-ADC results, allowing the same voltage conversion function to be applied. See the register description for more details.

analog.com Rev. 0 | 5 of 83

$<sup>^{2}\,\,</sup>$  The ADC specifications are guaranteed by the total measurement error specification.

## **SPECIFICATIONS**

Table 3. Auxiliary (AUX) ADC DC Specifications

| Parameter                                | Test Conditions/Comments                                | Min  | Тур   | Max       | Unit   |

|------------------------------------------|---------------------------------------------------------|------|-------|-----------|--------|

| MEASUREMENT RESOLUTION                   |                                                         |      | 0.15  |           | mV/bit |

| INPUT RANGE                              | GPIOx to V-                                             | -0.3 |       | $V_{REG}$ | V      |

| ADC OFFSET VOLTAGE <sup>1</sup>          |                                                         |      | -0.2  |           | mV     |

| ADC GAIN ERROR <sup>1</sup>              |                                                         |      | ±0.01 |           | %      |

| ADC UPDATE RATE                          |                                                         | 0.9  | 1     | 1.1       | kHz    |

| ADC TRANSITION NOISE                     |                                                         |      | 50    |           | μV rms |

| GPIOx TOTAL MEASUREMENT ERROR            |                                                         |      |       |           |        |

|                                          | 0 V < GPIOx to V− ≤ 3.3 V                               |      |       | ±2.8      | mV     |

|                                          | 3.3 V < GPIOx to V− ≤ 5 V                               |      |       | ±4.2      | mV     |

| DIAGNOSTIC MEASUREMENTS                  | Internal temperature, T = maximum specified temperature |      | ±5    |           | °C     |

|                                          | V <sub>REG</sub> pin                                    |      | ±0.1  | ±0.25     | %      |

|                                          | V <sub>REF2</sub> , VRES                                |      | ±0.02 | ±0.2      | %      |

|                                          | Digital supply voltage, V <sub>REGD</sub>               |      | ±0.1  | ±1.6      | %      |

|                                          | V+ to V-, V+ > 20 V                                     | -1   | ±0.05 | +0.5      | %      |

|                                          | -0.1 V ≤ S1N to V- ≤ 0.1 V                              |      | ±0.02 | 0.2       | %      |

| INPUT LEAKAGE CURRENT                    | AUX ADC off, GPIOx = 5 V                                |      | 10    | ±250      | nA     |

| INPUT RESISTANCE                         | AUX ADC on                                              | 1.5  | 2.7   | 3.5       | ΜΩ     |

| INPUT CURRENT DURING OPEN WIRE DETECTION | Pull-down current: GPIOx > 1.5 V                        | -140 | -200  | -260      | μΑ     |

|                                          | Pull-up current: GPIOx < V <sub>REG</sub> - 1.5 V       | 140  | 200   | 260       | μA     |

| ADC SAMPLING FREQUENCY                   |                                                         | 3.7  | 4.1   | 4.5       | MHz    |

<sup>&</sup>lt;sup>1</sup> The ADC specifications are guaranteed by the total measurement error specification.

Table 4. AUX2 ADC DC Specifications

| Parameter                       | Test Conditions/Comments  | Min  | Тур              | Max       | Unit   |

|---------------------------------|---------------------------|------|------------------|-----------|--------|

| MEASUREMENT RESOLUTION          |                           |      | 1.5 <sup>1</sup> |           | mV/bit |

| INPUT RANGE                     | GPIOx to V-               | -0.3 |                  | $V_{REG}$ | V      |

| ADC OFFSET VOLTAGE <sup>2</sup> |                           |      | ±0.2             |           | mV     |

| ADC GAIN ERROR <sup>2</sup>     |                           |      | ±0.05            |           | %      |

| ADC UPDATE RATE                 |                           | 110  | 125              | 140       | Hz     |

| ADC TRANSITION NOISE            |                           |      | 25               |           | μV rms |

| GPIOx TOTAL MEASUREMENT ERROR   |                           |      |                  |           |        |

|                                 | 0 V ≤ GPIOx to V− ≤ 3.3 V |      |                  | ±6        | mV     |

|                                 | 3.3 V < GPIOx to V− ≤ 5 V |      |                  | ±8        | mV     |

| INPUT LEAKAGE CURRENT           | AUX2 ADC off, GPIOx = 5 V |      | 10               | ±250      | nA     |

| INPUT RESISTANCE                | AUX2 ADC on               | 1.5  | 2.7              | 3.5       | ΜΩ     |

| ADC SAMPLING FREQUENCY          |                           | 3.7  | 4.1              | 4.5       | MHz    |

<sup>1</sup> The AUX2 ADC result registers are normalized to the weight of the AUX ADC results, allowing the same voltage conversion function to be applied. See the register description for more details.

analog.com Rev. 0 | 6 of 83

$<sup>^{2}\,\,</sup>$  The ADC specifications are guaranteed by the total measurement error specification.

## **SPECIFICATIONS**

Table 5. Voltage Reference Specifications

| Parameter                                            | Test Conditions/Comments               | Min   | Тур | Max   | Unit     |

|------------------------------------------------------|----------------------------------------|-------|-----|-------|----------|

| FIRST REFERENCE VOLTAGE                              | V <sub>REF1</sub> pin, no load         | 3     | 3.2 | 3.3   | V        |

| FIRST REFERENCE VOLTAGE TEMPERATURE COEFFICIENT (TC) | V <sub>REF1</sub> pin, no load         |       | 3   |       | ppm/°C   |

| FIRST REFERENCE VOLTAGE HYSTERESIS                   | V <sub>REF1</sub> pin, no load         |       | 20  |       | ppm      |

| FIRST REFERENCE VOLTAGE LONG-TERM DRIFT              | V <sub>REF1</sub> pin, no load         |       | 20  |       | ppm/√kHr |

| SECOND REFERENCE VOLTAGE                             | V <sub>REF2</sub> pin, no load         | 2.994 | 3   | 3.006 | V        |

|                                                      | V <sub>REF2</sub> pin, 1 kΩ load to V- | 2.994 | 3   | 3.006 | V        |

| OUTPUT CURRENT                                       | $\Delta V_{REF2} < \pm 2 \text{ mV}$   | -0.2  |     | +5    | mA       |

| SECOND REFERENCE VOLTAGE TC                          | V <sub>REF2</sub> pin, no load         |       | 10  |       | ppm/°C   |

| SECOND REFERENCE VOLTAGE HYSTERESIS                  | V <sub>REF2</sub> pin, no load         |       | 100 |       | ppm      |

| SECOND REFERENCE VOLTAGE LONG-TERM DRIFT             | V <sub>REF2</sub> pin, no load         |       | 60  |       | ppm/√kHr |

### Table 6. General DC Specifications

| Parameter                                                                                                                | Test Conditions/Comments                                                     | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|------|------|

| V+ SUPPLY CURRENT (See Figure 14)                                                                                        | Core in sleep, isoSPI in idle                                                |      |      |      |      |

|                                                                                                                          | Core in sleep, isoSPI in idle, V <sub>REG</sub> = 0 V, V+ = 60 V             |      | 4    | 10   | μA   |

|                                                                                                                          | Core in sleep, isoSPI in idle,V <sub>REG</sub> = 5 V, V+ = 60 V              |      | 2    | 5    | μA   |

|                                                                                                                          | Core in standby or extended balancing, V+ = 60 V                             | 4    | 10   | 24   | μA   |

|                                                                                                                          | Core in REFUP or measure or discharge timer monitor (DTM) measure, V+ = 60 V | 0.3  | 0.5  | 0.65 | mA   |

| / <sub>REG</sub> SUPPLY CURRENT (See Figure 14)                                                                          |                                                                              |      |      |      |      |

| I <sub>REG</sub> (CORE, MEASURE) = I <sub>REG</sub> (CORE,<br>REFUP) + I <sub>REG</sub> (CORE, ADCs ON)                  | Core in sleep, isoSPI in idle, V <sub>REG</sub> = 5 V                        |      | 2.2  | 8    | μA   |

|                                                                                                                          | Core in standby                                                              | 3    | 10   | 25   | μA   |

|                                                                                                                          | Core in REFUP                                                                | 2    | 2.3  | 3    | mA   |

|                                                                                                                          | Core in measure or DTM, additional current C-ADCs on                         | 4    | 4.5  | 5    | mA   |

|                                                                                                                          | Core in measure, additional current S-ADCs on                                | 3    | 3.9  | 4.5  | mA   |

|                                                                                                                          | Core in measure, additional current AUX ADCs on                              | 0.4  | 0.55 | 0.75 | mA   |

| ADDITIONAL V <sub>REG</sub> SUPPLY CURRENT IF isoSPI IN READY OR ACTIVE STATE AND t <sub>CLK</sub> = 0.5 µs <sup>1</sup> | isoSPI in idle state                                                         |      | 0    |      | mA   |

|                                                                                                                          | ISOMD = 0, ready                                                             | 2.6  | 3.2  | 3.9  | mA   |

|                                                                                                                          | ISOMD = 0, active                                                            | 7    | 8.5  | 11.5 | mA   |

|                                                                                                                          | ISOMD = 1, ready                                                             | 3.1  | 3.7  | 4.4  | mA   |

|                                                                                                                          | ISOMD = 1, active write                                                      | 7.5  | 9    | 12   | mA   |

|                                                                                                                          | ISOMD = 1, active read                                                       | 12.5 | 14   | 18   | mA   |

| ADDITIONAL V <sub>REG</sub> SUPPLY CURRENT FROM DISCHARGING                                                              | DCT = 0 and no cell discharge enabled                                        |      | 0    |      | μA   |

|                                                                                                                          | DCT ≠ 0 and/or some cell discharges asserted                                 | 10   | 40   | 130  | μA   |

| V+ SUPPLY VOLTAGE                                                                                                        | TME specifications met                                                       | 11   | 40   | 80   | V    |

| V <sub>REG</sub> SUPPLY VOLTAGE                                                                                          |                                                                              | 4.5  | 5    | 5.5  | V    |

| THERMAL SHUTDOWN PROCEDURE                                                                                               |                                                                              |      | 150  |      | °C   |

| DISCHARGE SWITCH ON RESISTANCE                                                                                           | SxN = 0 V (x = 1, 2, or 3), SxP = 6 V (x > 3)                                | 0.5  | 1    | 4    | Ω    |

| DRIVE PIN OUTPUT                                                                                                         |                                                                              |      |      |      |      |

| Output Voltage (V <sub>DRIVE</sub> )                                                                                     | T <sub>A</sub> = 25°C                                                        | 5.6  | 5.7  | 5.8  | V    |

| Output Current                                                                                                           | $\Delta V_{DRIVE}$ < ±100 mV                                                 | -0.2 |      | +1   | mA   |

| Temperature Coefficient                                                                                                  |                                                                              |      | -1.6 |      | mV/° |

analog.com Rev. 0 | 7 of 83

## **SPECIFICATIONS**

1 The active state current is calculated from DC measurements. The active state current is the additional average supply current into V<sub>REG</sub> when there are continuous 2 MHz communications on the isoSPI ports. Slower clock rates reduce the supply current.

## Table 7. Operation Timing Specifications

| Parameter                   | Symbol             | Test Conditions/Comments                                                                                                                                                                            | Min | Тур | Max | Unit |

|-----------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| REGULATOR START-UP TIME     | t <sub>WAKE</sub>  | V <sub>REG</sub> generated from DRIVE pin                                                                                                                                                           |     | 200 | 500 | μs   |

| WATCHDOG OR DISCHARGE TIMER | t <sub>SLEEP</sub> | DCTO[3:0] = 0000                                                                                                                                                                                    | 1.8 | 2   | 2.2 | sec  |

| REFERENCE WAKE-UP TIME      | t <sub>REFUP</sub> | Added to the conversion time when starting from the standby state. $t_{REFUP} = 0$ when starting from other states. $t_{REFUP}$ is independent of the number of channels measured and the ADC mode. | 2.7 | 3.5 | 4.4 | ms   |

| PWM DISCHARGE PERIOD        |                    |                                                                                                                                                                                                     |     | 937 |     | ms   |

## Table 8. Digital Pin DC Specifications

| Parameter                      | Symbol                     | Test Conditions/Comments      | Min | Тур | Max | Unit |

|--------------------------------|----------------------------|-------------------------------|-----|-----|-----|------|

| DIGITAL INPUT VOLTAGE HIGH     | V <sub>IH</sub>            | CSB, SCK, SDI, ISOMD, GPIOx   | 2.3 |     |     | V    |

| DIGITAL INPUT VOLTAGE LOW      | V <sub>IL</sub>            | CSB, SCK, SDI, ISOMD, GPIOx   |     |     | 0.8 | V    |

| DIGITAL INPUT LEAKCAGE CURRENT | I <sub>LEAK(DIG)</sub>     | SDI, ISOMD, GPIOx, SDO at 5 V |     |     | ±1  | μA   |

|                                |                            | CSB, SCK at 5 V               |     |     | 10  | μA   |

|                                |                            | CSB, SCK at 3.5 V             |     |     | 1   | μA   |

| DIGITAL OUTPUT, LOW SDO, GPIOx | V <sub>OL(SDO, GPIO)</sub> | Sinking 4 mA                  |     |     | 0.3 | V    |

#### Table 9. isoSPI Specifications

| Parameter                           | Symbol                   | Test Conditions/Comments                                         | Min | Тур  | Max | Unit |

|-------------------------------------|--------------------------|------------------------------------------------------------------|-----|------|-----|------|

| TRANSMITTER PULSE AMPLITUDE         | V <sub>A</sub>           | $V_A =  V_{IP} - V_{IM} $ , termination resistance = 50 $\Omega$ | 1   | 1.25 | 1.6 | V    |

| RECEIVER THRESHOLD SETTING          | V <sub>RX</sub>          |                                                                  | 240 | 300  | 360 | mV   |

| LEAKAGE CURRENT ON IPX AND IMX PINS | I <sub>LEAK(IP/IM)</sub> | Idle state, $V_{IP}$ or $V_{IM}$ , 0 V to $V_{REG}$              |     |      | 10  | μA   |

| TRANSMITTER DRIVE CURRENT           |                          | V <sub>CM</sub> set by the driver                                |     | 25   |     | mA   |

| COMMON-MODE VOLTAGE                 | V <sub>CM</sub>          | T <sub>A</sub> = 25°C, IPx and IMx pins not driving              |     | 3.2  |     | V    |

| RECEIVER INPUT RESISTANCE           | R <sub>IN</sub>          | ISOMD = 1, ready state IPA, IMA                                  | 35  |      |     | kΩ   |

|                                     |                          | ISOMD = 1, ready state IPB, IMB                                  | 100 |      |     | kΩ   |

| DIFFERENTIAL WAKE-UP VOLTAGE        | V <sub>WAKE</sub>        | t <sub>DWELL</sub> ≥ 240 ns                                      | 400 |      |     | mV   |

| START-UP TIME AFTER WAKE DETECTION  | t <sub>READY</sub>       |                                                                  |     |      | 10  | μs   |

| IDLE TIMEOUT DURATION               | t <sub>IDLE</sub>        |                                                                  | 4.3 | 5.5  | 6.7 | ms   |

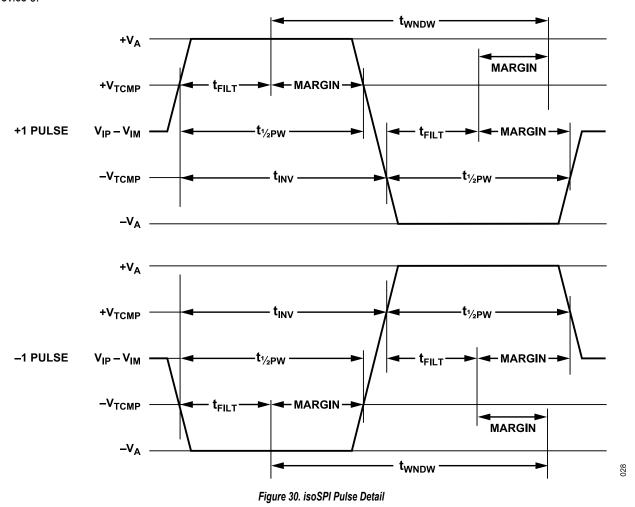

## ISOSPI PULSE TIMING SPECIFICATIONS

## Table 10. isoSPI Pulse Timing Specifications

| Parameter             | Symbol                | Test Conditions/Comments | Min | Тур | Max | Unit |

|-----------------------|-----------------------|--------------------------|-----|-----|-----|------|

| CHIP SELECT           |                       |                          |     |     |     |      |

| Half Pulse Width      | t <sub>½PW(CS)</sub>  | Transmitter              | 120 | 150 | 180 | ns   |

| Signal Filter         | t <sub>FILT(CS)</sub> | Receiver                 | 70  | 90  | 110 | ns   |

| Pulse Inversion Delay | t <sub>INV(CS)</sub>  | Transmitter              | 120 | 155 | 190 | ns   |

| Valid Pulse Window    | t <sub>WNDW(CS)</sub> | Receiver                 | 220 | 270 | 330 | ns   |

| DATA                  |                       |                          |     |     |     |      |

| Half Pulse Width      | t <sub>½PW(D)</sub>   | Transmitter              | 40  | 50  | 60  | ns   |

| Signal Filter         | t <sub>FILT(D)</sub>  | Receiver                 | 10  | 25  | 35  | ns   |

| Pulse Inversion Delay | t <sub>INV(D)</sub>   | Transmitter              | 40  | 55  | 65  | ns   |

| Valid Pulse Window    | t <sub>WNDW(D)</sub>  | Receiver                 | 70  | 90  | 110 | ns   |

analog.com Rev. 0 | 8 of 83

## **SPECIFICATIONS**

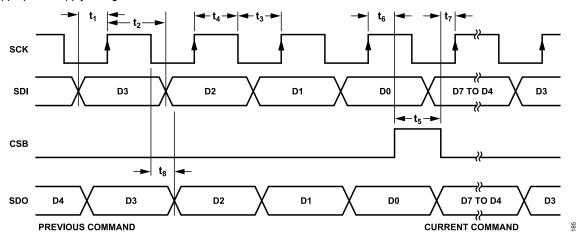

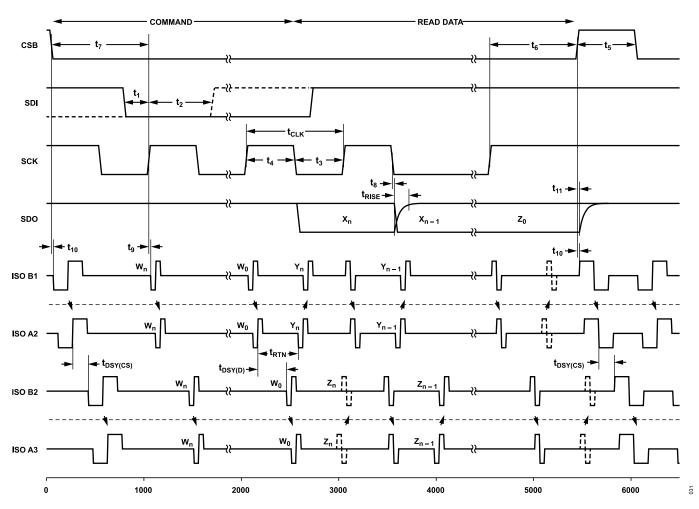

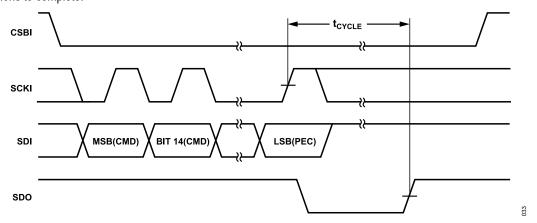

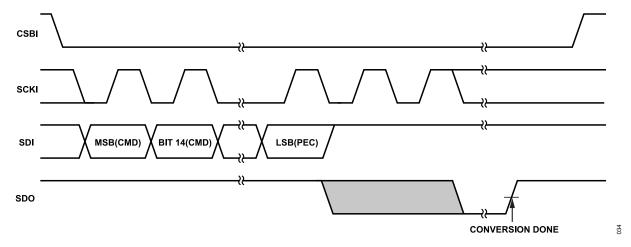

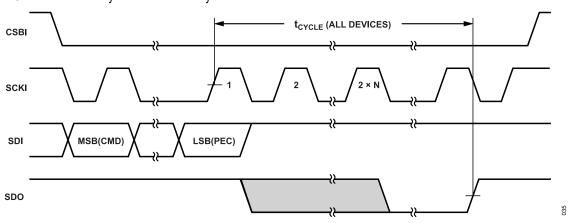

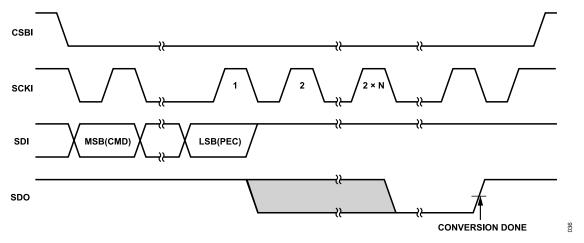

#### **SPI TIMING REQUIREMENTS**

Table 11. SPI Timing Requirements

| Symbol                         | Parameter                             | Test Conditions/Comments              | Min | Тур | Max | Unit |

|--------------------------------|---------------------------------------|---------------------------------------|-----|-----|-----|------|

| t <sub>CLK</sub> 1, 2          | SCK period                            |                                       | 0.5 |     |     | μs   |

| t <sub>1</sub> <sup>2</sup>    | SDI setup time before SCK rising edge |                                       | 25  |     |     | ns   |

| t <sub>2</sub> <sup>2</sup>    | SDI hold time after SCK rising edge   |                                       | 100 |     |     | ns   |

| $t_3^2$                        | SCK low                               | $t_{CLK} = t_3 + t_4 \ge 0.5 \ \mu s$ | 100 |     |     | ns   |

| $t_4^2$                        | SCK high                              | $t_{CLK} = t_3 + t_4 \ge 0.5 \ \mu s$ | 100 |     |     | ns   |

| $t_5^2$                        | CSB rising edge to CSB falling edge   |                                       | 2   |     |     | μs   |

| t <sub>6</sub> <sup>1, 2</sup> | SCK rising edge to CSB rising edge    |                                       | 0.5 |     |     | μs   |

| t <sub>7</sub> <sup>1, 2</sup> | CSB falling edge to SCK rising edge   |                                       | 0.5 |     |     | μs   |

<sup>1</sup> These timing specifications are dependent on the delay through the cable and include allowances for 50 ns of delay each direction. 50 ns corresponds to 10 m of Cat-5 cable (which has a velocity of propagation of 66% the speed of light). The use of longer cables requires derating these specifications by the amount of additional delay.

#### ISOSPI TIMING SPECIFICATIONS

Table 12. isoSPI Timing Specifications

| Symbol               | Parameter                              | Test Conditions/Comments                                      | Min  | Тур  | Max  | Unit |

|----------------------|----------------------------------------|---------------------------------------------------------------|------|------|------|------|

| t <sub>8</sub> 1, 2  | SCK falling edge to SDO valid          |                                                               |      |      | 60   | ns   |

| tg <sup>2</sup>      | SCK rising edge to short ±1 transmit   |                                                               | 230  | 265  | 300  | ns   |

| 102                  | CSB transition to long ±1 transmit     |                                                               |      |      | 100  | ns   |

| 1, 2<br>11           | CSB rising edge to SDO rising          |                                                               |      |      | 200  | ns   |

| RTN <sup>2</sup>     | Data return delay                      |                                                               | 150  | 185  | 220  | ns   |

| DSY(CS) <sup>2</sup> | Chip select daisy-chain delay          |                                                               | 100  | 160  | 200  | ns   |

| DSY(D) <sup>2</sup>  | Data daisy-chain delay                 |                                                               | 280  | 330  | 380  | ns   |

| LAG <sup>2</sup>     | Data daisy-chain lag (vs. chip select) | $(t_{DSY(D)} + t_{1/2}PW(D)) - (t_{DSY(CS)} + t_{1/2}PW(CS))$ | 0    | 70   | 100  | ns   |

| 5(GOV) <sup>2</sup>  | Chip select high to low pulse governor |                                                               | 0.54 | 0.67 | 0.85 | μs   |

| 6(GOV) <sup>2</sup>  | Data to chip select pulse governor     |                                                               | 0.69 | 0.86 | 1.1  | μs   |

| BLOCK <sup>2</sup>   | isoSPI port reversal blocking window   |                                                               | 2    |      | 10   | μs   |

These specifications do not include rise or fall time of SDO. Although fall time (typically 5 ns due to the internal pull-down transistor) is not a concern, the rising edge transition time (t<sub>RISE</sub>) is dependent on the pull-up resistance and load capacitance on the SDO pin. The time constant must be chosen such that SDO meets the setup time requirements of the MCU.

analog.com Rev. 0 | 9 of 83

<sup>&</sup>lt;sup>2</sup> This specification applies over the full operating temperature range.

<sup>&</sup>lt;sup>2</sup> This specification applies over the full operating temperature range.

#### **ABSOLUTE MAXIMUM RATINGS**

Table 13. Absolute Maximum Ratings

| Parameter                                      | Rating          |

|------------------------------------------------|-----------------|

| Total Supply Voltage, V+ to V-                 | -0.3 V to +85 V |

| Input Pins (Relative to V-)                    |                 |

| Cx (x ≤ 16)                                    | -0.3 V to +85 V |

| S1N, S1P, S2N                                  | -0.3 V to +12 V |

| S2P, S3N, S3P                                  | -0.3 V to +22 V |

| $Sx (4 \le x \le 16)$                          | -0.3 V to +85 V |

| IPA <sup>1</sup> , IMA <sup>1</sup> , IPB, IMB | -15 V to +15 V  |

| DRIVE                                          | -0.3 V to +7 V  |

| All Other Pins                                 | -0.3 V to +6 V  |

| Voltage Between Input Pins                     |                 |

| SxP to SxN                                     | -0.3 V to +12 V |

| S2N to S1N                                     | -0.3V to +12 V  |

| C16 to C16:15                                  | -6 V to +12 V   |

| C16:15 to C15                                  | -6 V to +12 V   |

|                                                |                 |

| C2:1 to C1 (ADBMS6830B in LQFP_EP              | -6 V to +12 V   |

| Current In and Out of Pins                     |                 |

| SxP to SxN (Discharge Switched Closed)         | 350 mA          |

| SxN to SxP (Discharge Switch Open)             | 10 mA           |

| Sx When Pulled Below V-                        | 10 mA           |

| IPA <sup>1</sup> , IMA <sup>1</sup> , IPB, IMB | 40 mA           |

| $V_{REG}$                                      | 30 mA           |

| All Other Pins                                 | 10 mA           |

| Temperature                                    |                 |

| Operating Range                                | -40°C to +125°C |

| Junction                                       | 150°C           |

| Storage Range                                  | -65°C to +150°C |

| Lead (Soldering, 10 sec)                       | 300°C           |

<sup>&</sup>lt;sup>1</sup> IPA and SCK are the same pin. IMA and CSB are the same pin. The absolute maximum rating for these pins depends on whether Port A is configured for SPI mode (CSB and SCK) or isoSPI mode (IPA and IMA).

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

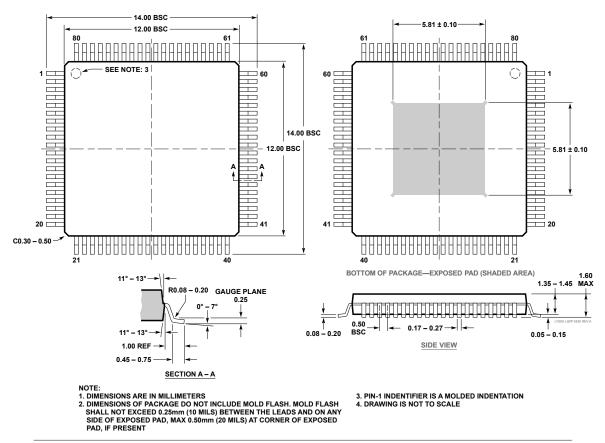

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

Table 14. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}^2$ | $\theta_{JCBOT}$ | $\theta_{\text{JCTOP}}$ | Unit |

|---------------------------|-----------------|------------------|-------------------------|------|

| 05-08-1783                | 18.5            | 1.4              | 19.2                    | °K/W |

The exposed pad must be connected to the V- plane for proper thermal management.

$\theta_{\text{JA}}$  is the natural convection, junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{\text{JCBOT}}$  is the bottom junction-to-case thermal resistance.

$\theta_{JCTOP}$  is the top junction-to-case thermal resistance.

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

## **ESD Ratings for ADBMS6830B**

Table 15. ADBMS6830B, 80-Lead LQFP EP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±3500                   | 2     |

| CDM       | ±500                    | C2B   |

|           | Corners pins: ±750      |       |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 10 of 83

$<sup>^{2}~</sup>$  Board layout impacts thermal characteristics, such as  $\theta_{\text{JA}}.$

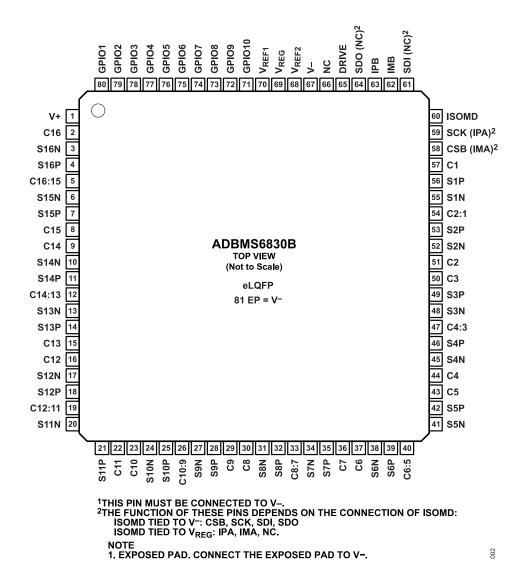

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration, 80-Lead LQFP EP

Table 16. Pin Function Descriptions

| Pin No. (LQFP_EP)                                                                                                          | Mnemonic                 | Description                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                                                                                                          | V+                       | Positive Supply Pin.                                                                                                                                                                                                                                       |

| 2, 5, 8, 9, 12, 15, 16, 19, 22, 23, 26, 29, 30, 33, 36, 37, 40, 43, 44, 47, 50, 51, 54, 57                                 | C16 to C1                | Differential Inputs for Cell Measurement ADCs.                                                                                                                                                                                                             |

|                                                                                                                            | C9N                      | Negative Terminal of the Ninth C-Measurement Channel. See the Bus Bar Monitoring and Bypassing section for usage details.                                                                                                                                  |

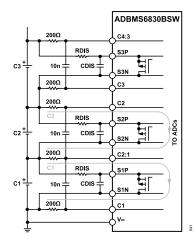

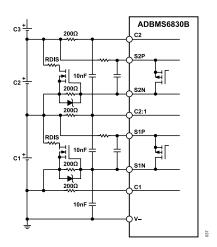

| 3, 4, 6, 7, 10, 11, 13, 14, 17, 18, 20, 21, 24, 25, 27, 28, 31, 32, 34, 35, 38, 39, 41, 42, 45, 46, 48, 49, 52, 53, 55, 56 | S16P to S1P, S16N to S1N | Balance Inputs and Outputs. 16 P-channel metal-oxide semiconductor field effect transistors (P-MOSFETs) are connected between SxP and SxN. Inputs to the S-ADCs.                                                                                           |

| 58, 59                                                                                                                     | IMA, IPA                 | Isolated 2-Wire Serial Interface Port A. IPA (plus) and IMA (minus) are a differential input/output pair.                                                                                                                                                  |

| 58, 59, 61, 64                                                                                                             | CSB, SCK, SDI, SDO       | 4-Wire SPI. Active low chip select (CSB), serial clock (SCK), and serial data input (SDI) are digital inputs. Serial data out (SDO) is an open-drain, N-channel metal-oxide semiconductor (NMOS) output pin. SDO requires a 1 k $\Omega$ pull-up resistor. |

analog.com Rev. 0 | 11 of 83

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Table 16. Pin Function Descriptions (Continued)

| Pin No. (LQFP_EP) | Mnemonic          | Description                                                                                                                                                                                                   |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60                | ISOMD             | Serial Interface Mode. Connecting ISOMD to V <sub>REG</sub> configures the ADBMS6830B for 2-wire isolated interface (isoSPI) mode. Connecting ISOMD to V- configures the ADBMS6830B for 4-wire SPI mode.      |

| 62, 63            | IMB, IPB          | Isolated 2-Wire Serial Interface Port B. IPB (plus) and IMB (minus) are a differential input/output pair.                                                                                                     |

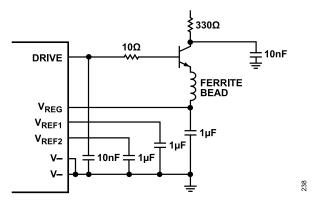

| 65                | DRIVE             | Connect the base of an external negative positive negative (NPN) transistor to this pin. Connect the collector to V+ and the emitter to $V_{REG}$ .                                                           |

| 66                | NC                | Leave unconnected (preferred) or connect to V                                                                                                                                                                 |

| 67                | V-                | Negative Supply Pins. The V- pins must be shorted together, external to the IC.                                                                                                                               |

| 68                | V <sub>REF2</sub> | Buffered Second Reference Voltage for Driving Multiple 10 k $\Omega$ Thermistors. Bypass with an external 1 $\mu F$ capacitor.                                                                                |

| 69                | $V_{REG}$         | 5 V Regulator Input. Bypass with an external 1 μF capacitor.                                                                                                                                                  |

| 70                | V <sub>REF1</sub> | ADC Reference Voltage. Bypass with an external 1 µF capacitor. No DC loads allowed.                                                                                                                           |

| 71 to 80          | GPIO10 to GPIO1   | General-Purpose Inputs/Outputs. Can be used as digital inputs or digital outputs, or as analog inputs with a measurement range from V- to 5 V. GPIO3 to GPIO5 can be used as an I <sup>2</sup> C or SPI port. |

|                   | Exposed Pad       | Exposed Pad. Connect the exposed pad to V                                                                                                                                                                     |

analog.com Rev. 0 | 12 of 83

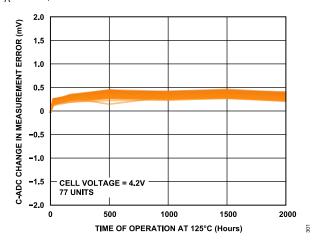

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

Figure 4. C-ADC Change in Measurement Error vs. Time of Operation at 125°C

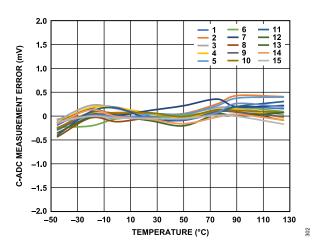

Figure 5. C-ADC Measurement Error at 4.2 V vs. Temperature for 15 Devices

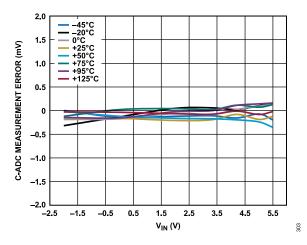

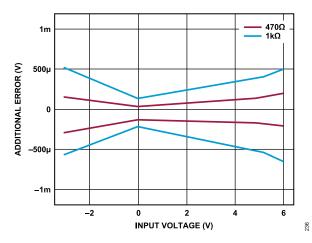

Figure 6. C-ADC Measurement Error vs. Input Voltage (V<sub>IN</sub>)

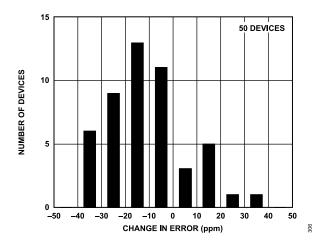

Figure 7. C-ADC Gain Error Due to IR Reflow

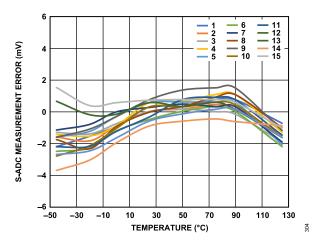

Figure 8. S-ADC Measurement Error at 4.2 V vs. Temperature for 15 Devices

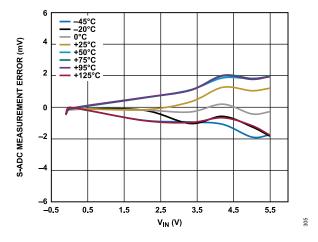

Figure 9. S-ADC Measurement Error vs. VIN

analog.com Rev. 0 | 13 of 83

## **TYPICAL PERFORMANCE CHARACTERISTICS**

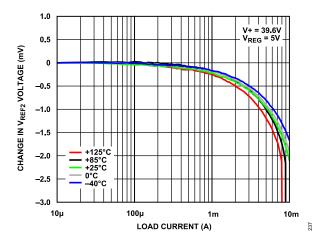

Figure 10. Change in V<sub>REF2</sub> Voltage vs. Load Current

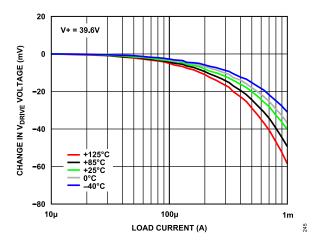

Figure 11. Change in V<sub>DRIVE</sub> Voltage vs. Load Current

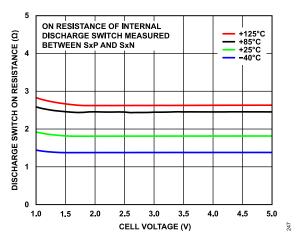

Figure 12. Discharge Switch On Resistance vs. Cell Voltage

analog.com Rev. 0 | 14 of 83

#### THEORY OF OPERATION

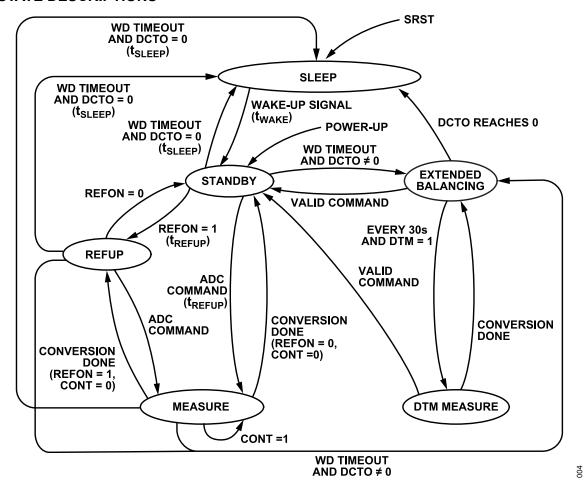

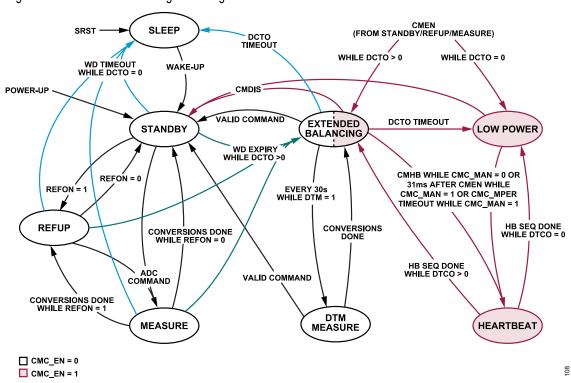

#### **CORE STATE DESCRIPTIONS**

Figure 13. Core State Diagram

analog.com Rev. 0 | 15 of 83

#### THEORY OF OPERATION

### Standby State

At first power-up or after a power-on reset (POR), the device resets and enters the standby state. The standby state allows communicating with the ADBMS6830B, and cell discharge and balancing can be enabled by writing to the PWM register group. The reference and the ADCs are off. The watchdog timer and/or the discharge timer is running. The DRIVE pin powers the  $\rm V_{REG}$  pin to 5.2 V through an external transistor controlled by the DRIVE pin.  $\rm V_{REG}$  can also be powered through an external source. In this case, the internal regulator must be disabled to avoid contention by floating the DRIVE pin. The IC can perform PWM discharge in the standby state.

When a valid ADC command is received, or if the REFON bit is set to 1 in the Configuration Register Group A, the IC pauses for  $t_{REFUP}$  to allow the reference to power up. Then, the IC enters either the REFUP or measure state. Otherwise, if no valid commands are received for  $t_{SLEEP}$ , the IC returns to the sleep state if DCTO = 0, or enters the extended balancing state if DCTO  $\neq$  0.

#### Sleep State

When the watchdog timer times out, the ADBMS6830B enters the sleep state with minimum power consumption. The references and ADCs are powered down. The isoSPI ports are in the idle state. The DRIVE pin is 0 V. An internal 3 V regulator supplies power to detect a wake-up signal and to retain 6 bytes of user programmable data in the retention registers. All other registers are reset to their default value. If a wake-up signal is received, the ADBMS6830B enters the standby state.

#### **REFUP State**

To reach the REFUP state, the REFON bit in Configuration Register Group A must be set to 1 using the WRCFGA command. In the REFUP state, the ADCs are off. The reference is powered up so that the ADBMS6830B can initiate ADC conversions faster than from the standby state.

When a valid ADC command is received, the IC moves to the measure state to begin the conversion. Otherwise, the ADBMS6830B returns to the standby state when the REFON bit is set to 0. If no valid commands are received for  $t_{SLEEP}$ , the IC either returns to the sleep state if DCTO = 0, or enters the extended balancing state if DCTO  $\neq$  0.

#### **Measure State**

When receiving a valid ADC command (ADCV, ADSV, ADAX, or ADAX2), the ADBMS6830B enters the measure state to perform ADC conversions. When entering this state, the reference and ADCs are powered.

If the CONT bit in the ADC command is set to 0, the ADBMS6830B executes a single conversion cycle according to the ADC com-

mand, updates the corresponding result registers, and returns to the standby state or REFUP state.

If the CONT bit in the ADC command is set to 1, the ADBMS6830B continuously executes conversion cycles according to the ADC command, updates the corresponding result registers with a 1 kHz update rate, and feeds the ADC results to the corresponding IIR filter preconfigured according to the filter configuration register (see the Internal Digital Filtering section for more details). If a new ADCV, ADSV, ADAX, or ADAX2 command is received during the conversions, the ongoing conversions of the concerned ADCs stop, and new measurements start, allowing re-synchronization of multiple ADBMS6830Bs in a stack.

## **Extended Balancing and DTM Measure States**

In the DTM measure state, the ADBMS6830B periodically monitors cell voltages while PWM balancing and the discharge timer are active without interacting with the host controller. The host must configure the PWM balancing, clear all DCC bits, and set the DTMEN bit to enable this feature.

If the watchdog timer expires and the discharge timer monitor is enabled and not timed out, the ADBMS6830B enters the extended balancing state in which the configured PWM discharge continues. From this state, the ADBMS6830B transitions every 30 sec to the DTM measure state to measure the cell voltages, compare the result to the overvoltage (OV) and undervoltage (UV) thresholds, and update the OV and UV flags in the status register accordingly. When the UV threshold is reached for any cell, the ADBMS6830B discontinues the discharge of the concerned cell. If the cell voltage recovers above the UV threshold, the discharge of that cell resumes.

The discharge is not muted when cell measurements are performed in the low power cell monitoring (LPCM) heartbeat mode or DTM measure state. As a result, measurements are affected by the voltage drop of the discharge current over the cell cable resistance. The PWM discharge happens asynchronously to the ADC measurements. Therefore, it is not predictable if a measurement is altered by the voltage drop. Depending on the cable resistance and the discharge current, the intended voltage thresholds (VOV, VUV, CMT CUV, and CMT COV) may not be checked accurately.

The ADBMS6830B transitions to the standby state upon reception of any valid command, or to the sleep state when the discharge timeout (DCTO) value expires. PWM balancing continues even when the DCTO value has not expired.

analog.com Rev. 0 | 16 of 83

#### THEORY OF OPERATION

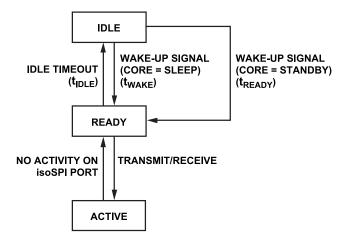

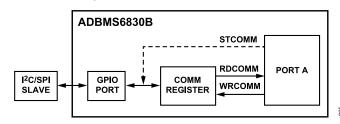

#### ISOSPI STATE DESCRIPTION

The ADBMS6830B has two isoSPI ports for daisy-chain communication: Port A and Port B.

## NOTES 1. STATE TRANSITION DELAYS ARE DENOTED BY $(t_x)$ .

Figure 14. isoSPI State Diagram

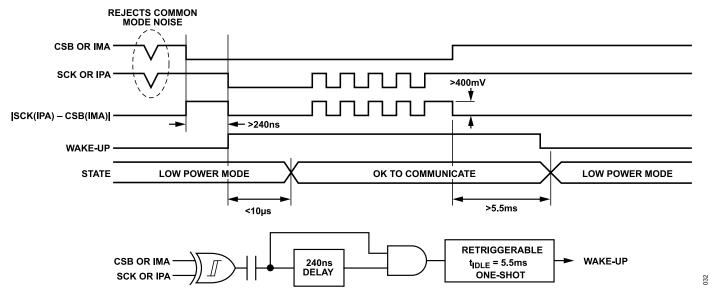

#### **Idle State**

In the idle state, the isoSPI ports are powered down.

When isoSPI Port A or Port B receives a wake-up signal, the isoSPI enters the ready state. This transition happens quickly (within  $t_{READY}$ ) if the core is in the standby state. If the core is in the sleep state when the isoSPI receives a wake-up signal, the IC transitions to the ready state within  $t_{WAKF}$ .

## **Ready State**

In the ready state, the isoSPI ports are ready for communication. The serial interface current in this state depends on the status of the ISOMD pin.

If there is no activity (that is, no wake-up signal) on Port A or Port B for greater than  $t_{\text{IDLE}}$ , the ADBMS6830B moves to the idle state. When the serial interface is transmitting or receiving data, the ADBMS6830B moves to the active state.

#### **Active State**

9

The ADBMS6830B is transmitting/receiving data using one or both of the isoSPI ports in the active state. The serial interface consumes maximum power in this state. The supply current increases with the clock frequency as the density of isoSPI pulses increases.

analog.com Rev. 0 | 17 of 83

#### **POWER SUPPLY**

The ADBMS6830B is powered by two pins: V+ and  $V_{REG}$ . The V+ input requires a voltage greater than or equal to 11 V, independent of the voltage of the cell measurement inputs pins. V+ provides power mainly to the highly accurate Zener reference voltage. The  $V_{REG}$  input requires 5 V and provides power to the remaining core circuits and the isoSPI circuitry, and to drive the discharge switches. The  $V_{REG}$  input can be powered through an external transistor that is driven by the regulated DRIVE output pin. Alternatively,  $V_{REG}$  can be powered by an external supply.

The power consumption varies according to the operational states. In the sleep state, the ADBMS6830B consumes 4  $\mu A$  provided either entirely by the V+ pin or partly by the V $_{REG}$  pin if the latter is powered by an external supply. The V+ pin current depends only on the core state, whereas the  $V_{REG}$  pin current depends on both the core state and isoSPI state and can be divided into two components.

$$I_{REG} = I_{REG(Core)} + I_{REG(isoSPI)}$$

When measuring, the current drawn depends on the number of ADCs that are turned on to measure.

I<sub>REG(Core)</sub> is thus the sum of the power consumed in the REFUP state and the additional current consumed by the ADCs.

$I_{REG}$  (Core, Measure) =  $I_{REG}$  (Core, REFUP) +  $I_{REG}$  (Core, ADCs on)

The Specifications section provides an overview of the power consumption in measure state, dependent on the number of ADCs used.

In a typical example, I<sub>REG(Core)</sub> can be estimated as

$$I_{REG(Core)} = I_{regREFUP} + I_{regCADC} + n_{SADC} \times t_{SADC} / t_{FDTI} \times I_{regSADC} + (n_{AUX} \times t_{AUX} + n_{AUX2} \times t_{AUX2}) / t_{FDTI} \times I_{regAUX} \approx 8 \text{mA}$$

based on the following assumptions:

- t<sub>AUX</sub> = 1 ms, AUX conversion time

- n<sub>AUX</sub> = 18, number of AUX conversions per fault detection time interval (FDTI) (all channels for diagnostics and all GPIOs)

- ▶ t<sub>AUX2</sub> = 8 ms, AUX2 conversion time

- ► n<sub>AUX2</sub> = 10, number of AUX2 conversions per FDTI (all 10 GPIOs)

- ▶ t<sub>FDTI</sub> = 100 ms, fault detection time interval

- ► t<sub>SADC</sub> = 8 ms, S-ADC conversion time

- ▶ n<sub>SADC</sub> = 3, number of S-ADC conversions per FDTI

- I<sub>regAUX</sub> = 0.55 mA, AUX ADC current consumption (AUX ADC and AUX2 ADC active)

- ► I<sub>regREFUP</sub> = 2.3 mA, current consumption in REFUP state, which is also the base current consumption

- ► I<sub>reaCADC</sub> = 4.5 mA, C-ADC current consumption (for all 16)

- ► I<sub>reqSADC</sub> = 3.9 mA, S-ADC current consumption (for all 16)

The isoSPI draws current only from the V<sub>REG</sub> pin. Table 17 provides equations to approximate the isoSPI current in function of the isoSPI state.

Table 17. Power Consumption for isoSPI Communication

| isoSPI State | ISOMD Logic    | I <sub>REG(isoSPI)</sub>                                                                                                                                                                    |

|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ldle         | Not applicable | 0 mA                                                                                                                                                                                        |

| Ready        | 1              | 3.7 mA                                                                                                                                                                                      |

|              | 0              | 3.2 mA                                                                                                                                                                                      |

| Active       | 1              | Active write: $I_{REG(isoSPI)}$ (ready state) + 2 × $t_{/2PW(D)}$ / $t_{CLK} \times I_{DRV}$<br>Active read: $I_{REG(isoSPI)}$ (ready state) + 4 × $t_{/2PW(D)}$ / $t_{CLK} \times I_{DRV}$ |

|              | 0              | Active write/read: $I_{REG(isoSPI)}$ (ready state) + 2 × $t_{/PW(D)}/t_{CLK} \times I_{DRV}$                                                                                                |

As an example, with the following assumptions:

- I<sub>regRd</sub> = 14 mA, active read current consumption (2 Mbps, 100% SPI duty cycle).

- I<sub>regWr</sub> = 9 mA, active write current consumption (2 Mbps, 100% SPI duty cycle).

- I<sub>regRdy</sub> = 3.7 mA, isoSPI ready state current consumption (when not communicating and t<sub>IDI F</sub> not elapsed).

- duty = 0.8, SPI communication duty cycle, assuming worst case 80%.

- ▶ wrRatio = 0.3, assuming 30% of commands are write commands (for example, WRCFGA, WRCFGB, WRPWM....).

- ► I<sub>REG(isoSPI)</sub> can be estimated as

$$I_{REG(isoSPI)} = \text{duty} \times (wrRatio \times I_{regWr} + (1 - wrRatio) \times I_{regRd}) + (1 - \text{duty}) \times I_{regRdy}$$

- $\approx 11$ mA

- ► Total I<sub>RFG</sub> current: 8 mA + 11 mA = 19 mA.

- ▶ For the typical application using an external NPN transistor to generate V<sub>REG</sub>, this current is taken from MODULE+, to which V+ is also connected. The typical V+ current consumption in the measure state is 0.5 mA. As a result, the typical MODULE+ current consumption is < 20 mA for the assumed isoSPI communication duty cycle.

analog.com Rev. 0 | 18 of 83

#### **CELL VOLTAGE MEASUREMENTS**

## C-ADC AND S-ADC OPERATIONS AND COMMANDS

16 ADCs are dedicated to measure the 16 differential cell inputs synchronously and are therefore called C-ADCs. C-ADCs feature an input range of –2 V to +5.5 V and a sampling frequency of ~4 MHz, giving out 16-bit results every 1 ms with an LSB of 150  $\mu V$ . Furthermore, every 8 ms an average of the last eight conversions of the ADC is provided.

16 additional ADCs are dedicated to measure the 16 differential inputs (SxP and SxN) synchronously with an input range of 0 V to 5. 5 V and a sampling frequency of ~4 MHz, giving out results every 8 ms. These S-ADCs allow redundant measurement of the cell voltages using an independent measurement path from the C-ADCs.

Refer to the memory map description for the representation of the measurement results in the respective 16-bit registers (see the Memory Map section).

Two commands can trigger C-ADC and S-ADC measurements: ADCV triggers cell voltage conversions with or without redundancy, and ADSV triggers S-ADC conversions.

If a new ADCV or ADSV is received during the conversions, the ongoing conversions of the concerned ADCs stop, and new measurements start, allowing re-synchronization of multiple ADBMS6830Bs in a stack. The corresponding result registers are reset upon reception of a new ADCV or ADSV.

Table 18. C-ADC and S-ADC Commands

| Command                                                 |      |                  | CC[10:0] - Command Code |   |    |      |   |   |     |   |      |       |       |

|---------------------------------------------------------|------|------------------|-------------------------|---|----|------|---|---|-----|---|------|-------|-------|

| Description                                             | Name | INC <sup>1</sup> | 10                      | 9 | 8  | 7    | 6 | 5 | 4   | 3 | 2    | 1     | 0     |

| Start Cell Voltage ADC<br>Conversion and Poll<br>Status | ADCV | Yes              | 0                       | 1 | RD | CONT | 1 | 1 | DCP | 0 | RSTF | OW[1] | OW[0] |

| Start S-ADC<br>Conversion and Poll<br>Status            | ADSV | Yes              | 0                       | 0 | 1  | CONT | 1 | 1 | DCP | 1 | 0    | OW[1] | OW[0] |

<sup>&</sup>lt;sup>1</sup> INC indicates whether the command counter increments for the command.

analog.com Rev. 0 | 19 of 83

#### **CELL VOLTAGE MEASUREMENTS**

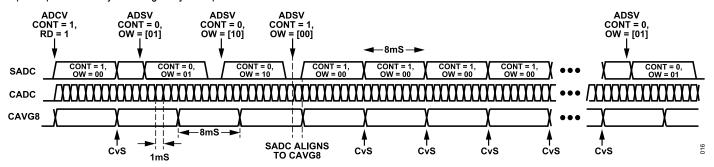

## CONTINUOUS OR SINGLE SHOT MEASUREMENTS

Both C-ADCs and S-ADCs can be configured to perform a single measurement (CONT = 0) or continuous measurements (CONT = 1). In continuous mode, the result registers of the corresponding ADCs are updated at their conversion rate of 1 ms (C-ADC) and 8 ms (S-ADC). To end continuous measurement mode of the respective ADC, send an ADCV or ADSV with CONT = 0. The addressed ADC then performs a last single shot measurement before turning off

#### REDUNDANT MEASUREMENTS

There are two methods to obtain redundant measurements: a direct method and an indirect method.

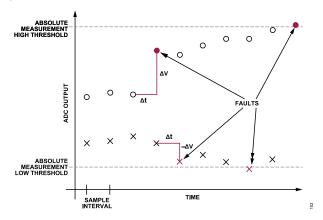

The direct method involves setting the redundancy bit (RD) in an ADCV command. In this case, the C-ADCs and S-ADCs are both triggered to provide redundancy. After 8 ms, the average results of the C-ADCs are compared to the results of the S-ADCs. If the results do not match within the threshold set by the CTH[2:0] in Configuration Register A, the CSxFLT flag is set in the Status Register Group C. A single shot measurement triggered with RD = 1 and CONT = 0 takes 8 ms. If an ADSV is issued with CONT = 0, no further comparison is performed, and the S-ADC performs a single shot conversion and then stops.

Note that if an ADCV with RD = 1 is issued, the open wire switches are reset (open) to ensure a proper comparison. The Algorithm for Cell Measurement with Diagnostics section describes a sequence of redundant measurements and open wire detection measurements by means of the S-ADC for high functional safety coverage.

The indirect method allows synchronizing the S-ADCs to the already running C-ADCs.

If an ADSV is issued with CONT = 1 while the C-ADCs are in continuous mode, the S-ADCs wait for the current C-ADC average of 8 conversions to finish, start conversions synchronous to the CAVG8, and compare the CAVG8 and S-ADC results. When redundant measurements with subsequent result comparison are started or ongoing, the COMP bit in the status register group is set to one for latent fault coverage.

#### **DISCHARGE DURING MEASUREMENTS**

The ADBMS6830B allows interrupting PWM discharge during measurements to acquire cell voltage without voltage drop in cabling due to discharge current. The behavior is controlled via the RD, DCP, and CONT bits and described in Table 19.

Table 19. ADC Command Control Bits

|         |        | Inputs | ;    |                                                                                                                                                                                                                                                                            |

|---------|--------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command | $RD^3$ | DCP    | CONT | PWM Discharge Status <sup>1, 2</sup>                                                                                                                                                                                                                                       |

| ADCV    | 0      | 0      | 1    | Stop ongoing C-ADC conversion and restart for continuous conversion of C-ADC. PWM controlled discharge remains unaffected.                                                                                                                                                 |

|         | 1      | 0      | 1    | PWM controlled discharge is interrupted. Stop ongoing C-ADC conversion and restart for continuous conversion of C-ADC and S-ADC to make redundant comparison. PWM discharge remains off if no further command is sent.                                                     |

|         | 1      | 0      | 0    | PWM controlled discharge is interrupted. Stop ongoing C-ADC conversion and make single-shot conversion of C-ADC and S-ADC for redundant comparison. PWM discharge remains off for the duration of the redundant C-ADC and S-ADC conversion (8 ms typical).                 |

|         | 0      | 0      | 0    | Immediately trigger single-shot conversion of C-ADC. Operation of S-ADC and PWM controlled discharge remains unaffected.                                                                                                                                                   |

|         | X      | 1      | 0    | Stop ongoing C-ADC conversion and make single-shot conversion of C-ADC (RD = 0) or C-ADC and S-ADC (RD = 1). No effect on PWM controlled discharge.                                                                                                                        |

|         | X      | 1      | 1    | Invalid command is ignored. Current operation remains unaffected, CC not incremented.                                                                                                                                                                                      |

| ADSV    | X      | 0      | 1    | If C-ADC is converting continuously, the S-ADC is synchronized to the C-ADC to make continuous conversion of C-ADCs and S-ADCs for redundant comparison. If C-ADC is not converting, only the S-ADC makes continuous conversions. The PWM controlled discharge is stopped. |

|         | X      | 0      | 0    | PWM controlled discharge is interrupted for single-shot conversion of S-ADC. Operation of C-ADC remains unaffected.                                                                                                                                                        |

|         | X      | 1      | 0    | PWM controlled discharge continues during measurement. Single-shot conversion of S-ADC. Operation of C-ADC remains unaffected.                                                                                                                                             |

|         | X      | 1      | 1    | Current operation remains unaffected, CC not incremented.                                                                                                                                                                                                                  |

Discharge always continues if statically enabled via the DCC bits and not interrupted by other higher priority events such as WRCFGA, WRCFGB, mute, and thermal shutdown.

analog.com Rev. 0 | 20 of 83

<sup>&</sup>lt;sup>2</sup> Any ADCV interrupts the ongoing C-ADC conversions and restarts the C-ADCs. For this reason, it is recommended to trigger redundant measurements with the ADSV command every fault tolerant time interval (FTTI)(ADSV with DCP = 0, CONT = 1).

<sup>3</sup> X means 0 or 1.

#### **CELL VOLTAGE MEASUREMENTS**

#### **OPEN WIRE SWITCHES**

As shown in Figure 2, the ADBMS6830B features current-limited switches at the cell measurement inputs. Activating these switches detects if the connection to the cell is broken. The open wire switches in the corresponding measurement path are controlled by the open wire bits (OW[1:0]), as shown in Table 20.

Table 20. Open Wire Switch Control Bits

| OW[1] | OW[0] | Open Wire Switches                                                                |

|-------|-------|-----------------------------------------------------------------------------------|

| 0     | 0     | All channels: off                                                                 |

| 0     | 1     | Even channels on (S2 and C2, S4 and C4,) odd channels off (S1 and C1, S3 and C3,) |

| 1     | 0     | Even channels off (S2 and C2, S4 and C4,) odd channels on (S1 and C1, S3 and C3,) |

| 1     | 1     | All channels on                                                                   |

See the Cell Open Wire Detection section for more details.

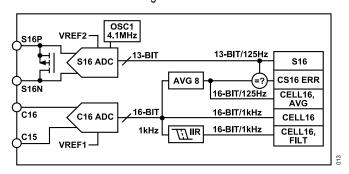

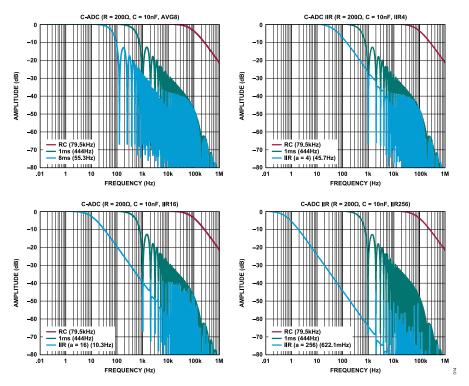

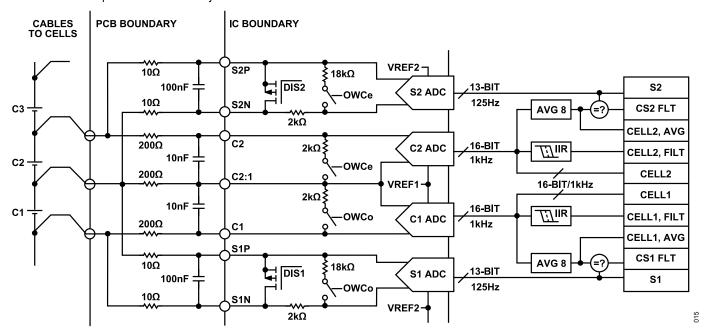

#### INTERNAL DIGITAL FILTERING

The figure below depicts the overall signal processing within the ADBMS6830B. The input voltages are samples by the S-ADCs and the C-ADCs with a sampling frequency of roughly 4.1 MHz. Both S-ADCs and C-ADCs are oversampling ADCs. Whereas the C-ADCs provide a new measurement result every 1 ms, the result of the S-ADCs is updated every 8 ms. The C-ADC measurement results are then averaged over 8 ms and, in case redundancy is required, compared to the synchronous results of the S-ADCs.

The 16-bit results of the C-ADCs are also fed to configurable IIR filters for further noise filtering.

Figure 15. Integrated Digital Filters

The transfer function of the IIR filter is represented by

$$Y[n] = Y[n-1] + (X[n] - Y[n-1])/a$$

where:

X[n] represents the nth input.

Y[n] represents the nth output of the filter.

a is the filter parameter given in Table 21.

The -3 dB corner frequency can be chosen between 110 Hz and 0.625 Hz by programming the FC[2:0] bits in the Configuration Register Group A (see Table 21).

Table 21. IIR Frequency Settings

| -3 dB Corner<br>Frequency | FC[2] | FC[1] | FC[0] | Filter Parameter |

|---------------------------|-------|-------|-------|------------------|

| Filter Disabled           | 0     | 0     | 0     | N/A <sup>1</sup> |

| 110                       | 0     | 0     | 1     | 2                |

| 45                        | 0     | 1     | 0     | 4                |

| 21                        | 0     | 1     | 1     | 8                |

| 10                        | 1     | 0     | 0     | 16               |

| 5                         | 1     | 0     | 1     | 32               |

| 1.25                      | 1     | 1     | 0     | 128              |

| 0.625                     | 1     | 1     | 1     | 256              |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

If all three bits are set to zero, no IIR filtering is applied.

The filtered results are stored in the Filtered Cell Voltage Register Groups A through E. The IIR filters can be reset by either issuing a clear filtered cell voltage register group (CLRFC) command or by setting the reset filter (RSTF) bit in an ADCV command. Furthermore, the filters are reset if the filter corner frequency is changed. To speed up the settling time, the filters are preloaded with the first sample arriving after a reset. Note that any C-ADC result, whether obtained in continuous mode or in single shot mode, is added to IIR filter. Table 22 summarizes the option of digital filtering with the ADBMS6830B.