# Dual 160 MHz Rail-to-Rail Amplifier

AD8042

#### **FEATURES**

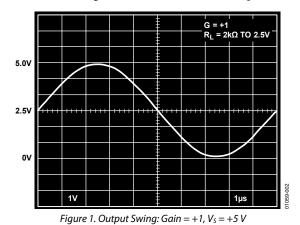

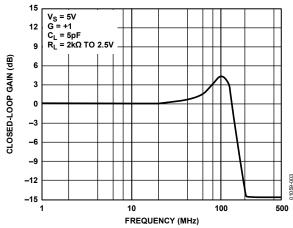

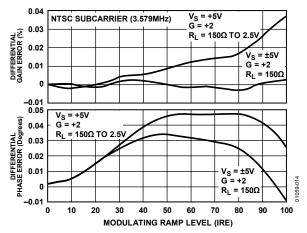

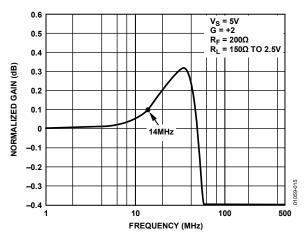

Single AD8041 and quad AD8044 also available Fully specified at +3 V, +5 V, and  $\pm 5$  V supplies Output swings to within 30 mV of either rail Input voltage range extends 200 mV below ground No phase reversal with inputs 0.5 V beyond supplies Low power of 5.2 mA per amplifier High speed and fast settling on 5 V 160 MHz, -3 dB bandwidth (G = +1) 200 V/ $\mu$ s slew rate 39 ns settling time to 0.1% Good video specifications ( $R_L = 150 \ \Omega$ , G = +2) Gain flatness of 0.1 dB to 14 MHz 0.02% differential gain error 0.04° differential phase error

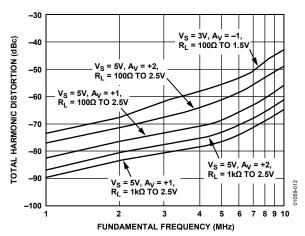

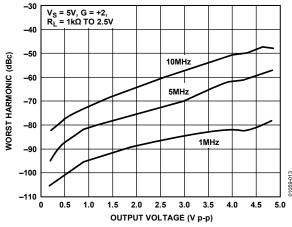

Low distortion: -64 dBc worst harmonic @ 10 MHz

#### **APPLICATIONS**

Video switchers

Distribution amplifiers

Analog-to-digital drivers

Professional cameras

CCD Imaging systems

Ultrasound equipment (multichannel)

Drives 50 mA 0.5 V from supply rails

### **GENERAL DESCRIPTION**

The AD8042 is a low power voltage feedback, high speed amplifier designed to operate on +3 V, +5 V, or  $\pm 5$  V supplies. It has true single-supply capability with an input voltage range extending 200 mV below the negative rail and within 1 V of the positive rail.

Rev. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

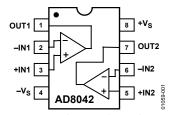

#### **CONNECTION DIAGRAM**

Figure 2. 8-Lead PDIP and 8-Lead SOIC\_N

The output voltage swing extends to within 30 mV of each rail, providing the maximum output dynamic range. Additionally, it features gain flatness of 0.1 dB to 14 MHz while offering differential gain and phase error of 0.04% and 0.06° on a single 5 V supply. This combination of features makes the AD8042 useful for professional video electronics, such as cameras, video switchers, or any high speed portable equipment. The low distortion and fast settling of the AD8042 make it ideal for buffering single-supply, high speed analog-to-digital converters (ADCs).

The AD8042 offers a low power supply current of 12 mA maximum and can run on a single 3.3 V power supply. These features are ideally suited for portable and battery-powered applications where size and power are critical.

The wide bandwidth of 160 MHz along with 200 V/ $\mu$ s of slew rate on a single 5 V supply make the AD8042 useful in many general-purpose, high speed applications where single supplies from +3.3 V to +12 V and dual power supplies of up to  $\pm 6$  V are needed. The AD8042 is available in 8-lead PDIP and 8-lead SOIC\_N packages.

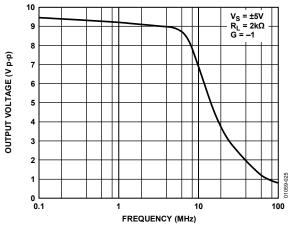

Figure 3. Frequency Response

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

## **TABLE OF CONTENTS**

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Connection Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Maximum Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ESD Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12/07—Rev. D to Rev. E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Changes to Figure 1 Caption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to Figure 1 Caption.1Changes to Table 1.3Changes to Figure 5.7Changes to Figure 20.9                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Changes to Figure 1 Caption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to Figure 1 Caption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to Figure 1 Caption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to Figure 1 Caption       1         Changes to Table 1       3         Changes to Figure 5       7         Changes to Figure 20       9         Changes to Layout and Figure 35       12         Changes to Figure 38       13         Changes to Single-Ended-to-Differential Driver Section       14         Updated Outline Dimensions       16                                                                                                                                                                          |

| Changes to Figure 1 Caption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Changes to Figure 1 Caption       1         Changes to Table 1       3         Changes to Figure 5       7         Changes to Figure 20       9         Changes to Layout and Figure 35       12         Changes to Figure 38       13         Changes to Single-Ended-to-Differential Driver Section       14         Updated Outline Dimensions       16         3/06—Rev. C to Rev. D       4         Changes to Text Prior to Table 2       4         8/04—Rev. B to Rev. C                                                     |

| Changes to Figure 1 Caption       1         Changes to Table 1       3         Changes to Figure 5       7         Changes to Figure 20       9         Changes to Layout and Figure 35       12         Changes to Figure 38       13         Changes to Single-Ended-to-Differential Driver Section       14         Updated Outline Dimensions       16         3/06—Rev. C to Rev. D         Changes to Text Prior to Table 2       4                                                                                           |

| Changes to Figure 1 Caption       1         Changes to Table 1       3         Changes to Figure 5       7         Changes to Figure 20       9         Changes to Layout and Figure 35       12         Changes to Figure 38       13         Changes to Single-Ended-to-Differential Driver Section       14         Updated Outline Dimensions       16         3/06—Rev. C to Rev. D       16         Changes to Text Prior to Table 2       4         8/04—Rev. B to Rev. C       15         Changes to Ordering Guide       5 |

| Typical Performance Characteristics | 7  |

|-------------------------------------|----|

| Applications Information            | 12 |

| Circuit Description                 | 12 |

| Driving Capacitive Loads            | 12 |

| Overdrive Recovery                  | 12 |

| Layout Considerations               | 15 |

| Outline Dimensions                  | 16 |

| Ordering Guide                      | 16 |

## **SPECIFICATIONS**

$T_{\text{A}}$  = 25°C,  $V_{\text{S}}$  = 5 V,  $R_{\text{L}}$  = 2  $k\Omega$  to 2.5 V, unless otherwise noted.

Table 1.

| Parameter                                         | Conditions                                                                        | Min         | Тур          | Max  | Unit   |

|---------------------------------------------------|-----------------------------------------------------------------------------------|-------------|--------------|------|--------|

| DYNAMIC PERFORMANCE                               |                                                                                   |             |              |      |        |

| $-3$ dB Small Signal Bandwidth, $V_0 < 0.5$ V p-p | G = +1                                                                            | 125 160     |              |      | MHz    |

| Bandwidth for 0.1 dB Flatness                     | $G=+2$ , $R_L=150~\Omega$ , $R_F=200~\Omega$                                      |             | 14           |      | MHz    |

| Slew Rate                                         | $G = -1$ , $V_{OUT} = 2 V$ step                                                   | 130         | 200          |      | V/µs   |

| Full Power Response                               | $V_0 = 2 V p-p$                                                                   |             | 30           |      | MHz    |

| Settling Time to 1%                               | $G = -1$ , $V_{OUT} = 2 V$ step                                                   |             | 26           |      | ns     |

| Settling Time to 0.1%                             |                                                                                   |             | 39           |      | ns     |

| NOISE/DISTORTION PERFORMANCE                      |                                                                                   |             |              |      |        |

| Total Harmonic Distortion                         | $f_C = 5 \text{ MHz}, V_{OUT} = 2 \text{ V p-p, G} = +2, R_L = 1 \text{ k}\Omega$ |             | -73          |      | dB     |

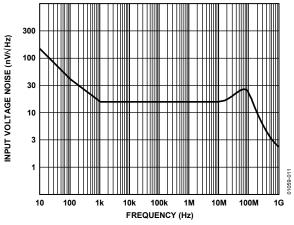

| Input Voltage Noise                               | f = 10 kHz                                                                        |             | 15           |      | nV/√Hz |

| Input Current Noise                               | f = 10 kHz                                                                        |             | 700          |      | fA/√Hz |

| Differential Gain Error (NTSC, 100 IRE)           | $G = +2$ , $R_L = 150 \Omega$ to 2.5 V                                            |             | 0.04         | 0.06 | %      |

|                                                   | $G = +2$ , $R_L = 75 \Omega$ to 2.5 V                                             |             | 0.04         |      | %      |

| Differential Phase Error (NTSC, 100 IRE)          | $G = +2$ , $R_L = 150 \Omega$ to 2.5 V                                            |             | 0.06         | 0.12 | Degree |

|                                                   | $G = +2$ , $R_L = 75 \Omega$ to 2.5 V                                             |             | 0.24         |      | Degree |

| Worst-Case Crosstalk                              | $f = 5$ MHz, $R_L = 150$ Ω to 2.5 V                                               |             | -63          |      | dB     |

| DC PERFORMANCE                                    |                                                                                   |             |              |      |        |

| Input Offset Voltage                              |                                                                                   |             | 3            | 9    | mV     |

|                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                              |             |              | 12   | mV     |

| Offset Drift                                      |                                                                                   |             | 12           |      | μV/°C  |

| Input Bias Current                                |                                                                                   |             | 1.2          | 3.2  | μΑ     |

|                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                              |             |              | 4.8  | μΑ     |

| Input Offset Current                              |                                                                                   |             | 0.2          | 0.5  | μΑ     |

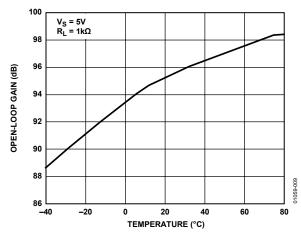

| Open-Loop Gain                                    | $R_L = 1 \text{ k}\Omega$                                                         | 90          | 100          |      | dB     |

|                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                              |             | 90           |      | dB     |

| INPUT CHARACTERISTICS                             |                                                                                   |             |              |      |        |

| Input Resistance                                  |                                                                                   |             | 300          |      | kΩ     |

| Input Capacitance                                 |                                                                                   |             | 1.5          |      | рF     |

| Input Common-Mode Voltage Range                   |                                                                                   |             | -0.2 to +4   |      | V      |

| Common-Mode Rejection Ratio                       | $V_{CM} = 0 \text{ V to } 3.5 \text{ V}$                                          | 68          | 74           |      | dB     |

| OUTPUT CHARACTERISTICS                            |                                                                                   |             |              |      |        |

| Output Voltage Swing                              | $R_L = 10 \text{ k}\Omega \text{ to } 2.5 \text{ V}$                              |             | 0.03 to 4.97 |      | V      |

|                                                   | $R_L = 1 \text{ k}\Omega \text{ to } 2.5 \text{ V}$                               | 0.10 to 4.9 | 0.05 to 4.95 |      | V      |

|                                                   | $R_L = 50 \Omega$ to 2.5 V                                                        | 0.4 to 4.4  | 0.36 to 4.45 |      | V      |

| Output Current                                    | $T_{MIN}$ to $T_{MAX}$ , $V_{OUT} = 0.5 \text{ V}$ to $4.5 \text{ V}$             |             | 50           |      | mA     |

| Short-Circuit Current                             | Sourcing                                                                          |             | 90           |      | mA     |

|                                                   | Sinking                                                                           |             | 100          |      | mA     |

| Capacitive Load Drive                             | G = +1                                                                            |             | 20           |      | pF     |

| POWER SUPPLY                                      |                                                                                   |             |              |      |        |

| Operating Range                                   |                                                                                   | 3           |              | 12   | V      |

| Quiescent Current (Per Amplifier)                 |                                                                                   |             | 5.5          | 6.4  | mA     |

| Power Supply Rejection Ratio                      | $V_{S-} = 0 \text{ V to } -1 \text{ V, or } V_{S+} = 5 \text{ V to } 6 \text{ V}$ | 72          | 80           |      | dB     |

| OPERATING TEMPERATURE RANGE                       |                                                                                   | -40         |              | +85  | °C     |

$T_{\text{A}}$  = 25°C,  $V_{\text{S}}$  = 3 V,  $R_{\text{L}}$  = 2  $k\Omega$  to 1.5 V, unless otherwise noted.

Table 2.

| Parameter                                         | Conditions                                                                        | Min        | Тур          | Max | Unit    |

|---------------------------------------------------|-----------------------------------------------------------------------------------|------------|--------------|-----|---------|

| DYNAMIC PERFORMANCE                               |                                                                                   |            |              |     |         |

| $-3$ dB Small Signal Bandwidth, $V_0 < 0.5$ V p-p | G = +1                                                                            | 120        | 140          |     | MHz     |

| Bandwidth for 0.1 dB Flatness                     | $G = +2$ , $R_L = 150 \Omega$ , $R_F = 200 \Omega$                                |            | 11           |     | MHz     |

| Slew Rate                                         | $G = -1$ , $V_{OUT} = 2 V$ step                                                   | 120        | 170          |     | V/µs    |

| Full Power Response                               | $V_0 = 2 V p-p$                                                                   |            | 25           |     | MHz     |

| Settling Time to 1%                               | $G = -1$ , $V_{OUT} = 1 \text{ V step}$                                           |            | 30           |     | ns      |

| Settling Time to 0.1%                             |                                                                                   |            | 45           |     | ns      |

| NOISE/DISTORTION PERFORMANCE                      |                                                                                   |            |              |     |         |

| Total Harmonic Distortion                         | $f_C = 5 \text{ MHz}, V_{OUT} = 2 \text{ V p-p}, G = -1, R_L = 100 \Omega$        |            | -56          |     | dB      |

| Input Voltage Noise                               | f = 10 kHz                                                                        |            | 16           |     | nV/√Hz  |

| Input Current Noise                               | f = 10 kHz                                                                        |            | 500          |     | fA/√Hz  |

| Differential Gain Error (NTSC, 100 IRE)           | $G = +2$ , $R_L = 150 \Omega$ to 1.5 V, Input $V_{CM} = 1 \text{ V}$              |            | 0.10         |     | %       |

|                                                   | $R_L = 75 \Omega$ to 1.5 V, Input $V_{CM} = 1 \text{ V}$                          |            | 0.10         |     | %       |

| Differential Phase Error (NTSC, 100 IRE)          | $G = +2$ , $R_L = 150 \Omega$ to 1.5 V, Input $V_{CM} = 1 \text{ V}$              |            | 0.12         |     | Degrees |

|                                                   | $R_L = 75 \Omega$ to 1.5 V, Input $V_{CM} = 1 \text{ V}$                          |            | 0.27         |     | Degrees |

| Worst-Case Crosstalk                              | $f = 5 \text{ MHz}, R_L = 1 \text{ k}\Omega \text{ to } 1.5 \text{ V}$            |            | -68          |     | dB      |

| DC PERFORMANCE                                    |                                                                                   |            |              |     |         |

| Input Offset Voltage                              |                                                                                   |            | 3            | 9   | mV      |

| •                                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                                              |            |              | 12  | mV      |

| Offset Drift                                      |                                                                                   |            | 12           |     | μV/°C   |

| Input Bias Current                                |                                                                                   |            | 1.2          | 3.2 | μA      |

| •                                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                                              |            |              | 4.8 | μΑ      |

| Input Offset Current                              |                                                                                   |            | 0.2          | 0.6 | μΑ      |

| Open-Loop Gain                                    | $R_{I} = 1 k\Omega$                                                               | 90         | 100          |     | dB      |

| •                                                 | T <sub>MIN</sub> to T <sub>MAX</sub>                                              |            | 90           |     | dB      |

| INPUT CHARACTERISTICS                             |                                                                                   |            |              |     |         |

| Input Resistance                                  |                                                                                   |            | 300          |     | kΩ      |

| Input Capacitance                                 |                                                                                   |            | 1.5          |     | рF      |

| Input Common-Mode Voltage Range                   |                                                                                   |            | -0.2 to +2   |     | V       |

| Common-Mode Rejection Ratio                       | $V_{CM} = 0 \text{ V to } 1.5 \text{ V}$                                          | 66         | 74           |     | dB      |

| OUTPUT CHARACTERISTICS                            |                                                                                   |            |              |     |         |

| Output Voltage Swing                              | $R_L = 10 \text{ k}\Omega \text{ to } 1.5 \text{ V}$                              |            | 0.03 to 2.97 |     | V       |

| , 3                                               | $R_L = 1 \text{ k}\Omega \text{ to } 1.5 \text{ V}$                               | 0.1 to 2.9 | 0.05 to 2.95 |     | V       |

|                                                   | $R_L = 50 \Omega$ to 1.5 V                                                        | 0.3 to 2.6 | 0.25 to 2.65 |     | V       |

| Output Current                                    | $T_{MIN}$ to $T_{MAX}$ , $V_{OUT} = 0.5 \text{ V}$ to $2.5 \text{ V}$             |            | 50           |     | mA      |

| Short-Circuit Current                             | Sourcing                                                                          |            | 50           |     | mA      |

|                                                   | Sinking                                                                           |            | 70           |     | mA      |

| Capacitive Load Drive                             | G = +1                                                                            |            | 17           |     | рF      |

| POWER SUPPLY                                      |                                                                                   |            |              |     |         |

| Operating Range                                   |                                                                                   | 3          |              | 12  | V       |

| Quiescent Current (Per Amplifier)                 |                                                                                   | -          | 5.5          | 6.4 | mA      |

| Power Supply Rejection Ratio                      | $V_{S-} = 0 \text{ V to } -1 \text{ V, or } V_{S+} = 3 \text{ V to } 4 \text{ V}$ | 68         | 80           |     | dB      |

| OPERATING TEMPERATURE RANGE                       | 2 2 2 2 2 3 7 2 2 3 7 2 3 7 3 7 3 7 3 7                                           | 0          |              | 70  | °C      |

$T_A$  = 25°C,  $V_S$  = ±5 V,  $R_L$  = 2  $k\Omega$  to 0 V, unless otherwise noted.

Table 3.

| Parameter                                         | Conditions                                                                         | Min          | Тур            | Max  | Unit    |

|---------------------------------------------------|------------------------------------------------------------------------------------|--------------|----------------|------|---------|

| DYNAMIC PERFORMANCE                               |                                                                                    |              |                |      |         |

| $-3$ dB Small Signal Bandwidth, $V_0 < 0.5$ V p-p | G = +1                                                                             | 125          | 170            |      | MHz     |

| Bandwidth for 0.1 dB Flatness                     | $G=+2$ , $R_L=150~\Omega$ , $R_F=200~\Omega$                                       |              | 18             |      | MHz     |

| Slew Rate                                         | $G = -1$ , $V_{OUT} = 2 V$ step                                                    | 145          | 225            |      | V/µs    |

| Full Power Response                               | $V_0 = 2 V p-p$                                                                    |              | 35             |      | MHz     |

| Settling Time to 1%                               | $G = -1$ , $V_{OUT} = 2 V$ step                                                    |              | 22             |      | ns      |

| Settling Time to 0.1%                             |                                                                                    |              | 32             |      | ns      |

| NOISE/DISTORTION PERFORMANCE                      |                                                                                    |              |                |      |         |

| Total Harmonic Distortion                         | $f_C = 5 \text{ MHz}, V_O = 2 \text{ V p-p}, G = +2, R_L = 1 \text{ k}\Omega$      |              | -78            |      | dB      |

| Input Voltage Noise                               | f = 10 kHz                                                                         |              | 15             |      | nV/√Hz  |

| Input Current Noise                               | f = 10 kHz                                                                         |              | 700            |      | fA/√Hz  |

| Differential Gain Error (NTSC, 100 IRE)           | $G = +2$ , $R_L = 150 \Omega$                                                      |              | 0.02           | 0.05 | %       |

|                                                   | $G = +2$ , $R_L = 75 \Omega$                                                       |              | 0.02           |      | %       |

| Differential Phase Error (NTSC, 100 IRE)          | $G = +2$ , $R_L = 150 \Omega$                                                      |              | 0.04           | 0.10 | Degrees |

|                                                   | $G = +2$ , $R_L = 75 \Omega$                                                       |              | 0.12           |      | Degrees |

| Worst-Case Crosstalk                              | $f = 5 \text{ MHz}, R_L = 150 \Omega$                                              |              | -63            |      | dB      |

| DC PERFORMANCE                                    |                                                                                    |              |                |      |         |

| Input Offset Voltage                              |                                                                                    |              | 3              | 9.8  | mV      |

|                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                               |              |                | 14   | mV      |

| Offset Drift                                      |                                                                                    |              | 12             |      | μV/°C   |

| Input Bias Current                                |                                                                                    |              | 1.2            | 3.2  | μΑ      |

|                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                               |              |                | 4.8  | μΑ      |

| Input Offset Current                              |                                                                                    |              | 0.2            | 0.6  | μΑ      |

| Open-Loop Gain                                    | $R_L = 1 \text{ k}\Omega$                                                          | 90           | 94             |      | dB      |

|                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                               |              | 86             |      | dB      |

| INPUT CHARACTERISTICS                             |                                                                                    |              |                |      |         |

| Input Resistance                                  |                                                                                    |              | 300            |      | kΩ      |

| Input Capacitance                                 |                                                                                    |              | 1.5            |      | pF      |

| Input Common-Mode Voltage Range                   |                                                                                    |              | -5.2 to +4     |      | V       |

| Common-Mode Rejection Ratio                       | $V_{CM} = -5 \text{ V to } +3.5 \text{ V}$                                         | 66           | 74             |      | dB      |

| OUTPUT CHARACTERISTICS                            |                                                                                    |              |                |      |         |

| Output Voltage Swing                              | $R_L = 10 \text{ k}\Omega$                                                         |              | -4.97 to +4.97 |      | ٧       |

|                                                   | $R_L = 1 \text{ k}\Omega$                                                          | -4.8 to +4.8 | -4.9 to +4.9   |      | V       |

|                                                   | $R_L = 50 \Omega$                                                                  | -4 to +3.2   | -4.2 to +3.5   |      | V       |

| Output Current                                    | $T_{MIN}$ to $T_{MAX}$ , $V_{OUT} = -4.5 \text{ V}$ to $+4.5 \text{ V}$            |              | 50             |      | mA      |

| Short-Circuit Current                             | Sourcing                                                                           |              | 100            |      | mA      |

|                                                   | Sinking                                                                            |              | 100            |      | mA      |

| Capacitive Load Drive                             | G = +1                                                                             |              | 25             |      | pF      |

| POWER SUPPLY                                      |                                                                                    |              |                |      |         |

| Operating Range                                   |                                                                                    | 3            |                | 12   | ٧       |

| Quiescent Current (Per Amplifier)                 |                                                                                    |              | 6              | 7    | mA      |

| Power Supply Rejection Ratio                      | $V_{S-} = -5 \text{ V to } -6 \text{ V, or } V_{S+} = 5 \text{ V to } 6 \text{ V}$ | 68           | 80             |      | dB      |

| OPERATING TEMPERATURE RANGE                       |                                                                                    | -40          |                | +85  | °C      |

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                            | Rating                           |

|--------------------------------------|----------------------------------|

| Supply Voltage                       | 12.6 V                           |

| Internal Power Dissipation1          |                                  |

| 8-Lead PDIP (N)                      | 1.3 W                            |

| 8-Lead SOIC_N (R)                    | 0.9 W                            |

| Input Voltage (Common Mode)          | $\pm V_{S} \pm 0.5 V$            |

| Differential Input Voltage           | ±3.4 V                           |

| Output Short-Circuit Duration        | Observe Power<br>Derating Curves |

| Storage Temperature Range (N, R)     | −65°C to +125°C                  |

| Lead Temperature (Soldering, 10 sec) | 300°C                            |

$<sup>^{1}</sup>$  Specification is for the device in free air: 8-Lead PDIP:  $\theta_{JA} = 90^{\circ}\text{C/W}$ 8-Lead SOIC\_N:  $\theta_{JA} = 155^{\circ}\text{C/W}$ .

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

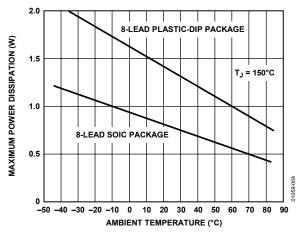

### **MAXIMUM POWER DISSIPATION**

The maximum power that can be safely dissipated by the AD8042 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Exceeding this limit temporarily can cause a shift in parametric performance due to a change in the stresses exerted on the die by the package.

Exceeding a junction temperature of 175°C for an extended period can result in device failure.

While the AD8042 is internally short-circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves.

Figure 4. Maximum Power Dissipation vs. Temperature

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### TYPICAL PERFORMANCE CHARACTERISTICS

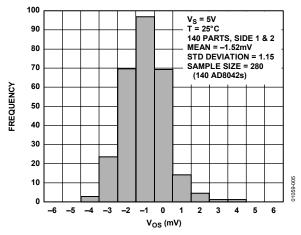

Figure 5. Typical Distribution of Vos

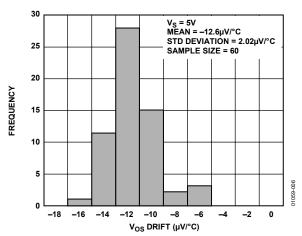

Figure 6. Vos Drift Over −40°C to +85°C

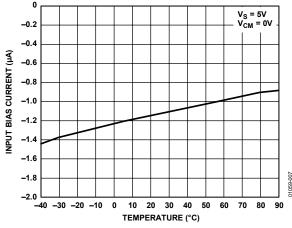

Figure 7. I<sub>B</sub> vs. Temperature

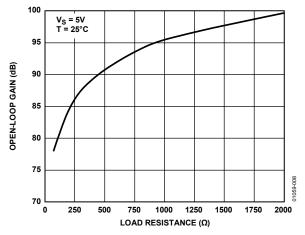

Figure 8. Open-Loop Gain vs. R<sub>L</sub> to 2.5 V

Figure 9. Open-Loop Gain vs. Temperature

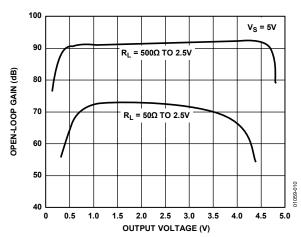

Figure 10. Open-Loop Gain vs. Output Voltage

Figure 11. Input Voltage Noise vs. Frequency

Figure 12. Total Harmonic Distortion vs. Frequency

Figure 13. Worst Harmonic vs. Output Voltage

Figure 14. Differential Gain and Phase Errors

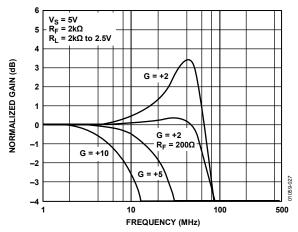

Figure 15. 0.1 dB Gain Flatness

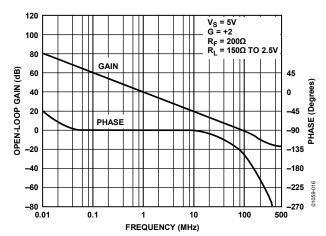

Figure 16. Open-Loop Gain and Phase vs. Frequency

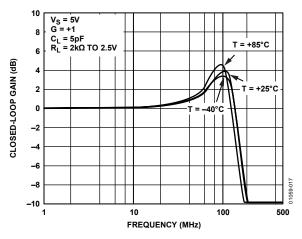

Figure 17. Closed-Loop Frequency Response vs. Temperature

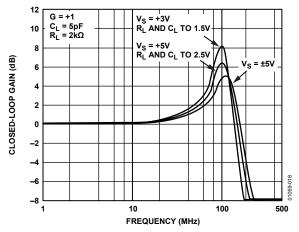

Figure 18. Closed-Loop Frequency Response vs. Supply

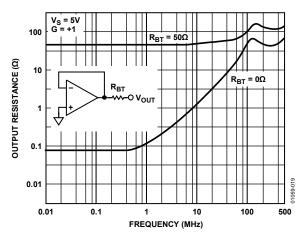

Figure 19. Output Resistance vs. Frequency

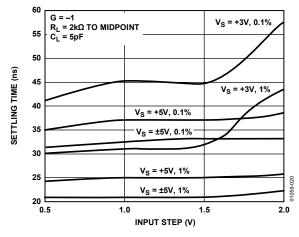

Figure 20. Settling Time vs. Input Voltage

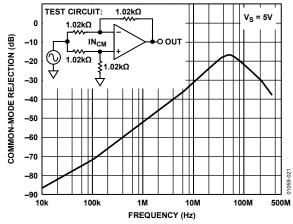

Figure 21. Common-Mode Rejection vs. Frequency

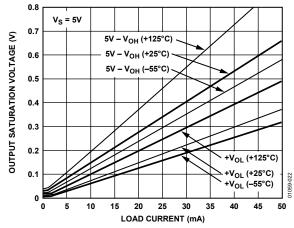

Figure 22. Output Saturation Voltage vs. Load Current

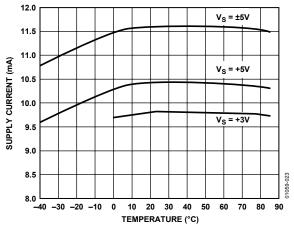

Figure 23. Supply Current vs. Temperature

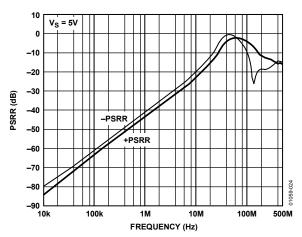

Figure 24. PSRR vs. Frequency

Figure 25. Output Voltage vs. Frequency

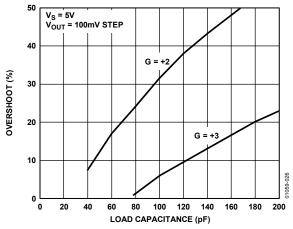

Figure 26. Overshoot vs. Load Capacitance

Figure 27. Closed-Loop Gain vs. Frequency Response

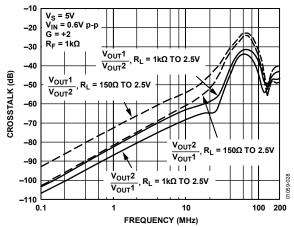

Figure 28. Crosstalk (Output-to-Output) vs. Frequency

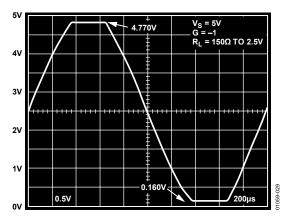

Figure 29. Output Swing with Load Reference to Supply Midpoint

Figure 30. Output Swing with Load Reference to Negative to Supply

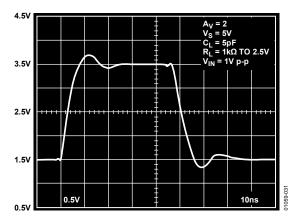

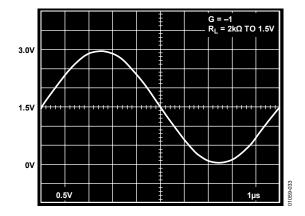

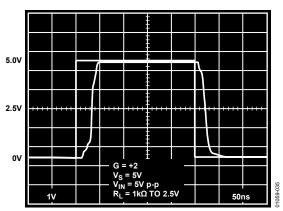

Figure 31. 1 V Pulse Response,  $V_S = 5 V$

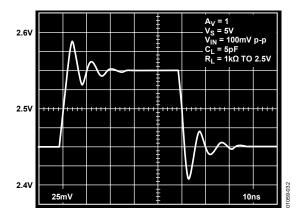

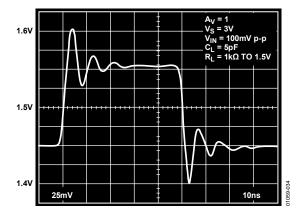

Figure 32. 100 mV Pulse Response,  $V_S = 5 V$

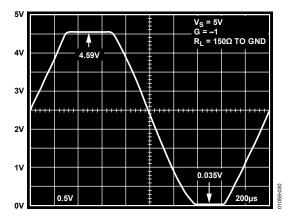

Figure 33. Rail-to-Rail Output Swing,  $V_S = 3 V$

Figure 34. 100 mV Pulse Response,  $V_S = 3 \text{ V}$

### APPLICATIONS INFORMATION

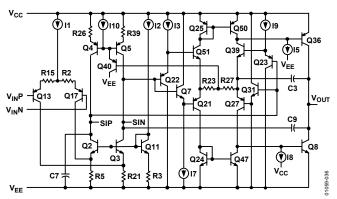

### **CIRCUIT DESCRIPTION**

The AD8042 is fabricated on the Analog Devices, Inc., proprietary eXtra-Fast Complementary Bipolar (XFCB) process, which enables the construction of PNP and NPN transistors with similar  $f_i$ s in the 2 GHz to 4 GHz region. The process is dielectrically isolated to eliminate the parasitic and latch-up problems caused by junction isolation. These features allow the construction of high frequency, low distortion amplifiers with low supply currents. This design uses a differential output input stage to maximize bandwidth and headroom (see Figure 35). The smaller signal swings required on the first stage outputs (nodes SIP, SIN) reduce the effect of nonlinear currents due to junction capacitances and improve the distortion performance. With this design, harmonic distortion of better than -77 dB @ 1 MHz into  $100 \Omega$  with  $V_{OUT} = 2 V$  p-p (gain = +2) on a single 5 V supply is achieved.

Figure 35. Simplified Schematic

The rail-to-rail output range of the AD8042 is provided by a complementary common-emitter output stage. High output drive capability is provided by injecting all output stage predriver currents directly into the bases of the output devices Q8 and Q36. Biasing of Q8 and Q36 is accomplished by I8 and I5, along with a common-mode feedback loop (not shown). This circuit topology allows the AD8042 to drive 40 mA of output current with the outputs within 0.5 V of the supply rails.

On the input side, the device can handle voltages from 0.2 V below the negative rail to within 1.2 V of the positive rail. Exceeding these values does not cause phase reversal; however, the input ESD devices do begin to conduct if the input voltages exceed the rails by greater than 0.5 V.

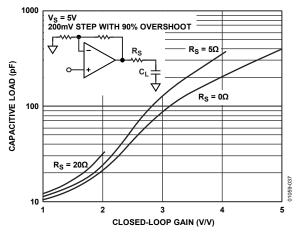

#### **DRIVING CAPACITIVE LOADS**

The capacitive load drive of the AD8042 can be increased by adding a low valued resistor in series with the load. Figure 36 shows the effects of a series resistor on capacitive drive for varying voltage gains. As the closed-loop gain is increased, the larger phase margin allows for larger capacitive loads with less overshoot. Adding a series resistor with lower closed-loop gains accomplishes the same effect. For large capacitive loads, the frequency response of the amplifier is dominated by the roll-off of the series resistor and capacitive load.

Figure 36. Capacitive Load Drive vs. Closed-Loop Gain

### **OVERDRIVE RECOVERY**

Overdrive of an amplifier occurs when the output and/or input range are exceeded. The amplifier must recover from this overdrive condition. As shown in Figure 37, the AD8042 recovers within 30 ns from negative overdrive and within 25 ns from positive overdrive.

Figure 37. Overdrive Recovery

### Single-Supply Composite Video Line Driver

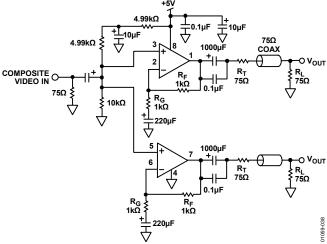

The two op amps of an AD8042 can be configured as a single-supply dual line driver for composite video. The wide signal swing of the AD8042 enables this function to be performed without using any type of clamping or dc restore circuit, which can cause signal distortion.

Figure 38 shows a schematic for a circuit that is driven by a single composite video source that is ac-coupled, level-shifted and applied to both noninverting inputs of the two amplifiers. Each op amp provides a separate 75  $\Omega$  composite video output. To obtain single-supply operation, ac coupling is used throughout. The large capacitor values are required to ensure that there is minimal tilting of the video signals due to their low frequency (30 Hz) signal content. The circuit shown was measured to have a differential gain of 0.06% and a differential phase of 0.06°.

The input is terminated in 75  $\Omega$  and ac-coupled via  $C_{\rm IN}$  to a voltage divider that provides the dc bias point to the input. Setting the optimal bias point requires some understanding of the nature of composite video signals and the video performance of the AD8042.

Figure 38. Single-Supply Composite Video Line Driver Using AD8042

Signals of bounded peak-to-peak amplitude that vary in duty cycle require larger dynamic swing capability than their peak-to-peak amplitude after ac coupling. As a worst case, the dynamic signal swing required approaches twice the peak-to-peak value. The two bounding cases are for a duty cycle that is mostly low, but occasionally goes high at a fraction of a percent duty cycle, and vice versa.

Composite video is not quite this demanding. One bounding extreme is for a signal that is mostly black for an entire frame but has a white (full intensity), minimum width spike at least once per frame.

The other extreme is for a video signal that is full white everywhere. The blanking intervals and sync tips of such a signal have negative going excursions in compliance with composite video specifications. The combination of horizontal and vertical blanking intervals limit such a signal to being at its highest level (white) for only about 75% of the time.

As a result of the duty cycle variations between the two extremes presented, a 1 V p-p composite video signal that is multiplied by a gain of 2 requires about 3.2 V p-p of dynamic voltage swing at the output for an op amp to pass a composite video signal of arbitrary duty cycle without distortion.

Some circuits use a sync tip clamp along with ac coupling to hold the sync tips at a relatively constant level, which lowers the amount of dynamic signal swing required. However, these circuits can have artifacts, such as sync tip compression, unless they are driven by sources with very low output impedance.

The AD8042 not only has ample signal swing capability to handle the dynamic range required without using a sync tip clamp but also has good video specifications such as differential gain and differential phase when buffering these signals in an ac-coupled configuration.

To test the dynamic range, the differential gain and differential phase were measured for the AD8042 while the supplies were varied. As the lower supply is raised to approach the video signal, the first effect observed is that the sync tips become compressed before the differential gain and differential phase are adversely affected. Therefore, there must be adequate swing in the negative direction to pass the sync tips without compression.

As the upper supply is lowered to approach the video, the differential gain and differential phase was not significantly affected until the difference between the peak video output and the supply reached 0.6 V. Therefore, the highest video level should be kept at least 0.6 V below the positive supply rail.

Therefore, it was found that the optimal point to bias the noninverting input is at 2.2 V dc. Operating at this point, the worst-case differential gain is measured at 0.06% and the worst-case differential phase is 0.06°.

The ac-coupling capacitors used in the circuit at first glance appear quite large. A composite video signal has a lower frequency band edge of 30 Hz. The resistances at the various ac coupling points, especially at the output, are quite small. To minimize phase shifts and baseline tilt, the large value capacitors are required. For video system performance that is not to be of the highest quality, the value of these capacitors can be reduced by a factor of up to five with only a slightly observable change in the picture quality.

### Single-Ended-to-Differential Driver

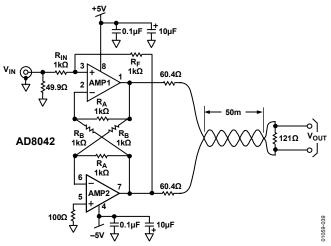

Using a cross-coupled, single-ended-to-differential converter (SEDC), the AD8042 makes a good general-purpose differential line driver. This SEDC can be used for applications such as driving Category-5 (CAT-5) twisted pair wires. Figure 39 shows a configuration for a circuit that performs this function that can be used for video transmission over a differential pair or various data communication purposes.

Figure 39. Single-Ended-to-Differential Twisted Pair Line Driver

Each of the op amps of the AD8042 is configured as a unity gain follower by the feedback resistors ( $R_A$ ). Each op amp output also drives the other as a unity gain inverter via  $R_B$ , creating a totally symmetrical circuit.

If the noninverting input of AMP2 is grounded and a small positive signal is applied to the noninverting input of AMP1, the output of AMP1 is driven to saturation in the positive direction and the input of AMP2 is driven to saturation in the negative direction. This is similar to the way a conventional op amp behaves without any feedback.

If a resistor ( $R_{\rm F}$ ) is connected from the output of AMP2 to the noninverting input of AMP1, negative feedback is provided, which closes the loop. An input resistor ( $R_{\rm IN}$ ) makes the circuit look like a conventional inverting op amp configuration with differential outputs.

The gain of this circuit from input to either output is  $\pm R_F/R_{IN}$ , or the single-ended-to-differential gain is  $2 \times R_F/R_{IN}$ . This gives the circuit the advantage of being able to adjust its gain by changing a single resistor.

The cable has a characteristic impedance of about 120  $\Omega$ . Each driver output is back terminated with a pair of 60.4  $\Omega$  resistors to make the source look like 120  $\Omega$ . The receive end is terminated with 121  $\Omega$ , and the signal is measured differentially with a pair of scope probes. One channel on the oscilloscope is inverted and then the signals are added.

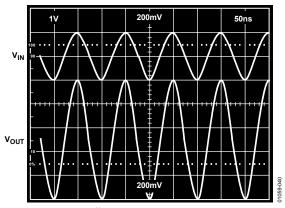

Figure 40 shows the results of the circuit in Figure 39 driving 50 meters of CAT-5 cable.

Figure 40. Differential Driver Frequency Response

### Single-Supply Differential A/D Driver

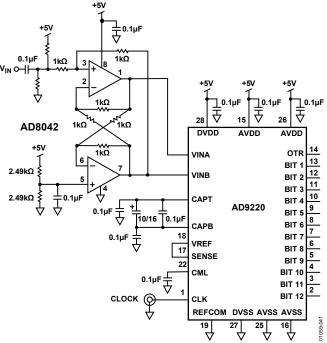

The single-ended-to-differential converter circuit is also useful as a differential driver for video speed, single-ended, differential input ADCs. Figure 41 is a schematic that shows such a circuit differentially driving an AD9220, a 12-bit, 10 MSPS ADC.

Figure 41. AD8042 Differential Driver for the AD9220 12-Bit, 10 MSPS ADC

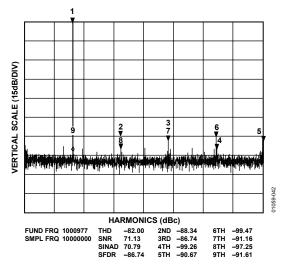

The circuit was tested with a 1 MHz input signal and clocked at 10 MHz. An FFT response of the digital output is shown in Figure 42.

Pin 5 is biased at 2.5 V by the voltage divider and bypassed. This biases each output at 2.5 V.  $V_{\rm IN}$  is ac-coupled such that  $V_{\rm IN}$  going positive makes VINA go positive and VINB go in the negative direction. The opposite happens for a negative going  $V_{\rm IN}$ .

Figure 42. FFT of the AD9220 Output When Driven by the AD8042

### **HDSL Line Driver**

High bit rate digital subscriber line (HDSL) is a popular means of providing data communication at DS1 rates (1.544 Mbps) over moderate distances via conventional telephone twisted pair wires. In these systems, the transceiver at the customer's end is powered sometimes via the twisted pair from a power source at the central office. Sometimes, it is required to raise the dc voltage of the power source to compensate for IR drops in long lines or lines with narrow gauge wires.

Because of the IR drop, it is highly desirable to keep the power consumption of the customer's transceiver as low as possible. One means to realize significant power savings is to run the transceiver from a  $\pm 5$  V supply instead of the more conventional  $\pm 12$  V.

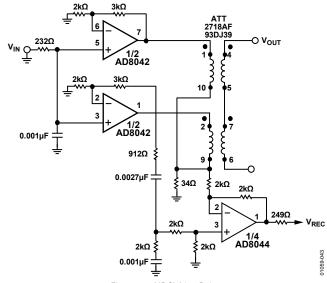

The high output swing and current drive capability of the AD8042 make it ideally suited to this application. Figure 43 shows a circuit for the analog portion of an HDSL transceiver using the AD8042 as the line driver.

Figure 43. HDSL Line Driver

### LAYOUT CONSIDERATIONS

The specified high speed performance of the AD8042 requires careful attention to board layout and component selection. Proper RF design techniques and low-pass parasitic component selection are necessary.

The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low impedance path. The ground plane should be removed from the area near the input pins to reduce the stray capacitance.

Chip capacitors should be used for the supply bypassing. One end should be connected to the ground plane and the other within ½-inch of each power pin. An additional large (0.47  $\mu F$  to 10  $\mu F$ ) tantalum electrolytic capacitor should be connected in parallel, but not necessarily so close to supply current, for fast, large signal changes at the output.

The feedback resistor should be located close to the inverting input pin to keep the stray capacitance at this node to a minimum. Capacitance variations of less than 1 pF at the inverting input significantly affect high speed performance.

Stripline design techniques should be used for long signal traces (greater than approximately one inch). These should be designed with a characteristic impedance of 50  $\Omega$  or 75  $\Omega$  and be properly terminated at each end.

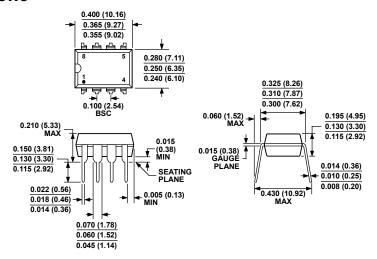

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 44. 8-Lead Plastic Dual In-Line Package [PDIP] Narrow Body (N-8)—Dimensions shown in inches and (millimeters)

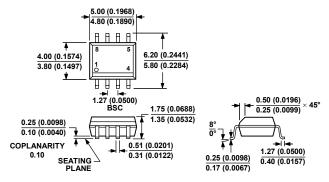

COMPLIANT TO JEDEC STANDARDS MS-012-A A

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 45. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)—Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description     | Package Option |

|------------------------------|-------------------|-------------------------|----------------|

| AD8042AN                     | -40°C to +85°C    | 8-Lead PDIP             | N-8            |

| AD8042AR                     | -40°C to +85°C    | 8-Lead SOIC_N           | R-8            |

| AD8042AR-REEL                | -40°C to +85°C    | 8-Lead SOIC_N, 13" Reel | R-8            |

| AD8042AR-REEL7               | -40°C to +85°C    | 8-Lead SOIC_N, 7" Reel  | R-8            |

| AD8042ARZ <sup>1</sup>       | -40°C to +85°C    | 8-Lead SOIC_N           | R-8            |

| AD8042ARZ-REEL <sup>1</sup>  | -40°C to +85°C    | 8-Lead SOIC_N, 13" Reel | R-8            |

| AD8042ARZ-REEL7 <sup>1</sup> | -40°C to +85°C    | 8-Lead SOIC_N, 7" Reel  | R-8            |

| AD8042ACHIPS                 |                   | DIE                     |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.