| Part No.: | LTC2232 |

| Page: | 28 Pages |

| Size: | 752 KB |

| Manufacturer: | Linear Technology |

| Logo: |  |

| Views: | 2 |

| Update Time: | 2023-11-15 17:18:34 |

| DataSheet: | Download |

| Part No. | Packing | SPQ | Marking | MSL | Pins | Temp Range | Package Description | Buy |

| LTC2232CUK#PBF | Tube | 52 | LTC2232UK | 1 | 48 | 0°C ~ 70°C | 48-Lead QFN (7mm x 7mm x 0.75mm) | |

| LTC2232CUK#TRPBF | Reel | 2000 | LTC2232UK | 1 | 48 | 0°C ~ 70°C | 48-Lead QFN (7mm x 7mm x 0.75mm) | |

| LTC2232CUK#TRMPBF | Reel | 500 | LTC2232UK | 1 | 48 | 0°C ~ 70°C | 48-Lead QFN (7mm x 7mm x 0.75mm) | |

| LTC2232IUK#PBF | Tube | 52 | LTC2232UK | 1 | 48 | -40°C ~ 85°C | 48-Lead QFN (7mm x 7mm x 0.75mm) | |

| LTC2232IUK#TRPBF | Reel | 2000 | LTC2232UK | 1 | 48 | -40°C ~ 85°C | 48-Lead QFN (7mm x 7mm x 0.75mm) | |

| LTC2232IUK#TRMPBF | Reel | 500 | LTC2232UK | 1 | 48 | -40°C ~ 85°C | 48-Lead QFN (7mm x 7mm x 0.75mm) |

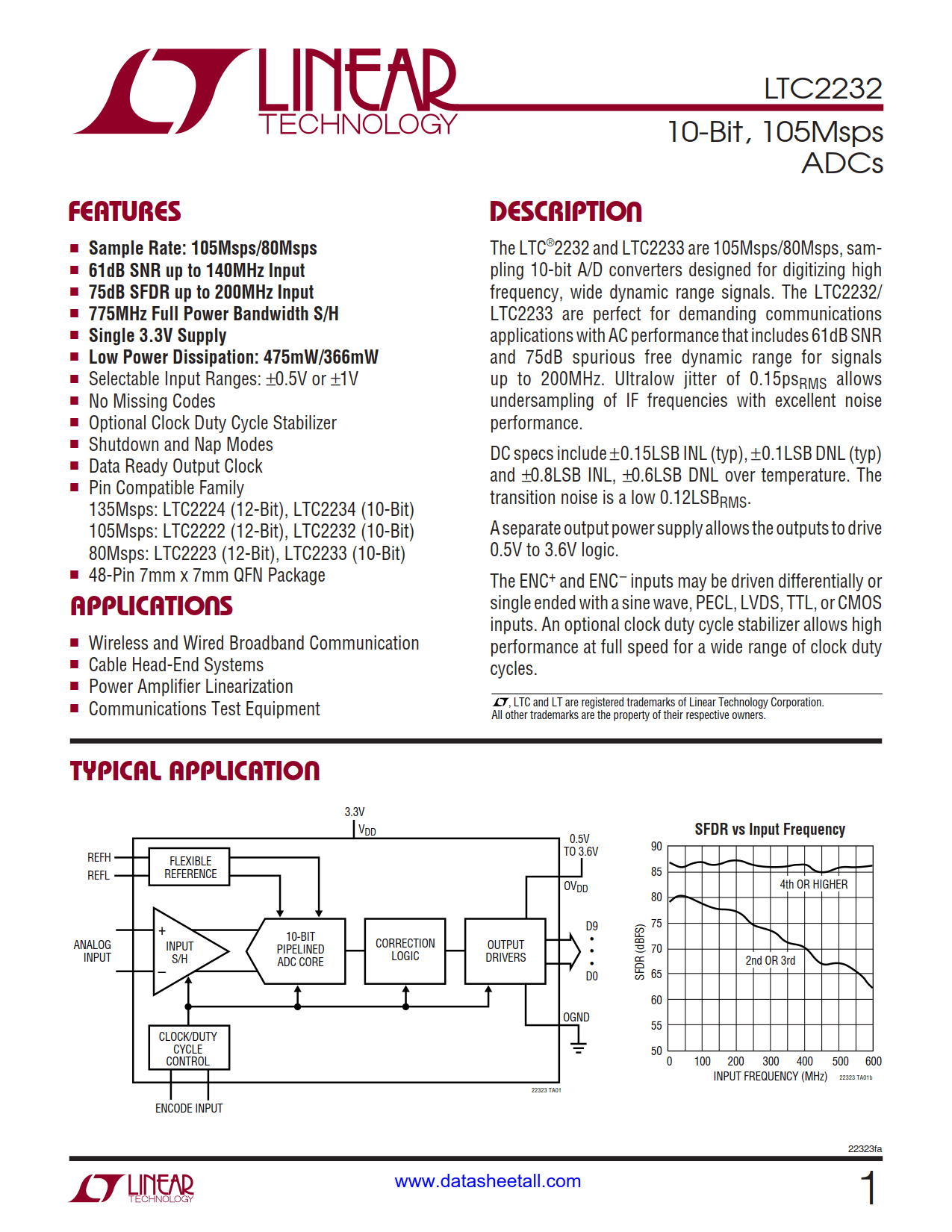

The LTC2232 are 105Msps, sampling 10-bit A/D converters designed for digitizing high frequency, wide dynamic range signals. The LTC2232 are perfect for demanding communications applications with AC performance that includes 61dB SNR and 75dB spurious free dynamic range for signals up to 200MHz. Ultralow jitter of 0.15psRMS allows undersampling of IF frequencies with excellent noise performance.

DC specs include ±0.15LSB INL (typ), ±0.1LSB DNL (typ) and ±0.8LSB INL, ±0.6LSB DNL over temperature. The transition noise is a low 0.12LSBRMS.

A separate output power supply allows the outputs to drive 0.5V to 3.6V logic.

The ENC+ and ENC– inputs may be driven differentially or single ended with a sine wave, PECL, LVDS, TTL, or CMOS inputs. An optional clock duty cycle stabilizer allows high performance at full speed for a wide range of clock duty cycles.