| Part No.: | AD9763 |

| Page: | 44 Pages |

| Size: | 568 KB |

| Manufacturer: | Analog Devices, Inc. |

| Logo: |  |

| Views: | 2 |

| Update Time: | 2024-12-04 11:28:33 |

| DataSheet: | Download |

| Part No. | Packing | SPQ | Marking | MSL | Pins | Temp Range | Package Description | Buy |

| AD9763ASTZ | Tray | 250 | 9763ASTZ | 3 | 48 | -40°C ~ 85°C | 48-Lead Low Profile Quad Flat Package [LQFP] | |

| AD9763ASTZRL | Reel | 2000 | 9763ASTZ | 3 | 48 | -40°C ~ 85°C | 48-Lead Low Profile Quad Flat Package [LQFP] |

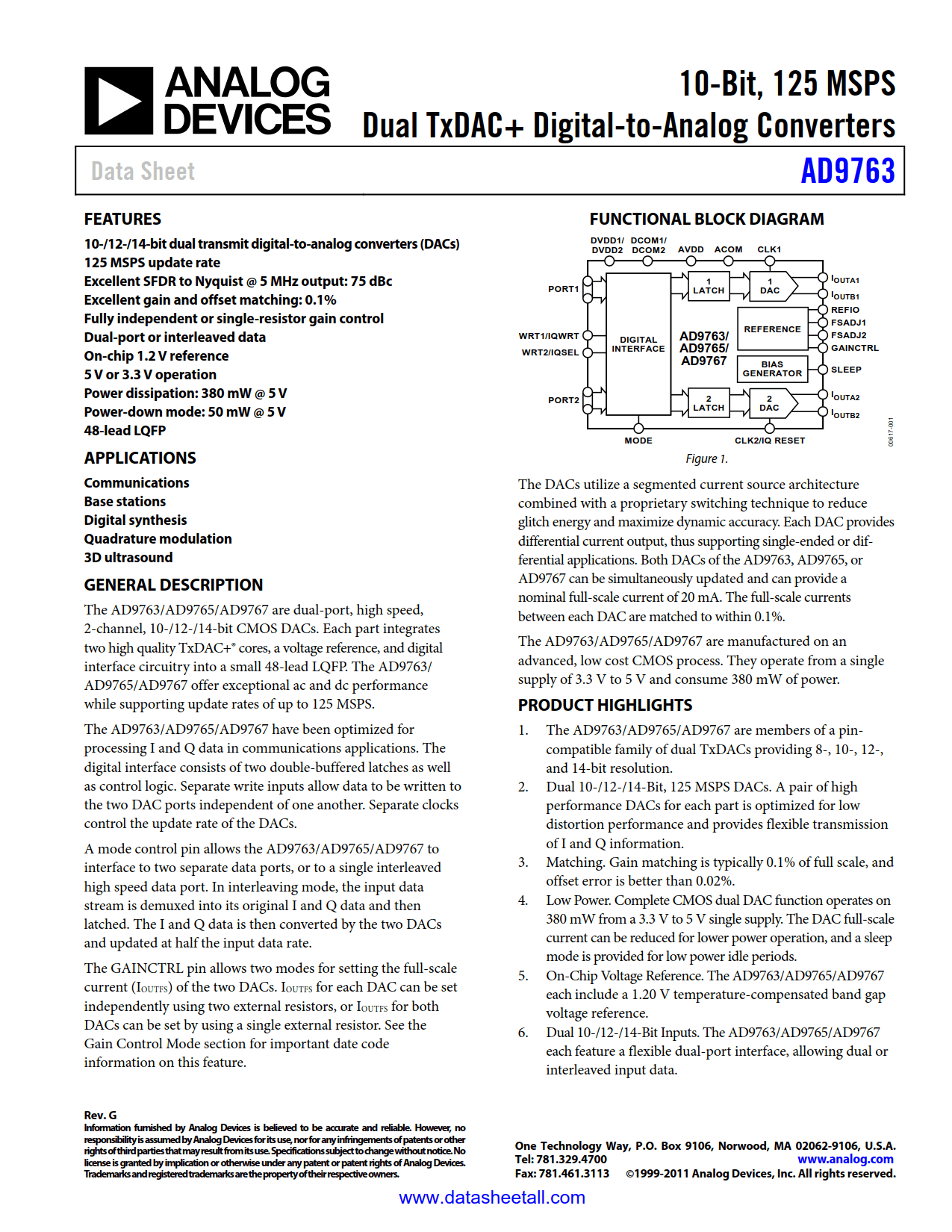

The AD9763 is dual-port, high speed, 2-channel, 10-bit CMOS DACs. Each part integrates two high quality TxDAC+® cores, a voltage reference, and digital interface circuitry into a small 48-lead LQFP. The AD9763 offer exceptional ac and dc performance while supporting update rates of up to 125 MSPS.

The AD9763 have been optimized for processing I and Q data in communications applications. The digital interface consists of two double-buffered latches as well as control logic. Separate write inputs allow data to be written to the two DAC ports independent of one another. Separate clocks control the update rate of the DACs.

A mode control pin allows the AD9763 to interface to two separate data ports, or to a single interleaved high speed data port. In interleaving mode, the input data stream is demuxed into its original I and Q data and then latched. The I and Q data is then converted by the two DACs and updated at half the input data rate.

The GAINCTRL pin allows two modes for setting the full-scale current (IOUTFS) of the two DACs. IOUTFS for each DAC can be set independently using two external resistors, or IOUTFS for both DACs can be set by using a single external resistor. See the Gain Control Mode section for important date code information on this feature.

The DACs utilize a segmented current source architecture combined with a proprietary switching technique to reduce glitch energy and maximize dynamic accuracy. Each DAC provides differential current output, thus supporting single-ended or differential applications. Both DACs of the AD9763 can be simultaneously updated and can provide a nominal full-scale current of 20 mA. The full-scale currents between each DAC are matched to within 0.1%.

The AD9763 is manufactured on an advanced, low cost CMOS process. They operate from a single supply of 3.3 V to 5 V and consume 380 mW of power.