| Part No.: | AD9629 |

| Page: | 32 Pages |

| Size: | 906 KB |

| Manufacturer: | Analog Devices, Inc. |

| Logo: |  |

| Views: | 1 |

| Update Time: | 2024-01-03 10:51:52 |

| DataSheet: | Download |

| Part No. | Packing | SPQ | Marking | MSL | Pins | Temp Range | Package Description | Buy |

| AD9629BCPZ-80 | Tray | 490 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | ||

| AD9629BCPZRL7-80 | Reel | 1500 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | ||

| AD9629BCPZ-65 | Tray | 490 | AD9629BCPZ-65 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | |

| AD9629BCPZRL7-65 | Reel | 1500 | AD9629BCPZ-65 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | |

| AD9629BCPZ-40 | Tray | 490 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | ||

| AD9629BCPZRL7-40 | Reel | 1500 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | ||

| AD9629BCPZ-20 | Tray | 490 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) | ||

| AD9629BCPZRL7-20 | Reel | 1500 | 3 | 32 | -40°C ~ 85°C | 32-Lead Lead Frame Chip Scale Package (LFCSP_WQ) |

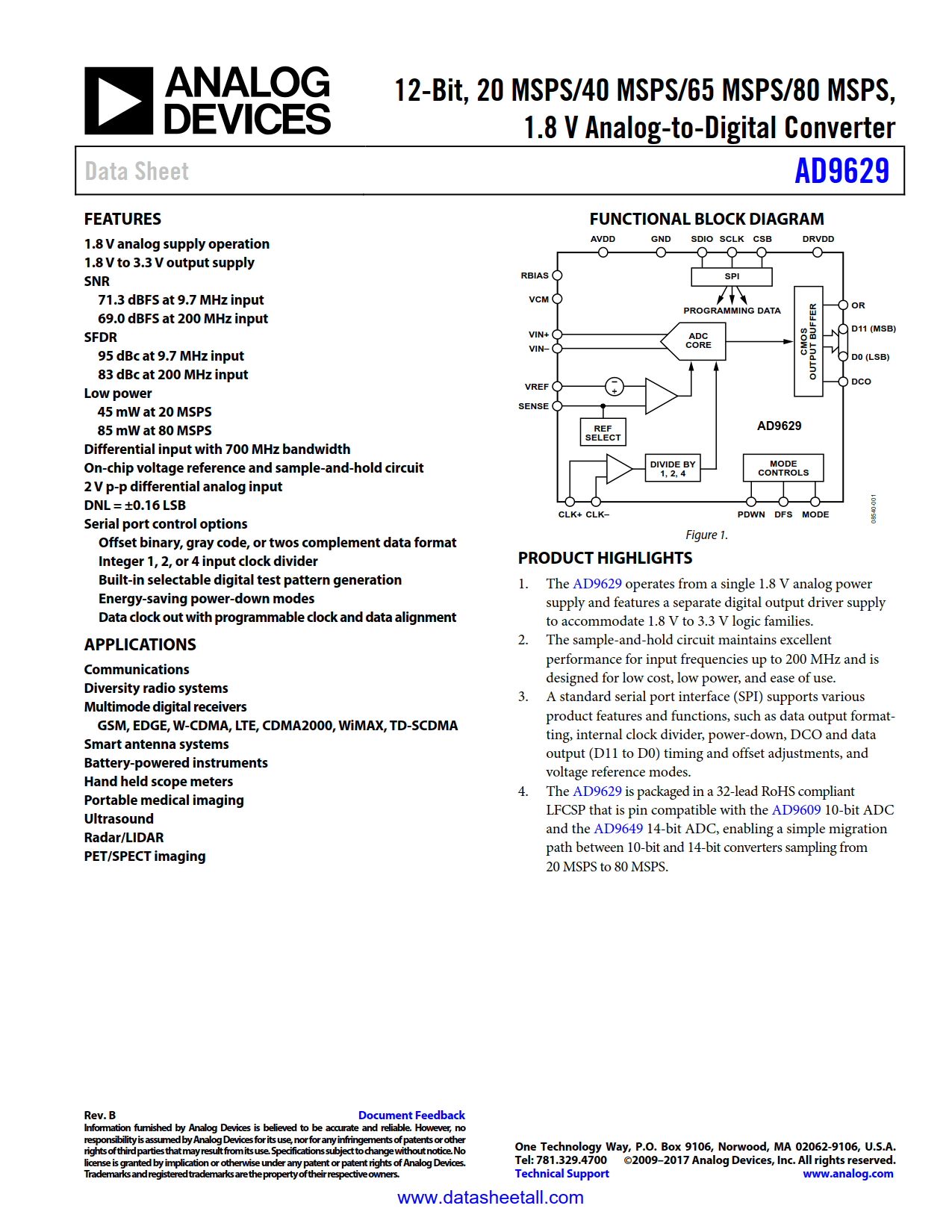

The AD9629 is a monolithic, single channel 1.8 V supply, 12-bit, 20 MSPS/40 MSPS/65MSPS/80 MSPS analog-to-digital converter (ADC). It features a high performance sample-and-hold circuit and on-chip voltage reference.

The product uses multistage differential pipeline architecture with output error correction logic to provide 12-bit accuracy at 80 MSPS data rates and to guarantee no missing codes over the full operating temperature range.

The ADC contains several features designed to maximize flexibility and minimize system cost, such as programmable clock and data alignment and programmable digital test pattern generation. The available digital test patterns include built-in deterministic and pseudorandom patterns, along with custom user-defined test patterns entered via the serial port interface (SPI).

A differential clock input with optional 1, 2, or 4 divide ratios controls all internal conversion cycles.

The digital output data is presented in offset binary, gray code, or twos complement format. A data output clock (DCO) is provided to ensure proper latch timing with receiving logic. Both 1.8 V and 3.3 V CMOS levels are supported.

The AD9629 is available in a 32-lead RoHS compliant LFCSP and is specified over the industrial temperature range (−40°C to +85°C).