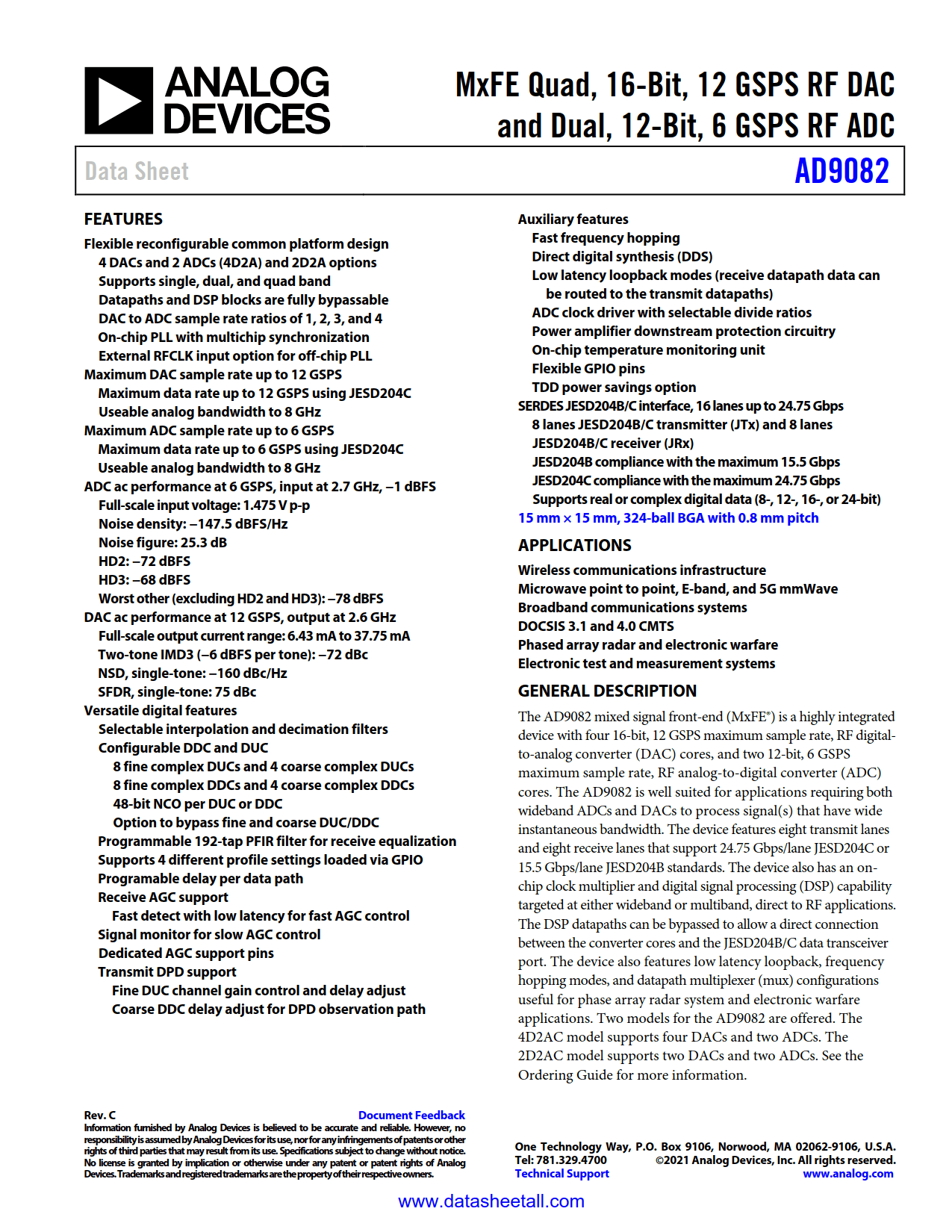

The AD9082 mixed signal front-end (MxFE

®) is a highly integrated device with a 16-bit, 12 GSPS maximum sample rate, RF digital-to-analog converter (DAC) core, and 12-bit, 6 GSPS maximum sample rate, RF analog-to-digital converter (ADC) cores. The AD9082 is well suited for applications requiring both wideband ADCs and DACs to process signal(s) having wide instantaneous bandwidth. The device features eight transmit lanes and eight receive lanes that support 24.75 Gbps/lane JESD204C or 15.5 Gbps/lane JESD204B standards. The device also has an on-chip clock multiplier and digital signal processing (DSP) capability targeted at either wideband or multiband, direct to RF applications. The DSP datapaths can be bypassed to allow a direct connection between the converter cores and the JESD204B/C data transceiver port. The device also features low latency loopback, frequency hopping modes, and datapath multiplexer (mux) configurations useful for phase array radar system and electronic warfare applications. Two models for the AD9082 are offered.

The 4D2AC model supports four DACs and two ADCs. The 2D2AC model supports two DACs and two ADCs.